PCB设计之如何去耦

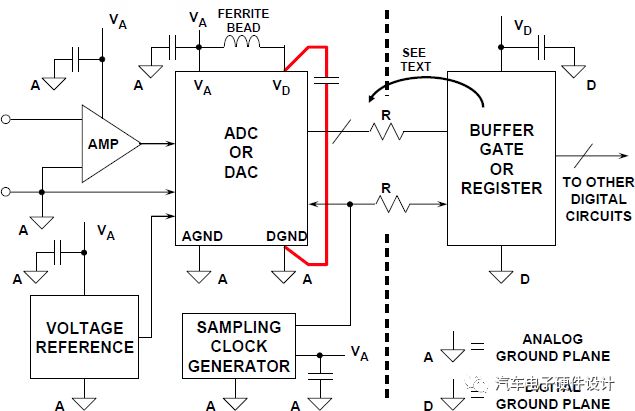

描述

局部的高频滤波器可以优化小小效果,去耦电容 可以减小回路电感

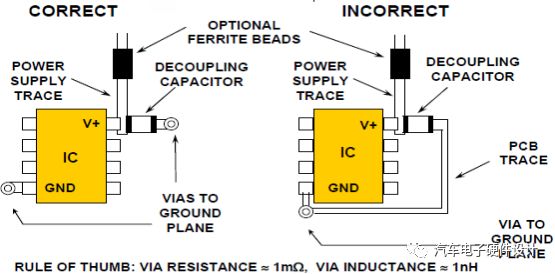

SOIC的去耦

经验法则

–Via resistance ≈ 1mΩ, Via inductance ≈1nH

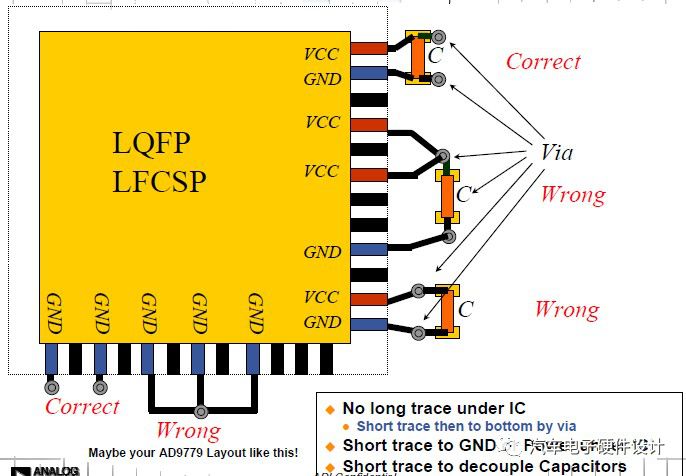

LQFP/LFCSP去耦

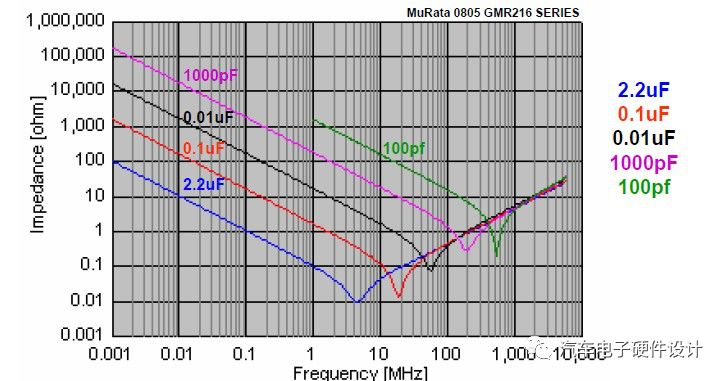

不同的去耦电容阻抗VS频率

并联电容可以在一个较宽的频带内降低阻抗

小的去耦电容尽可能靠近电源引脚

为什么每个电源引脚都需要去耦

去耦电容总结

旁路电容离电容引脚尽可能的近

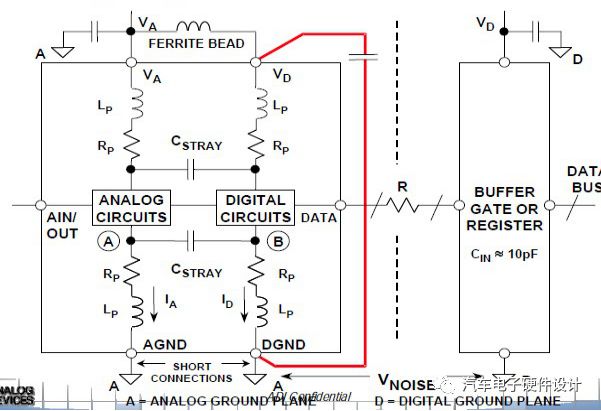

SMT磁珠对于降低Ripple非常有效

高频时需要地平面

最小化寄生参数

使用稳定高效的器件

较少的漂移和较低的ESR

完全精确的分析是比较困难的

为了优化结果可以使用一引起模型分析

使用一组并联的电容来去除较宽频带内的噪声

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PCB设计如何用电源去耦电容改善高速信号质量2025-05-19 570

-

详解去耦电容:去耦电容的PCB布局布线2024-03-27 7081

-

PCB去耦电容怎么放置?怎么选择去耦电容?2023-11-29 2206

-

PCB设计时处理去耦电容和旁路电容的注意事项2023-11-21 2323

-

去耦电容PCB设计和布局详解2023-07-05 2150

-

高速PCB设计指南之六.zip2022-12-30 529

-

什么是PCB中的板级去耦2022-02-10 1760

-

PCB的板级去耦设计方法2021-03-14 1323

-

PCB的板级去耦设计方法和实例讲解2021-02-19 1300

-

PCB设计之电容2019-08-13 3642

-

优秀的高速PCB设计之去耦电容2019-06-14 4940

-

PCB布线技巧之去耦电容的摆放2016-10-26 1370

-

高速PCB设计指南之八2009-11-11 629

-

高速PCB电源去耦设计指南2007-10-16 908

全部0条评论

快来发表一下你的评论吧 !