й«ҳйҖҹж”ҫеӨ§еҷЁжҢҜиҚЎзҡ„жңҖеёёи§ҒеҺҹеӣ зӣҳзӮ№ йҒҝе…ҚдҪ иө°жӣҙеӨҡзҡ„ејҜи·Ҝ

жЁЎжӢҹжҠҖжңҜ

жҸҸиҝ°

ж”ҫеӨ§еҷЁиў«з”ЁдәҺи®ёеӨҡдёҚеҗҢзҡ„еә”з”ЁдёӯпјҢе®ғ们еҸҜд»Ҙиў«з”ЁеҒҡй«ҳйҖҹжЁЎж•°иҪ¬жҚўеҷЁзҡ„иҫ“е…Ҙзј“еҶІеҷЁгҖҒеӨҡдёӘи§Ҷйў‘иҙҹиҪҪзҡ„й©ұеҠЁеҷЁе’ҢжөӢиҜ•д»ӘеҷЁеә”з”Ёдёӯзҡ„й«ҳйҖҹи„үеҶІдҝЎеҸ·ж”ҫеӨ§еҷЁзӯүгҖӮзӣ®еүҚпјҢеёӮеңәдёҠзҡ„еӨ§еӨҡж•°й«ҳйҖҹпјҲгҖӢ50MHzпјүж”ҫеӨ§еҷЁзҡ„дҪҝз”ЁйғҪйқһеёёж–№дҫҝпјҢдҪҶжҳҜеңЁйҖӮеҪ“зҡ„жғ…еҶөдёӢпјҢе®ғ们дјҡеҸҳжҲҗйқһеёёзЁіе®ҡзҡ„жҢҜиҚЎеҷЁгҖӮй«ҳйҖҹж”ҫеӨ§еҷЁжҢҜиҚЎзҡ„жңҖеёёи§ҒеҺҹеӣ еҰӮдёӢпјҡ

1. ж”ҫеӨ§еҷЁзҡ„иҫ“еҮәжңӘз»Ҹзј“еҶІиҖҢй©ұеҠЁе®№жҖ§иҙҹиҪҪпјӣ

2. з”өи·ҜжқҝеёғеұҖеј•е…Ҙзҡ„йҷ„еҠ з”өж„ҹжҲ–з”өе®№пјӣ

3. дёҚеҗҲйҖӮзҡ„з”өжәҗж—Ғи·Ҝпјӣ

4. дёҚйҒөе®Ҳж”ҫеӨ§еҷЁи®ҫ计规еҲҷгҖӮ

жң¬ж–Үе°ҶжӣҙдёәиҜҰз»Ҷең°и®Ёи®әиҝҷдәӣиҝқ规ж“ҚдҪңгҖӮйҒөеҫӘдёӢиҝ°йҖҡз”Ёзҡ„и®ҫи®ЎжҢҮеҚ—пјҢдҪ еңЁйҮҮз”Ёй«ҳйҖҹж”ҫеӨ§еҷЁиҝӣиЎҢи®ҫи®Ўзҡ„иҝҮзЁӢдёӯе°ҶйҒӯеҸ—иҫғе°‘зҡ„жҢ«жҠҳгҖӮ

й©ұеҠЁе®№жҖ§иҙҹиҪҪжҲ–з”өжҠ—жҖ§иҙҹиҪҪ

й©ұеҠЁе®№жҖ§иҙҹиҪҪеҸҜд»ҘзӣҙжҺҘеҮҸе°Ҹж”ҫеӨ§еҷЁзҡ„зӣёдҪҚиЈ•йҮҸгҖӮе®№жҖ§иҙҹиҪҪе’Ңж”ҫеӨ§еҷЁиҫ“еҮәйҳ»жҠ—еј•иө·зҡ„зӣёдҪҚж»һеҗҺе°ҶеҜјиҮҙж¬ йҳ»е°ји„үеҶІе“Қеә”жҲ–жҢҜиҚЎгҖӮдёҖдәӣж”ҫеӨ§еҷЁиғҪеӨҹзӣҙжҺҘй©ұеҠЁеӨ§зҡ„е®№жҖ§иҙҹиҪҪпјҢиҖҢеҸҰеӨ–дёҖдәӣж”ҫеӨ§еҷЁйңҖиҰҒдёҖдёӘдёІиҒ”з”өйҳ»жқҘзј“еҶІиҫ“еҮәзә§гҖӮиҰҒжҹҘйҳ…ж”ҫеӨ§еҷЁзҡ„ж•°жҚ®жүӢеҶҢд»ҘзЎ®е®ҡдҪ зҡ„ж”ҫеӨ§еҷЁеұһдәҺе“ӘдёҖзұ»гҖӮеҰӮеӣҫ1жүҖзӨәпјҢж”ҫеӨ§еҷЁиҫ“еҮәз«ҜдёҠзҡ„е°Ҹзҡ„дёІиҒ”з”өйҳ»пјҲRsпјүе°Ҷж”№е–„зЁіе®ҡжҖ§е’Ңе»әз«ӢжҖ§иғҪгҖӮ

еӣҫ1пјҡе®№жҖ§иҙҹиҪҪй©ұеҠЁз”өи·Ҝзҡ„е…ёеһӢжӢ“жңҙеӣҫ2пјҡз”өзјҶжҲ–дј иҫ“зәҝзҡ„й©ұеҠЁз”өи·Ҝ

дёҚдҪҝз”ЁдёІиҒ”з”өйҳ»жқҘй©ұеҠЁеҗҢиҪҙз”өзјҶд№ҹеҸҜиғҪеј•иө·йў‘зҺҮжҖҘеү§еўһеҠ жҲ–жҢҜиҚЎгҖӮеӣҫ2жҸҸиҝ°дәҶеҗҢиҪҙз”өзјҶй©ұеҠЁз”өи·Ҝзҡ„е…ёеһӢй…ҚзҪ®гҖӮ

з”өйҳ»Rsе’ҢRLйғҪзӯүдәҺз”өзјҶжҲ–дј иҫ“зәҝзҡ„зү№еҫҒйҳ»жҠ—ZoгҖӮж”ҫеӨ§еҷЁиҫ“еҮәйҳ»жҠ—йҡҸзқҖйў‘зҺҮзҡ„еўһеҠ иҖҢеўһеҠ гҖӮз”өе®№CеҸҜд»Ҙиў«з”ЁдәҺеңЁжӣҙеӨ§зҡ„йў‘зҺҮиҢғеӣҙеҶ…еҢ№й…Қз”өзјҶпјҢе®ғиЎҘеҒҝж”ҫеӨ§еҷЁдёҚж–ӯеўһеҠ зҡ„иҫ“еҮәйҳ»жҠ—гҖӮ

йҖҡз”Ёз”өи·Ҝжқҝи®ҫи®ЎжҢҮеҚ—

жҖ»дҪ“зҡ„з”өи·Ҝжқҝе’Ңз”өжәҗж—Ғи·Ҝзҡ„и®ҫи®ЎеңЁзЎ®дҝқй«ҳйў‘жҖ§иғҪдёӯеҸ‘жҢҘйҮҚиҰҒзҡ„дҪңз”ЁгҖӮй«ҳйҖҹж”ҫеӨ§еҷЁзҡ„жңҖж•Ҹж„ҹеј•и„ҡжҳҜеҸҚеҗ‘иҫ“е…Ҙз«Ҝе’Ңиҫ“еҮәеј•и„ҡгҖӮиҰҒйҒөеҫӘдёӢеҲ—жҖ»дҪ“и®ҫи®ЎжҢҮеҚ—пјҡ

1. иҰҒеҲ©з”Ёз”өи·ҜжқҝдёҠзҡ„жҺҘең°еұӮдёәе…ғеҷЁд»¶жҸҗдҫӣдёҖдёӘдҪҺз”өж„ҹеҖјзҡ„жҺҘең°иҝһжҺҘпјҢ然иҖҢпјҢиҰҒжҠҠй«ҳйҖҹж”ҫеӨ§еҷЁдёӢйқўе’Ңе‘Ёеӣҙзҡ„ең°е№ійқўеҺ»йҷӨпјҢзү№еҲ«жҳҜиҫ“е…Ҙе’Ңиҫ“еҮәеј•и„ҡйҷ„иҝ‘зҡ„ең°е№ійқўпјҢд»ҘеҮҸе°‘жқӮж•Јз”өе®№гҖӮ

2. е°ҪеҸҜиғҪдҪҝз”ЁиЎЁиҙҙе…ғеҷЁд»¶пјҢеӣ дёәе®ғ们жҸҗдҫӣдҪҺзҡ„еј•и„ҡз”өж„ҹгҖӮеҰӮжһңйҮҮз”Ёжңүеј•и„ҡзҡ„е…ғеҷЁд»¶пјҢе°ұиҰҒи®©еј•и„ҡжңҖзҹӯпјҢзү№еҲ«жҳҜжҠҠRfе’ҢRgжҺ§еҲ¶дёәжңҖе°ҸпјҢд»ҘеҮҸе°Ҹж”ҫеӨ§еҷЁеҸҚеҗ‘иҫ“е…Ҙз«Ҝзҡ„дёІиҒ”з”өж„ҹгҖӮ

3. иҰҒи®ҫи®Ўзҙ§еҮ‘зҡ„з”өи·Ҝжқҝ并жңҖе°ҸеҢ–жүҖжңүзҡ„еёғзәҝй•ҝеәҰпјҢзү№еҲ«жҳҜжңҖе°ҸеҢ–Rfе’ҢRgпјҢд»ҘеҮҸе°Ҹж”ҫеӨ§еҷЁеҸҚеҗ‘иҫ“е…Ҙз«Ҝзҡ„дёІиҒ”з”өж„ҹгҖӮ

4. дёҚиҰҒдҪҝз”ЁжҸ’еә§гҖӮжҠҠйҮҮз”ЁиЎЁйқўе°ҒиЈ…зҡ„ж”ҫеӨ§еҷЁзӣҙжҺҘз„ҠжҺҘеҲ°з”өи·ҜжқҝдёҠеҸҜд»ҘиҺ·еҫ—жңҖдҪізҡ„жҖ§иғҪгҖӮеҰӮжһңиҰҒз”ЁжҸ’еә§зҡ„иҜқпјҢз”Ёй—ӘеӯҳжҸ’еә§пјҲflash-mount socketпјүпјҢиҖҢдёҚиҰҒдҪҝз”ЁдҪ“з§Ҝй«ҳзҡ„жҸ’еә§гҖӮ

з”өжәҗж—Ғи·Ҝзҡ„йҖҡеёёеҒҡжі•

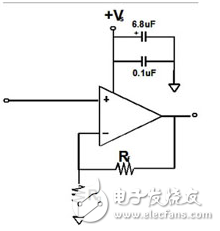

иҰҒеңЁжҜҸдёҖдёӘз”өжәҗдёҠйҮҮз”Ёж—Ғи·Ҝз”өе®№гҖӮж—Ғи·Ҝз”өе®№еңЁз”өжәҗеј•и„ҡдёҠжҸҗдҫӣдёҖжқЎдҪҺйҳ»жҠ—зҡ„з”өжөҒиҝ”еӣһи·Ҝеҫ„пјҢж”№е–„дәҶеҜ№з”өжәҗеҷӘеЈ°зҡ„жҠ‘еҲ¶пјҢ并ж»ӨйҷӨз”өжәҗиө°зәҝдёҠзҡ„й«ҳйў‘еҲҶйҮҸгҖӮиҰҒжҹҘйҳ…еҲ¶йҖ е•ҶжҸҗдҫӣзҡ„ж•°жҚ®жүӢеҶҢдёӯзҡ„жҺЁиҚҗе®№еҖјгҖӮеӨ§еӨҡж•°еҲ¶йҖ е•ҶжҺЁиҚҗйҮҮз”Ё6.8uFзҡ„й’Ҫз”өе®№е’Ң0.1uFзҡ„йҷ¶з“·з”өе®№гҖӮеңЁжҹҗдәӣжғ…еҶөдёӢпјҢеҮ дёӘж”ҫеӨ§еҷЁеҸҜд»Ҙе…ұдә«иҜҘй’Ҫз”өе®№гҖӮдҪҶжҳҜдёәдәҶдјҳеҢ–жҖ§иғҪпјҢзі»з»ҹдёӯзҡ„жҜҸдёҖдёӘж”ҫеӨ§еҷЁйғҪдҪҝз”ЁдёҖдёӘйҷ¶з“·з”өе®№гҖӮ

дёәдәҶе®һзҺ°жңҖдҪіжҖ§иғҪпјҢиҰҒжҢүз…§дёӢеҲ—иҰҒжұӮж”ҫзҪ®з”өе®№пјҡ

1. жҠҠ6.8uFз”өе®№ж”ҫзҪ®еңЁи·қзҰ»з”өжәҗеј•и„ҡ0.75иӢұеҜёзҡ„иҢғеӣҙеҶ…пјӣ

2. жҠҠ0.1uFз”өе®№ж”ҫзҪ®еңЁи·қзҰ»з”өжәҗеј•и„ҡ0.1иӢұеҜёзҡ„иҢғеӣҙеҶ…гҖӮ

жҠҠйҷ¶з“·з”өе®№ж”ҫзҪ®еңЁи·қзҰ»з”өжәҗеј•и„ҡ0.1иӢұеҜёзҡ„иҢғеӣҙеҶ…жҳҜиҮіе…ійҮҚиҰҒзҡ„гҖӮйҡҸзқҖи·қзҰ»зҡ„еўһеҠ пјҢеӣ еӯҳеңЁйҷ„еҠ иө°зәҝз”өж„ҹзҡ„зјҳж•…пјҢж—Ғи·Ҝз”өе®№зҡ„ж•ҲжһңдјҡдёӢйҷҚгҖӮеӣҫ3жҸҸз»ҳдәҶеҚ•з”өжәҗж”ҫеӨ§еҷЁзҡ„дҫӢеӯҗгҖӮеҰӮжһңйҮҮз”ЁеҸҢз”өжәҗдҫӣз”өпјҢйӮЈд№ҲеҸҰдёҖдёӘз”өжәҗиҰҒйҮҮз”ЁеҗҢж ·зҡ„ж—Ғи·Ҝз”өе®№гҖӮ

еӣҫ3пјҡеҚ•з”өжәҗж”ҫеӨ§еҷЁзҡ„еҹәжң¬ж”ҫеӨ§еҷЁжӯЈеҗ‘еўһзӣҠй…ҚзҪ®

еҹәжң¬ж”ҫеӨ§еҷЁи®ҫ计规еҲҷ

дёҖдәӣж”ҫеӨ§еҷЁе…·жңүжңҖе°ҸзЁіе®ҡеўһзӣҠиҰҒжұӮгҖӮеҰӮжһңж”ҫеӨ§еҷЁжүҖдҪҝз”Ёзҡ„еўһзӣҠдҪҺдәҺжҺЁиҚҗзҡ„жңҖе°ҸзЁіе®ҡеўһзӣҠпјҢе®ғе°ұеҸҜиғҪжҢҜиҚЎгҖӮиҖҢеҰӮжһңйҮҮз”Ёз”өжөҒеҸҚйҰҲж”ҫеӨ§еҷЁпјҡ1. ж №жҚ®дҪ зҡ„еўһзӣҠиҰҒжұӮпјҢйҮҮз”ЁеҲ¶йҖ е•ҶжҺЁиҚҗзҡ„еҸҚйҰҲз”өйҳ»еҖјпјӣ2. еңЁж”ҫеӨ§еҷЁзҡ„зӣҙжҺҘеҸҚйҰҲзҺҜи·ҜдёӯпјҢдёҚиҰҒдҪҝз”Ёз”өе®№жҲ–е…¶е®ғйқһзәҝжҖ§е…ғ件пјӣ3. еҜ№дәҺеҚ•дҪҚеўһзӣҠй…ҚзҪ®пјҢиҰҒдҪҝз”ЁеҸҚйҰҲз”өйҳ»пјӣдёҚдҪҝз”Ёж ҮеҮҶз”өеҺӢи·ҹйҡҸеҷЁз”өи·ҜгҖӮ

жң¬ж–Үе°Ҹз»“

еҪ“йҮҮз”Ёй«ҳйҖҹж”ҫеӨ§еҷЁиҝӣиЎҢи®ҫи®Ўж—¶пјҢиҰҒйҒөеҫӘдёӢеҲ—еҹәжң¬и®ҫи®ЎжҢҮеҚ—пјҡ

1. й©ұеҠЁе®№жҖ§иҙҹиҪҪж—¶пјҢйҮҮз”ЁдёІиҒ”з”өйҳ»пјӣ

2. з”өи·Ҝжқҝи®ҫи®ЎиҰҒйҮҮз”ЁжҺҘең°еұӮпјҢдҪҶжҳҜпјҢиҰҒж¶ҲйҷӨиҫ“е…Ҙ/иҫ“еҮәйҷ„иҝ‘зҡ„жҺҘең°е№ійқўпјҡ

3. ж¶ҲйҷӨй•ҝзҡ„еј•и„ҡжҲ–йҮҮз”ЁиЎЁиҙҙе…ғеҷЁд»¶пјӣ

4. ж¶ҲйҷӨI/Oз«Ҝйҷ„иҝ‘зҡ„д»»дҪ•еҜ„з”ҹз”өе®№жҲ–з”өж„ҹпјӣ

5. еңЁжҜҸдёҖдёӘз”өжәҗеј•и„ҡдёҠдҪҝз”Ёз”өжәҗж—Ғи·Ҝз”өе®№пјӣ

6. е°ҪеҸҜиғҪжҠҠж—Ғи·Ҝз”өе®№йқ иҝ‘ж”ҫеӨ§еҷЁзҡ„з”өжәҗеј•и„ҡж”ҫзҪ®пјӣ

7. жҹҘйҳ…еҲ¶йҖ е•ҶжҸҗдҫӣзҡ„ж•°жҚ®жүӢеҶҢпјӣ

8. зЎ®дҝқдёҚиҝқеҸҚж”ҫеӨ§еҷЁзҡ„жңҖе°ҸзЁіе®ҡеўһзӣҠпјӣ

9 гҖӮеҜ№дәҺз”өжөҒеҸҚйҰҲж”ҫеӨ§еҷЁпјҡйҮҮз”ЁжҺЁиҚҗзҡ„еҸҚйҰҲз”өйҳ»гҖӮеңЁеҸҚйҰҲзҺҜи·ҜдёӯпјҢдёҚиҰҒйҮҮз”Ёз”өе®№жҲ–дәҢжһҒз®ЎпјҢйҷӨйқһйҮҮеҸ–дәҶзү№еҲ«жҺӘж–ҪжқҘзЎ®дҝқзЁіе®ҡжҖ§гҖӮ

- зӣёе…іжҺЁиҚҗ

- зғӯзӮ№жҺЁиҚҗ

- ж

-

и®ҫи®Ўж”ҫеӨ§еҷЁж—¶пјҢжҢҜиҚЎеёёи§ҒеҺҹеӣ д»ҘеҸҠиЎҘж•‘ж–№жі•2018-03-19 18806

-

иҝҗз®—ж”ҫеӨ§еҷЁдјҡеҸ‘з”ҹжҢҜиҚЎзҡ„дёӨз§Қеёёи§ҒеҺҹеӣ жө…жһҗ2018-09-26 5046

-

иҝҗз®—ж”ҫеӨ§еҷЁеҸ‘з”ҹжҢҜиҚЎзҡ„дёӨз§Қеёёи§ҒеҺҹеӣ жө…жһҗ2018-10-22 1885

-

ж”ҫеӨ§еҷЁжҢҜиҚЎзҡ„еёёи§ҒеҺҹеӣ д»ҘеҸҠиЎҘж•‘ж–№жі•2019-01-04 2262

-

иҝҗз®—ж”ҫеӨ§еҷЁзҡ„жҢҜиҚЎ2019-07-18 2285

-

еӨ§зҘһжҖ»з»“пјҡй«ҳйҖҹж”ҫеӨ§еҷЁи®ҫи®Ўзҡ„еёёи§Ғй—®йўҳдёҺи§ЈеҶіж–№жі•2020-10-11 3498

-

еҜјиҮҙеҸҚйҰҲж”ҫеӨ§еҷЁжҢҜиҚЎзҡ„еҺҹеӣ жҳҜд»Җд№Ҳпјҹ2021-04-07 1747

-

иҜ·й—®д»ӘиЎЁж”ҫеӨ§еҷЁиғҪеҗҰйҒҝе…Қеёёи§Ғзҡ„и®ҫи®Ўйҷ·йҳұпјҹ2021-04-13 1043

-

йҒҝе…Қж”ҫеӨ§еҷЁз”өи·Ҝи®ҫи®Ўдёӯзҡ„еёёи§Ғй—®йўҳ2010-05-11 541

-

ж”ҫеӨ§еҷЁдјҡеҸ‘з”ҹжҢҜиҚЎдёӨз§Қеёёи§ҒеҺҹеӣ жө…жһҗ2017-03-05 676

-

жҠҖжңҜ | ж”ҫеӨ§еҷЁз”өи·Ҝи®ҫи®Ў:еҰӮдҪ•йҒҝе…Қеёёи§Ғй—®йўҳ?2019-06-22 5072

-

AN-937: ж”ҫеӨ§еҷЁз”өи·Ҝи®ҫи®ЎпјҡеҰӮдҪ•йҒҝе…Қеёёи§Ғй—®йўҳ2021-03-20 1040

-

еј•иө·ж”ҫеӨ§еҷЁжҢҜиҚЎзҡ„еҺҹеӣ жҳҜд»Җд№ҲпјҢеҰӮдҪ•и§ЈеҶіпјҹ2021-05-01 20396

-

AN148-дҪ зҡ„иҝҗз®—ж”ҫеӨ§еҷЁжҢҜиҚЎеҗ—пјҹ2021-05-24 795

-

ж”ҫеӨ§еҷЁз”өи·Ҝи®ҫи®Ў:еҰӮдҪ•йҒҝе…Қеёёи§Ғй—®йўҳ2023-11-22 411

е…ЁйғЁ0жқЎиҜ„и®ә

еҝ«жқҘеҸ‘иЎЁдёҖдёӢдҪ зҡ„иҜ„и®әеҗ§ !