DSP系统的电磁兼容和抗干扰设计

EMC/EMI设计

描述

0 引言

印制线路板(PCB)提供电路元件和器件之间的电气连接,是各种电子设备最基本的组成部分,它的性能直接关系到电子设备质量的好坏。随着电子技术的发展,各种电子产品经常在一起工作,它们之间的干扰越来越严重,所以电磁兼容问题成为一个电子系统能否正常工作的关键。同样,随着PCB的密度越来越高,PCB设计的好坏对电路的干扰及抗干扰能力影响很大。要使电子电路获得最佳性能,除了元器件的选择和电路设计之外,良好的PCB布线在电磁兼容性中也是一个非常重要的因素。

随着高速DSP技术的广泛应用,相应的高速DSP的PCB设计就显得十分重要。由于DSP是一个相当复杂、种类繁多并有许多分系统的数、模混合系统,所以来自外部的电磁辐射以及内部元器件之间、分系统之间和各传输通道间的串扰对DSP及其数据信息所产生的干扰,已严重地威胁着其工作的稳定性、可靠性和安全性。据统计,干扰引起的DSP事故占其总事故的90%左右。因此设计一个稳定、可靠的DSP系统,电磁兼容和抗干扰至关重要。

1 DSP的电磁干扰环境

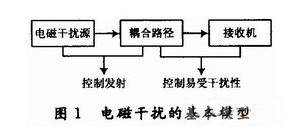

电磁干扰的基本模型由电磁干扰源、耦合路径和接收机3部分组成,如图1所示。

电磁干扰源包含微处理器、微控制器、静电放电、瞬时功率执行元件等。随着大量高速半导体器件的应用,其边沿跳变速率非常快,这种电路可以产生高达300 MHz的谐波干扰。耦合路径可以分为空间辐射电磁波和导线传导的电压与电流。噪声被耦合到电路中的最简单方式是通过导体的传递,例如,有一条导线在一个有噪声的环境中经过,这条导线通过感应接收这个噪声并且将其传递到电路的其他部分,所有的电子电路都可以接收传送的电磁干扰。例如,在数字电路中,临界信号最容易受到电磁干扰的影响;模拟的低级放大器、控制电路和电源调整电路也容易受到噪声的影响。

2 DSP电路板的布线和设计

良好的电路板布线在电磁兼容性中是一个非常重要的因素,一个拙劣的电路板布线和设计会产生很多电磁兼容问题,即使加上滤波器和其他元器件也不能解决这些问题。

正确的电路布线和设计应该达到如下3点要求:

(1)电路板上的各部分电路之间存在干扰,电路仍能正常工作;

(2)电路板对外的传导发射和辐射发射尽可能低,达到有关标准要求;

(3)外部的传导干扰和辐射干扰对电路板上的电路没有影响。

2.1 元器件的布置

(1)元器件布置的首要问题是对元器件进行分组。元器件的分组原则有:按电压不同分;按数字电路和模拟电路分;按高速和低速信号分和按电流大小分。一般情况下都按照电压不同分或按数字电路与模拟电路分。

(2)所有的连接器都放在电路板的一侧,尽量避免从两侧引出电缆。

(3)避免让高速信号线靠近连接器。

(4)在元器件安排时应考虑尽可能缩短高速信号线,如时钟线、数据线和地址线等。

2.2 地线和电源线的布置

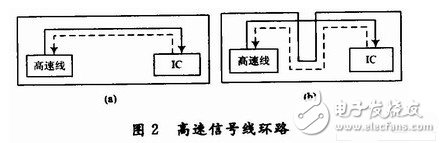

地线布置的最终目的是为了最小化接地阻抗,以此减小从电路返回到电源之间的接地回路电势,即减小电路从源端到目的端线路和地层形成的环路面积。通常增加环路面积是由于地层隔缝引起的。如果地层上有缝隙,高速信号线的回流线就被迫要绕过隔缝,从而增大了高频环路的面积,如图2所示。

图2中高速线与芯片之间进行信号传输。图2(a)中没有地层隔缝,根据“电流总是走阻抗最小的途径”,此时环路面积最小。图2(b)中,有地层隔缝,此时地环路面积增大,这样就产生如下后果:

(1)增大向空间的辐射干扰,同时易受空间磁场的影响;

(2)加大与板上其他电路产生磁场耦合的可能性;

(3)由于环路电感加大,通过高速线输出的信号容易产生振荡;

(4)环路电感上的高频压降构成共模辐射源,并通过外接电缆产生共模辐射。

通常地层上的隔缝不是在分地时、有意识地加上的,有时隔缝是因为板上的过孔过于接近而产生的,因此在PCB设计中应尽量避免该种情况发生。

电源线的布置要和地线结合起来考虑,以便构成特性阻抗尽可能小的供电线路。为了减小供电用线的特性阻抗,电源线和地线应该尽可能的粗,并且相互靠近,使供电回路面积减到最小,而且不同的供电环路不要相互重叠。在集成芯片的电源脚和地脚之间要加高频去耦电容,容量为0.01~0.1μF,而且为了进一步提高电源的去耦滤波的低频特性,在电源引入端要加上1个高频去耦电容和1个1~10μF的低频滤波电容。

在多层电路板中,电源层和地层要放置在相邻的层中,从而在整个电路板上产生一个大的PCB电容消除噪声。速度最快的关键信号和集成芯片应当布放在临近地层一边,非关键信号则布放在靠近电源层一边。因为地层本身就是用来吸收和消除噪声的,其本身几乎是没有噪声的。

2.3 信号线的布置

不相容的信号线之间能产生耦合干扰,所以在信号线的布置上要把它们隔离,隔离时采取的措施有:

(1)不相容信号线应相互远离,不要平行,分布在不同层上的信号线走向应相互垂直,这样可以减少线间的电场和磁场耦合干扰;

(2)高速信号线特别是时钟线要尽可能的短,必要时可在高速信号线两边加隔离地线;

(3)信号线的布置最好根据信号流向顺序安排,一个电路的输入信号线不要再折回输入信号线区域,因为输入线与输出线通常是不相容的。

当高速数字信号的传输延时时间Td》Tr(Tr为信号的脉冲上升时间)时,应考虑阻抗匹配问题。因为错误的终端阻抗匹配将会引起信号反馈和阻尼振荡。通常线路终端阻抗匹配的方法有串联源端接法、并联端接法、RC端接法、Thevenin端接法4种。

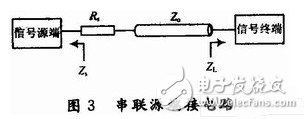

(1)串联源端接法

图3为串联源端接电路。

源端阻抗Zs和分布在传输线上的阻抗Zo之间,加上源端接电阻Rs,用来完成阻抗匹配,Rs还能吸收负载的反馈。这里的Rs必须离源端尽可能的近,理论上应为Rs=Zo-Zs中的实数值。一般Rs取15~75Ω。

(2)并联端接法

图4为并联端接电路。附加1个并联端电阻Rp,这样Rp与ZL并联后就与Zo相匹配。这个方法需要源驱动电路来驱动一个较高的电流,能耗很高,所以在功耗小的系统中不适用。

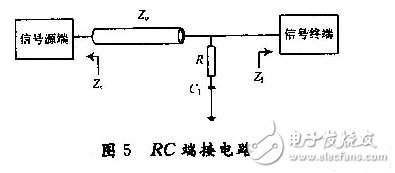

(3)RC端接法

图5为RC端接电路。该方法类似于并联端接电路,但引入了电容C1,此时R用于提供匹配Zo的阻抗。C1为R提供驱动电流并过滤掉从传输线到地的射频能量。因此与并联端接方法相比,RC端接电路需要的源驱动电流更少。R和C1的值由Zo,Tpd(环路传输延迟)和终端负载电容值Cd决定。时间为常数,RC=3Tpd,其中R∥ZL=Zo,C=C1∥Cd。

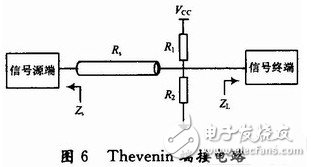

(4)Thevenin端接法

图6为Thevenin端接电路。该电路由上拉电阻R1和下拉电阻R2组成,这样就使逻辑高和逻辑低与目标负载相符。其中,R1和R2的值由R1∥R2=Zo决定,R1+R2+ZL的值要保证最大电流不能超过驱动电路容量。

3 结语

本文通过对电子产品电磁环境的分析,确定高速DSP系统中产生干扰的主要原因,并针对这些原因,通过对高速DSP系统的多层板布局、器件布局以及PCB布线等方面进行分析,给出有效降低DSP系统的干扰、提高电磁兼容性能的措施。从设计层次保证了高速DSP系统的有效性和可靠性。合理布局设计,减少噪声,降低干扰,避开不必要的失误,对系统性能的发挥起到不可低估的作用。

-

为什么接地可以抗干扰?详解电磁兼容与抗干扰技术2020-09-01 23347

-

单片机系统设计中硬件如何提高抗干扰能力和电磁兼容性?2018-07-13 1844

-

DSP系统中的电磁兼容探讨2019-07-25 2022

-

电磁干扰与电磁兼容技术2009-10-06 1244

-

抗干扰能力和电磁兼容性的解决方法讲解2007-10-16 2406

-

如何提高电子产品的抗干扰能力和电磁兼容性2010-02-06 2227

-

DSP应用系统电磁兼容的设计2011-10-20 1230

-

如何提高抗干扰能力和电磁兼容性2017-02-10 1744

-

高速DSP系统电磁兼容性解析2017-10-21 756

-

高速DSP系统的电路板级电磁兼容性设计2017-12-02 439

-

分析高速DSP系统中产生干扰的原因及如何解决2018-10-02 8526

-

电磁兼容与抗干扰的详解为什么接地可以抗干扰2020-11-24 2003

-

提高电子产品的抗干扰能力和电磁兼容性的方法2021-06-24 1249

-

GB/T 17626.1-2006电磁兼容试验和测量技术抗干扰度试验2022-08-17 1212

-

电磁兼容与电磁干扰快速评估系统2025-02-14 783

全部0条评论

快来发表一下你的评论吧 !