用于MCU和FPGA的LED图文显示屏控制系统现

移动通信

描述

关键词: FPGA , LED图文 , MCU , 显示屏

引言

2012-3-22 14:49:58 上传

目前,市场上的中小规模LED显示系统,一般采用传统的单片机作为主控芯片。对LED大屏幕显示屏来说,由于数据传输量大,要求扫描速度快,而单片机内部的资源较少、运行速度较慢,难于满足系统要求。以FPGA作为控制器,一方面,FPGA采用软件编程实现硬件功能,速度较快;另一方面,它的引脚资源丰富,可扩展性强。因此,用单片FPGA和简单的外围电路就可以实现大屏幕LED显示屏的控制,无需另外设计汉字库,具有集成度高、稳定性好、设计灵活和效率高等优点。

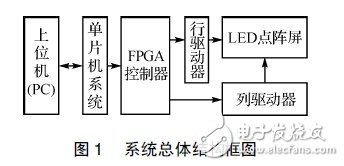

1 系统总体结构

LED大屏幕显示系统由上位机(PC机)、单片机系统、FPGA控制器、LED显示屏的行列驱动电路等模块组成,如图1所示。上位机负责汉字、字符等数据的采集与发送。单片机系统与上位机之间以异步串行通信工作方式,通过串行端口从上位机获得已完成格式转换的待显示的图形点阵数据,并将其存入EEPROM存储器。之后通过FPGA控制器,将存储器的显示数据还原到LED显示屏。扫描控制电路采用可编程逻辑芯片CyclONeEP1C6,利用VHDL语言编程实现,采用1/16扫描方式,刷新频率在60Hz以上。本文着重介绍2561024的单色图文显示屏的FPGA控制模块。

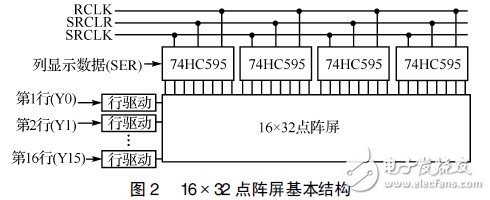

对大屏幕LED显示屏来说,列显示数据通常采用的是串行传输方式,行采用1/16的扫描方式。图2为1632点阵屏单元模块的基本结构,列驱动电路采用4个74HC595级联而成。在移位脉冲SRCLK的作用下,串行数据从74HC595的数据端口SER一位一位地输入,当一行的所有32列数据传送完后,输出锁存信号RCLK并选通行信号Y0,则第1行的各列数据就可按要求显示。

2012-3-22 14:49:58 上传

下载附件 (29.24 KB) 按同样的方法显示其余各行,当16行数据扫描一遍(即完成一个周期)后,再从第1行开始下一个周期的扫描。只要扫描的周期小于20ms,显示屏就不闪烁。2561024大屏幕显示屏由1632个的1632点阵屏级联而成。为了缩短控制系统到屏体的信号传输时间,将显示数据分为16个区,每个区由161024点阵组成,每行数据为1024/8=128字节,显示屏的像素信号由LED显示屏的右侧向左侧传输移位,把16个分区的数据存在同一块存储器。一屏的显示数据为32KB,要准确读出16个分区的数据,其存储器的读地址由16位组成,由于数据只有32KB,因此最高可置为0。其余15位地址从高到低依次为:行地址(4位)、列地址(7位)、分区地址(4位)。4位分区地址的译码信号(Y0~Y15)作为锁存器的锁存脉冲,在16个读地址发生周期内,依次将第1~16分区的第1字节数据锁存到相应的锁存器,然后在移位锁存信号上升沿将该16字节数据同时锁存入16个8位并转串移位寄存器组中。在下一个16个读地址发生时钟周期,一方面,并转串移位寄存器将8位数据移位串行输出,移位时钟为读地址发生时钟的二分频;另一方面,依次将16个分区的第2字节数据读出并锁入相应的锁存器,按照这种规律将所有分区的第一行数据依次全部读出后,在数据有效脉冲信号的上升沿将所有串行移位数据输出,驱动LED显示。接下来,移位输出第2行的数据,在此期间第1行保持显示;第2行全部移入后,驱动第2行显示,同时移入第3行按照这种各分区分行扫描的方式完成整个LED大屏幕的扫描显示。

3 基于FPGA显示屏控制器的设计

3.1 FPGA控制模块总体方案

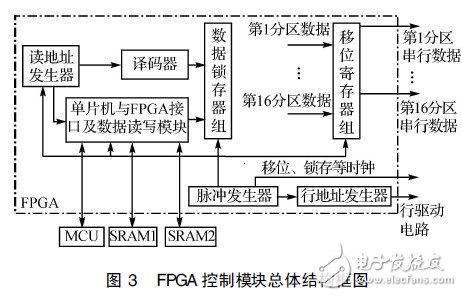

如图3所示,FPGA控制模块主要由单片机与FPGA接口及数据读写模块、读地址发生器、译码器、行地址发生器、数据锁存器组、移位寄存器组、脉冲发生器等模块组成。

2012-3-22 14:49:58 上传

下载附件 (43.38 KB) 读地址发生器主要产生读地址信号,地址信号送往MCU接口及数据读写模块,读取外部SRAM1或SRAM2中已处理好的LED显示屏数据,并把数据按分区方式送到数据锁存器组锁存。锁存器输出16分区数据,通过移位寄存器组实现并串转换得到显示屏所需要的串行数据,并送往LED显示屏列驱动电路。脉冲发生器为各模块提供相应的同步时钟,行地址发生器产生相应的行信号送往显示屏的行驱动电路。3.2 单片机与FPGA接口及数据读写模块

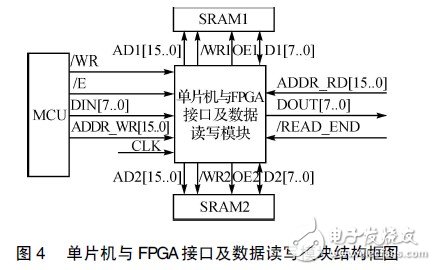

单片机与FPGA接口及数据读写模块结构如图4所示。单片机从EEPROM中读取数据并根据显示要求进行处理后,通过接口及数据读写模块把数据送往数据缓冲器SRAM1或SRAM2。为提高数据的传输速度,保证显示效果的连续性,在系统中采用双体切换技术来完成数据存储过程。也就是说,采用双SRAM存储结构,两套完全独立的读、写地址线和数据线轮流切换进行读写。工作时,FPGA在一个特定的时间只从两块SRAM中的一块读取显示的数据进行显示,同时另外一块SRAM与MCU进行数据交换。MCU会写入新的数据,依次交替工作,可实现左移、上移、双屏等显示模式。如果显示的内容不改变,即一块SRAM里的数据不变时,MCU不需要给另外一块SRAM写数据。

2012-3-22 14:49:58 上传

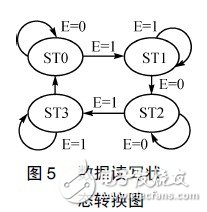

下载附件 (31.02 KB) 该模块采用VHDL有限状态机来实现,整个控制分为4个状态,其状态转换图如图5所示。其工作过程如下:系统开机进入初始状态ST0,单片机的写入使能端E为低电平,单片机从EEPROM中读取数据并把数据写入到SRAM1,同时FPGA读取SRAM2中的数据;当单片机数据写完一屏数据后E变为高电平,当FPGA从SRAM2中读完数据、结束信号READ_END为低电平时,进入ST1状态。

2012-3-22 14:49:58 上传

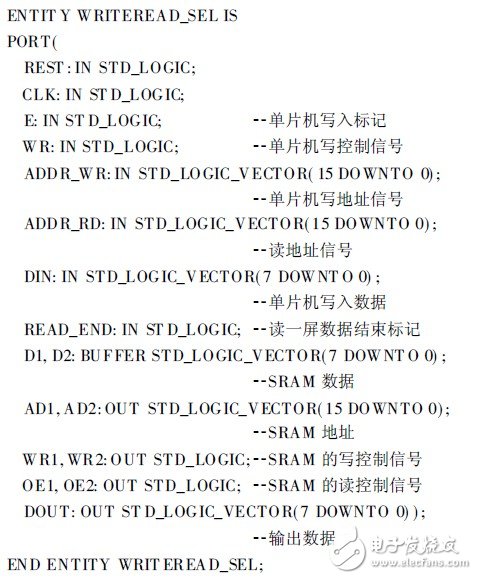

下载附件 (14.21 KB) 在ST1状态下,若没有新的数据写入则E保持高电平,FPGA读取SRAM1的数据,为静态显示;只有当单片机的读入控制信号E为低电平且READ_END为低电平时,进入ST2状态。在ST2状态下,单片机把数据写入SRAM2,同时FPGA读取SRAM1的数据,单片机数据写完后E变为高电平,当FPGA一屏数据读完后READ_END为低电平,进入ST3状态。在ST3状态下,如果没有新数据写入E为高电平,FPGA读取SRAM2中的数据。当单片机有新的数据写入时E变为低电平,当FPGA一屏数据读完后READ_END为低电平时,重新进入ST0状态。通过这种周而复始的交替工作完成数据的写入与读取,其端口程序如下:

2012-3-22 14:49:58 上传

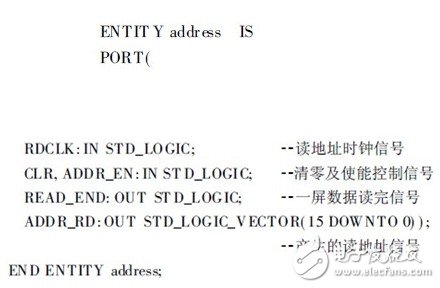

下载附件 (85.25 KB)3.3 读地址发生器

读地址发生器主要产生外部缓存器SRAM1(SRAM2)的读地址信号,使系统能正确地从存储器中读取相应的显示数据。其地址最高位为0,其余地址分别为行地址(hang[30])、列地址(lie[60])、分区地址(qu[30])15位有效地址信号。在16个脉冲周期内读出在SRAM1(SRAM2)中的16字节数据,其部分VHDL源程序如下:

2012-3-22 14:49:58 上传

下载附件 (25.4 KB)3.4 译码器

译码器模块主要是产生16路的分区信号(低电平有效)分别控制16个锁存器,把16个分区的显示数据分别锁存在相应的锁存器中。

3.5 数据锁存器组及移位寄存器组模块

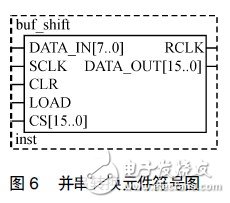

数据锁存器组模块由16个8位锁存器组成锁存器组,锁存16个分区的数据。移位寄存器组模块由16个8位移位寄存器组成,把各路锁存器中8位并行数据转换成同时输出的16路串行数据,驱动LED显示屏,实现数据的并串转换。

其生成的元件符号如图6所示。其中,DATA_IN[7.0]为每个分区的8位并行数据输入,SCLK为移位时钟,CLR为清零信号,LOAD为数据锁存信号,CS[150]为16分区的输入信号(接译码器的输出),DATA_OUT[150]为16路的串行数据输出。

2012-3-22 14:49:58 上传

下载附件 (15.78 KB)3.6 脉冲发生器

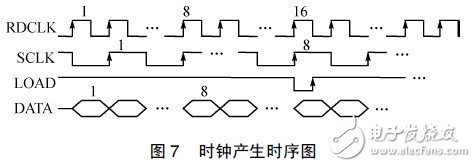

系统采用1/16的扫描方式,把数据分为16分区,16分区数据同时传送。假设刷新的频率为60Hz(即周期为16.67ms),每一行显示的时间约为16.67ms/16=1.04ms。每行有1024位,则移位脉冲周期为1.04/1024=102s,即移位频率为0.983MHz以上才能满足要求。

由于移位脉冲是数据读取模块时钟的2分频,因此系统的时钟至少1.97MHz以上,本系统采用50MHz时钟源。

其时序图如图7所示。

2012-3-22 14:49:58 上传

下载附件 (16.89 KB)其中,RDCLK为FPGA读取数据时钟;SCLK是串行输出的移位时钟,是RDCLK的2分频;LOAD是数据锁存信号,每次读完16个分区中的某个字节数据DATA后产生锁存信号,数据锁存在数据锁存器组中,其时钟是RDCLK的16分频。

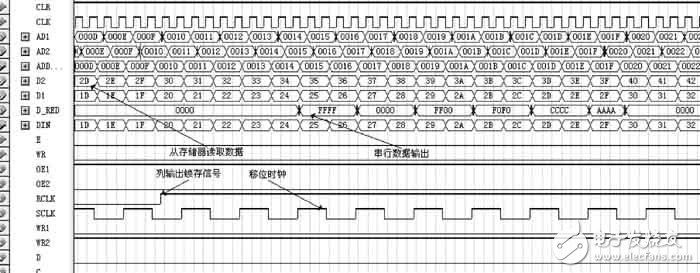

4 FPGA控制模块的仿真测试

在QuartusII5.1中建立一个工程,并建立原理图文件,把单片机与FPGA接口及数据读写模块、读地址发生器、译码器、行地址发生器、数据锁存器、移位寄存器、脉冲发生器等单元模块所生的模块元件符号连接起来,构成总控制模块逻辑图并对其功能仿真。仿真结果如图8所示,从存储器中读取16字节数据,经并串转换输出16路的串行数据。从波形图分析,功能正确,且各输出端口信号均符合时序要求。

2012-3-22 14:49:58 上传

下载附件 (53.08 KB) 5 结语FPGA是在线可编程芯片,可以根据不同的用户要求进行不同的编程,缩短了系统的开发周期并节约了硬件的开发成本。本文以FPGA为主芯片,较完整地设计了大屏幕LED单色图文显示屏控制系统。随着LED显示屏技术的发展,FPGA与ARM或DSP等芯片的组合,必将在双色显示屏和彩色显示屏领域获得广泛的应用。

来源:电子工程网

- 相关推荐

- 热点推荐

-

Led显示屏控制系统怎么使用 led显示屏控制器怎么设置2024-02-03 13703

-

浅谈LED显示屏控制系统2023-07-24 4021

-

LED大屏幕显示屏的控制系统设计2020-01-18 3654

-

基于FPGA的大屏幕LED单色图文显示屏控制系统设计2019-07-16 2662

-

如何使用FPGA和MCU进行大型LED显示屏系统设计2018-12-25 1906

-

基于LED图文显示屏控制系统的设计2018-10-23 6793

-

led显示屏控制软件有哪些_九个led显示屏控制软件介绍2018-03-21 211825

-

LED显示屏控制系统的设计与整体分析2017-11-03 1625

-

LED显示屏控制系统与控制卡2016-07-22 6940

-

基于FPGA的大型LED显示屏系统设计2011-11-16 3065

-

基于MCU和FPGA的LED图文显示屏控制系统2011-08-19 5653

-

DBA-5.0B系列嵌入式LED图文显示屏控制器使用手册2011-04-17 977

-

点阵LED显示屏控制系统2009-08-04 1301

全部0条评论

快来发表一下你的评论吧 !