BJ-EPM240学习板介绍

电子说

描述

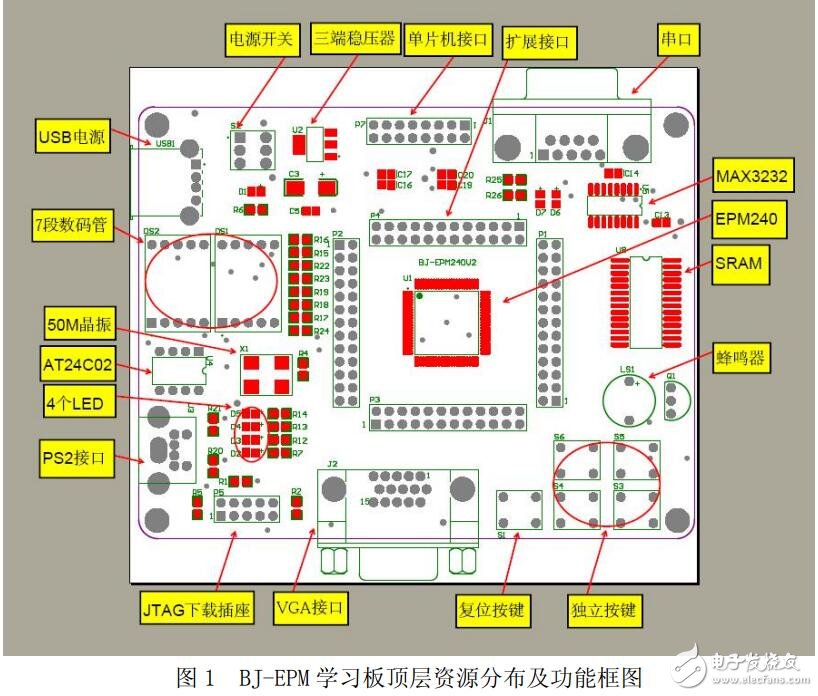

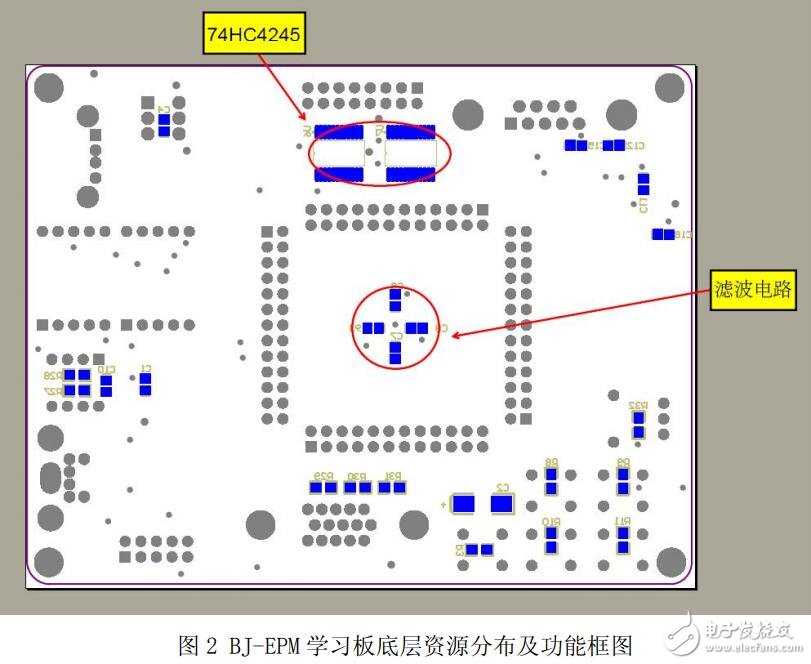

1.BJ-EPM240学习板功能框图

图1和图2是整板系统的功能框图,从图中可以清楚地看到EPM240T100学习板上丰富的外设资源及其位置分布情况。

2.BJ-EPM240学习板基本配置

主芯片使用的是Altera公司的MAXII系列EPM240T100C5,该芯片有240个逻辑单元,等效宏单元192个,资源比较丰富,内有8KbitFlash的存储空间。

50MHz有源晶振,作为系统主时钟。

低电平复位按键,使用EPM240的全局复位管脚。

8色VGA接口1个,让大家掌握电脑显示器的驱动原理。

RS232串口1个,通过串口调试助手轻松实现UART通信协议。

PS/2接口1个,实现键盘解码,配合串口调试助手在PC机上显示键值。

70ns快速读写的SRAM芯片IS62LV256-70U,具有32KB存储空间,让大家熟悉SRAM的读写操作。

EEPROM芯片AT24C02,让大家熟悉使用verilog进行I2C通信。

4个独立按键,进行verilog脉冲采样和按键消抖控制。

4个流水灯,配合4位按键进行Johnson计数器实验。

蜂鸣器,实现简单的分频计数器。

2位数码管,使用其进行计数实验。

外接信号电平转换芯片SN74LVC4245,可以与单片机等5V器件进行通信,预留16PIN总线接口。

使用电源开关和电源指示灯,系统稳定可靠。

3. EPM240T100C5芯片介绍

选用Altera公司目前市场性价比较高的MAXII系列的CPLD。Altera推出的MAX II器件系列是一款革命性的CPLD产品。它基于突破性的CPLD架构,提供业界所有 CPLD系列中单个I/O管脚最低成本和最小功耗。这些器件采用新的查表(LUT)体系,采用TSMC的0.18μm嵌入Flash工艺,使其裸片尺寸仅为同样工艺器件的1/4。

MAX II系列和上一代MAX产品相比,成本降低了一半,功耗只有其1/10,同时保持MAX系列原有的瞬态启动、单芯片、非易失性和易用性。新的系列器件容量翻了两番,性能是上一代MAX CPLD的两倍多,使消费类、通信、工业和计算机产品的设计者能够采用MAX II系列器件代替昂贵和不够灵活的小型ASIC和ASSP。

MAX II 系列器件的主要特征:

成本优化的架构:新型 MAX II CPLD 架构包括基于 LUT 的 LAB 阵列、非易失性 Flash 存储模块和 JTAG 控制电路。

低功耗:MAX II 器件是动态功耗较低的 CPLD。

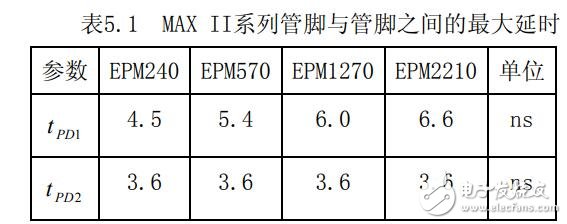

高性能:MAX II 器件支持高达 300MHz 的内部时钟,可为用户提供更高的系统级性能。通过改善布线结构管脚间的延时与其他同容量的 CPLD 相比大大降低,目前降低到 3.6ns。MAX II 系列管脚与管脚之间的最大延时见表 5.1,其中 PD1 t 为最大距离管脚之间的延迟时间(即对角上的管脚之间), PD2 t 为最小距离管脚的延迟时间(即相邻的管脚之间)。

。用户 Flash 存储器:MAX II CPLD 内的用户 Flash 存储器是一个大小为 8Kbit、用户可访问且可编程的 Flash 存储器块,可用于用户自己定义的数据。

实时在系统可编程能力(ISP):MAX II 器件支持实时在系统可编程。

灵活的多电压内核:MAX II 架构支持 MultiVolt,允许器件在 1.8V、 2.5V 或 3.3V 电压环境下工作。

JATG 翻译器:MAX II CPLD 具有一种被称为 JATG 翻译器的功能,这种功能允许通过 MAX II 器件执行定制的 JTAG 指令,配置单板上不兼容 JTAG 协议的器件,从而简化了单板管理。

I/O 能力:MAX II CPLD 的 I/O 能力加强了其易用性和系统集成能力。表 5.2 列出了 MAX II 器件支持的 I/O 标准。

- 相关推荐

- 热点推荐

- 学习板

-

Lesson05:BJ-EPM240学习板介绍 - 第1节充八万 2023-08-20

-

课程5:BJ-EPM240学习板介绍2019-12-23 3630

-

深入浅出玩转FPGA视频:BJ-EPM240学习板介绍2019-12-16 2224

-

FPGA视频教程:BJ-EPM240学习板介绍2019-12-10 4412

-

BJ-EPM240学习板之Johnson.计数器实验2019-03-06 5937

-

FPGA视频教程之BJ-EPM240学习板的详细资料介绍2019-03-01 1497

-

FPGA视频教程之使用BJ-EPM240学习板进行数码管显示实验的资料说明2019-02-28 1426

-

基于BJ-EPMCPLD 开发板的串口通信实验2017-08-31 694

-

BJ-EPM_CPLD开发套件介绍2016-10-27 924

-

BJ-EPM240V2原理图2016-09-27 2471

-

BJ-EPM240学习板介绍2015-12-02 902

全部0条评论

快来发表一下你的评论吧 !