BJ-EPM240学习板之分频计数实验

电子说

1.4w人已加入

描述

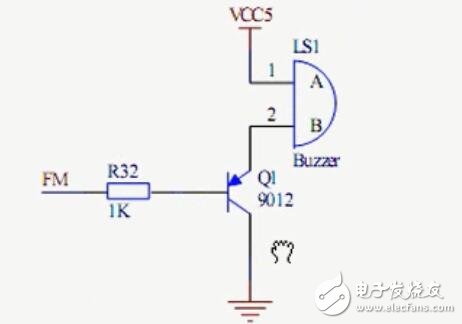

这个实验可以说是verilog入门最基础的实验了,我们不做太多的理论分析,实践是硬道理。蜂鸣器与CPLD的接口如图所示,当CPLD的1/0口(FM) 为低电平时,三极管截至,蜂鸣器不发声;当CPLD的I/0 (FM)为高电平时,三极管导通,蜂鸣器发声。

在verilog代码设计中,我们把分频输出的信号clk div与FM管脚对应,大家就可以真真切切的感受到什么是分频了。在代码里,用了20bit的计数器cnt,循环的计数,所以说一个周期有2的20次幂即大约1M分频。因为主时钟是50MHz(周期是20ns),所以大约20ms为-一个计数周期。蜂鸣器就以大约20ms的周期发声,如果大家希望蜂鸣器的发声频率改变,那么可以改变cnt的值看看效果。

更多关于BJ-EPM240学习板之分频计数实验请看视频。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

#硬声创作季 #FPGA 玩转FPGA-07 BJ-EPM240实验1-分频计数实验-1水管工 2022-10-29

-

BJ-EPM240学习板:Johnson计数器实验2019-12-24 2215

-

课程5:BJ-EPM240学习板介绍2019-12-23 3629

-

深入浅出玩转FPGA视频:BJ-EPM240学习板介绍2019-12-16 2224

-

FPGA视频教程:BJ-EPM240学习板-分频计数实验2019-12-10 2054

-

BJ-EPM240学习板之Johnson.计数器实验2019-03-06 5936

-

FPGA视频教程之BJ-EPM240学习板Johnson计数器实验的详细资料说明2019-03-04 1114

-

FPGA视频教程之BJ-EPM240学习板的详细资料介绍2019-03-01 1497

-

FPGA视频教程之使用BJ-EPM240学习板进行数码管显示实验的资料说明2019-02-28 1426

-

基于BJ-EPMCPLD 开发板的串口通信实验2017-08-31 694

-

BJ-EPM240学习板介绍2015-12-02 902

全部0条评论

快来发表一下你的评论吧 !