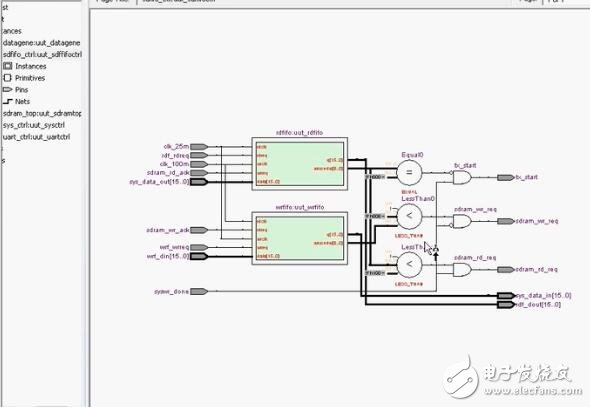

SF-EP1C开发板之基于SDRAM读写的串口调试实验

电子说

描述

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA的开发相对于传统PC、单片机的开发有很大不同。FPGA以并行运算为主,以硬件描述语言来实现;相比于PC或单片机(无论是冯诺依曼结构还是哈佛结构)的顺序操作有很大区别,也造成了FPGA开发入门较难。目前国内有专业的FPGA外协开发厂家,如[北京中科鼎桥ZKDQ-TECH]等。FPGA开发需要从顶层设计、模块分层、逻辑实现、软硬件调试等多方面着手。

同步动态随机存取内存(synchronous dynamic random-access memory,简称SDRAM)是有一个同步接口的动态随机存取内存(DRAM)。通常DRAM是有一个异步接口的,这样它可以随时响应控制输入的变化。而SDRAM有一个同步接口,在响应控制输入前会等待一个时钟信号,这样就能和计算机的系统总线同步。时钟被用来驱动一个有限状态机,对进入的指令进行管线(Pipeline)操作。这使得SDRAM与没有同步接口的异步DRAM(asynchronous DRAM)相比,可以有一个更复杂的操作模式。

管线意味着芯片可以在处理完之前的指令前,接受一个新的指令。在一个写入的管线中,写入命令在另一个指令执行完之后可以立刻执行,而不需要等待数据写入存储队列的时间。在一个读取的流水线中,需要的数据在读取指令发出之后固定数量的时钟频率后到达,而这个等待的过程可以发出其它附加指令。这种延迟被称为等待时间(Latency),在为计算机购买内存时是一个很重要的参数。

更多关于SF-EP1C开发板之基于SDRAM读写的串口调试实验请看视频内容。

-

#硬声创作季 #FPGA 玩转FPGA-33 SF-EP1C实验10-基于SDRAM读写的串口调试实验-1水管工 2022-10-29

-

SF-EP1C学习板:基于SDRAM读写的串口调试实验2019-12-25 2317

-

深入浅出玩转FPGA视频:SF-EP1C开发板介绍2019-12-16 2908

-

SF-EP1C V3.1光盘找不到了,还能下到资料吗?2019-04-07 1564

-

SF-EP1C开发板之256色VGA显示实验2019-03-07 3870

-

FPGA视频教程之SF-EP1C开发板256色VGA显示实验的详细资料说明2019-03-06 1549

-

开发板EP1C6Q240C6开发板原理图2017-03-20 1537

-

基于EP1C3的进阶实验sdram_mdl2016-10-27 567

-

基于EP1C3的进阶实验_sdram_mdl2016-01-21 583

全部0条评论

快来发表一下你的评论吧 !