Quartus.II调用ModelSim仿真实例

电子说

描述

Quartus.II调用ModelSim仿真实例

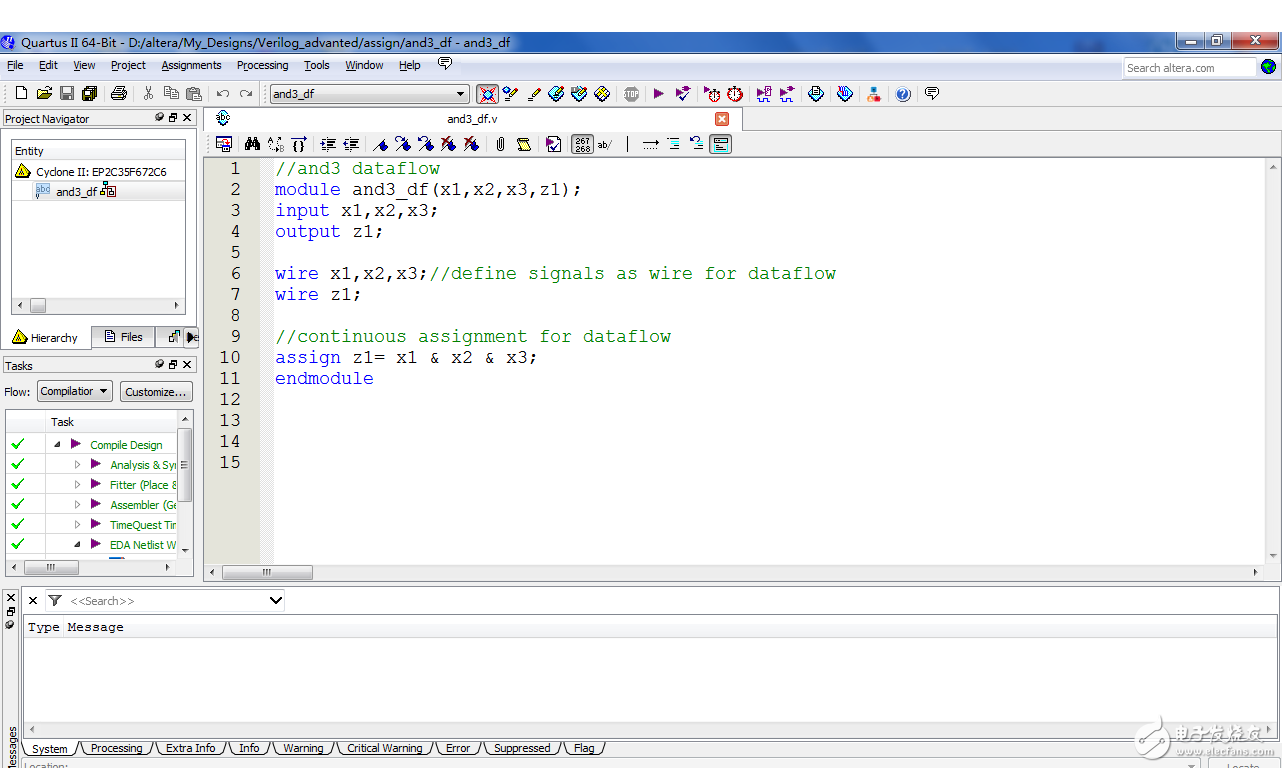

1、建立工程如下

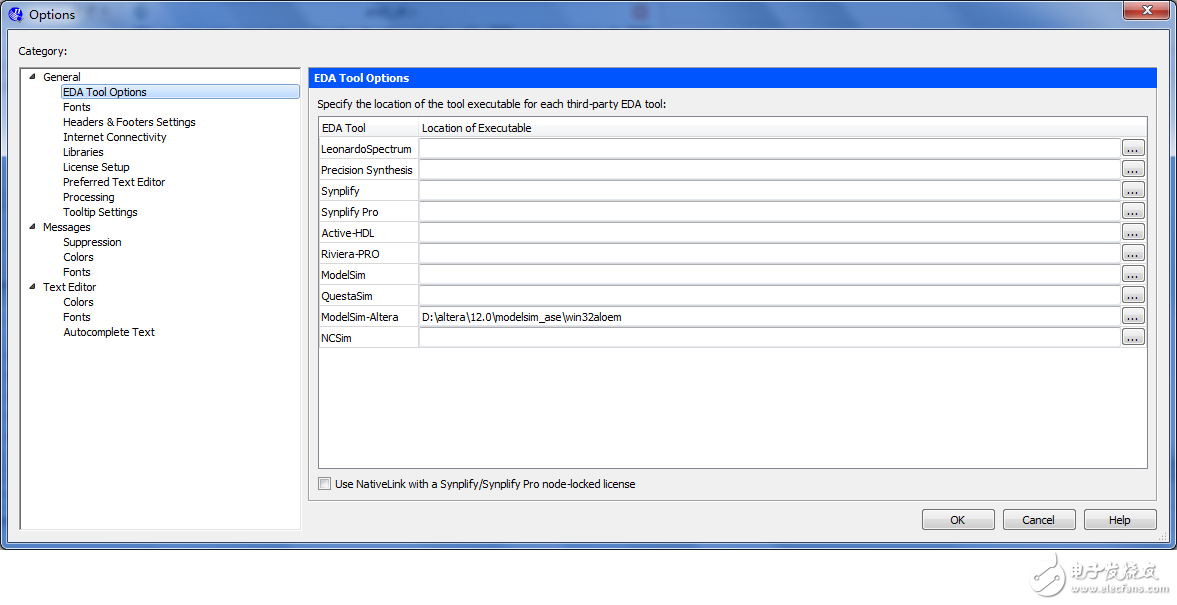

2.如果是第一次使用modelsim,需要建立Quartus ii12.0和modelsim的链接。Quartus II12.0-》Tools-》option-》EDA Tool options再选择自己的软件和对应的安装文件夹,如下

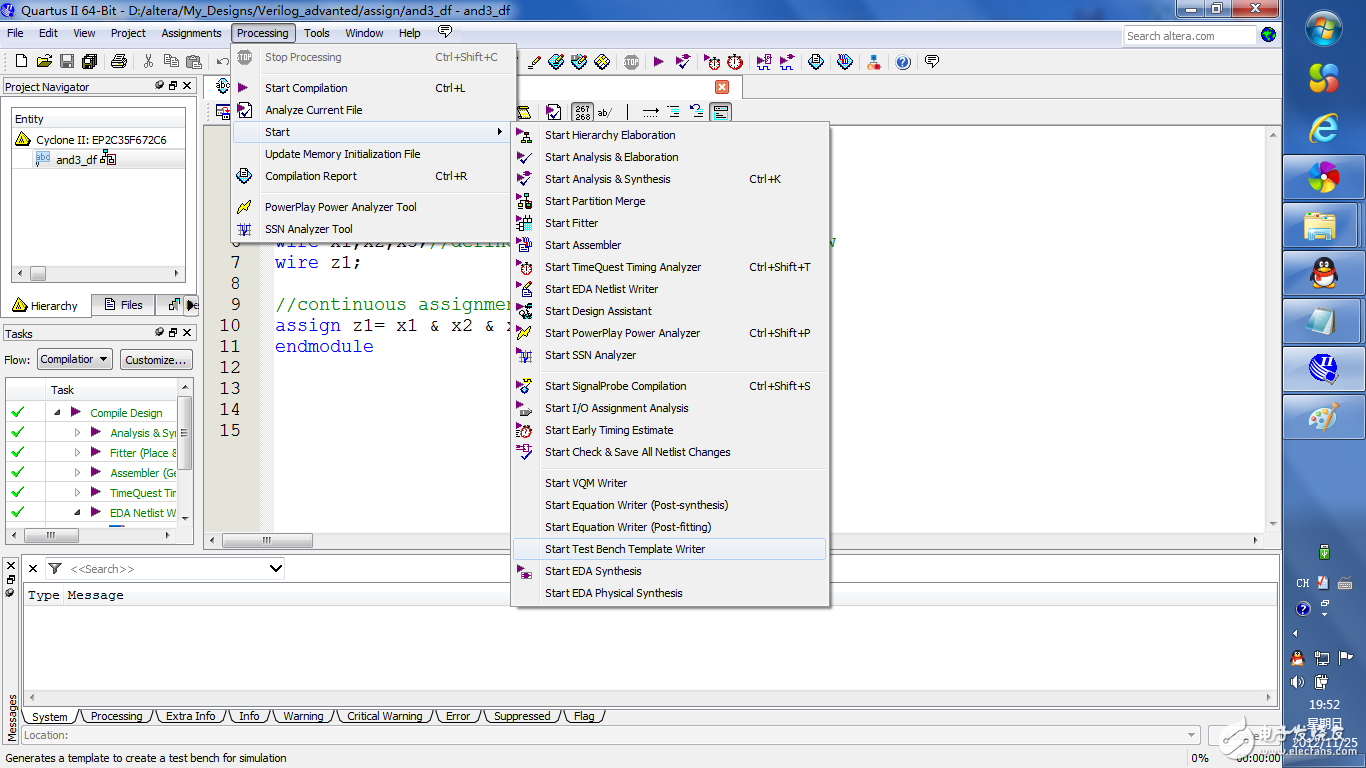

3.建立测试文件(testbench)可以自己写,也可以用quartus II自己生成(生成的只是模版,功能需要自己添加),注:testbench的输出为要测试文件的输入,即测试文件是为要测试文件产生信号用的,因此testbench的input为reg变量,输出为wire变量,具体操纵如下

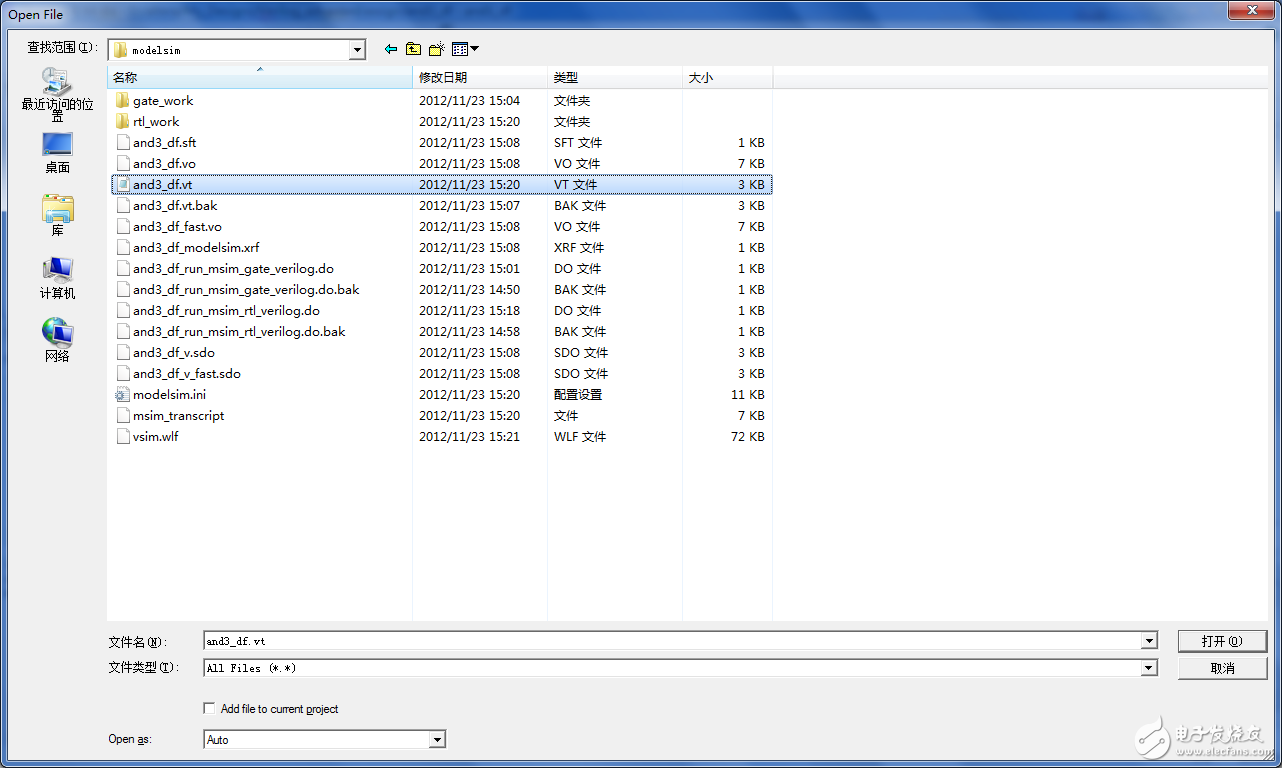

4.打开测试文本,添加测试的信号功能(注:上步生成的文件后缀为.vt,在所建工程下的simulationmodelsim下面)。

5.添加信号功能如下。

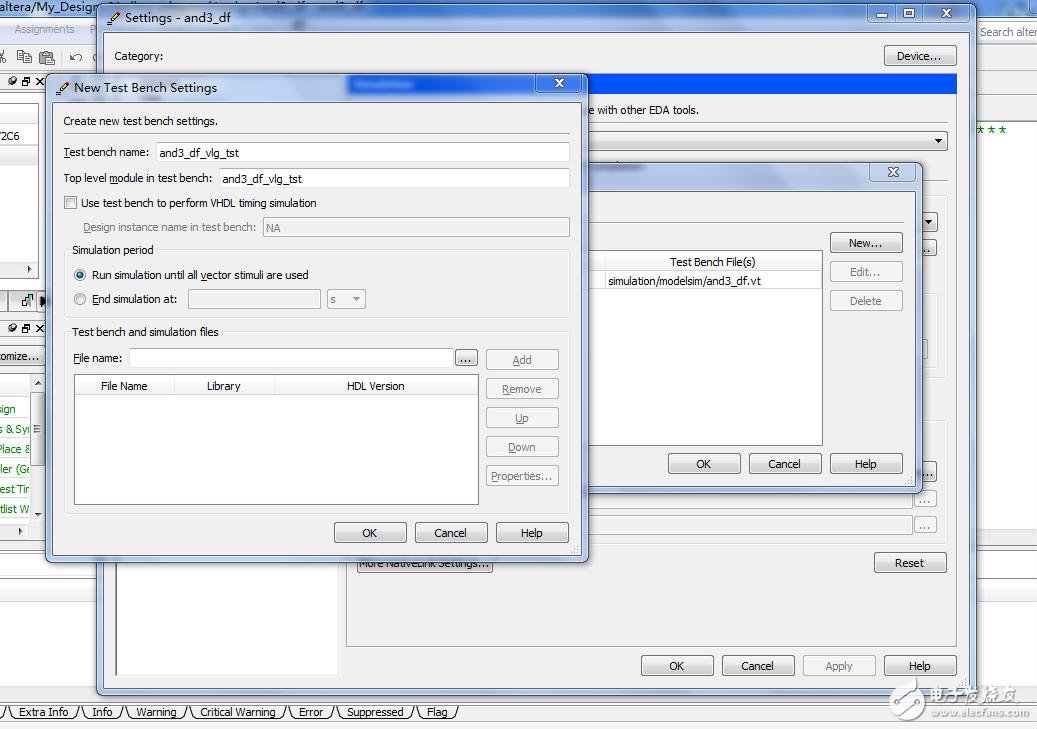

6.复制测试文件模块名(供下步添加testbench name用)添加测试文件。assignment-》setting-》

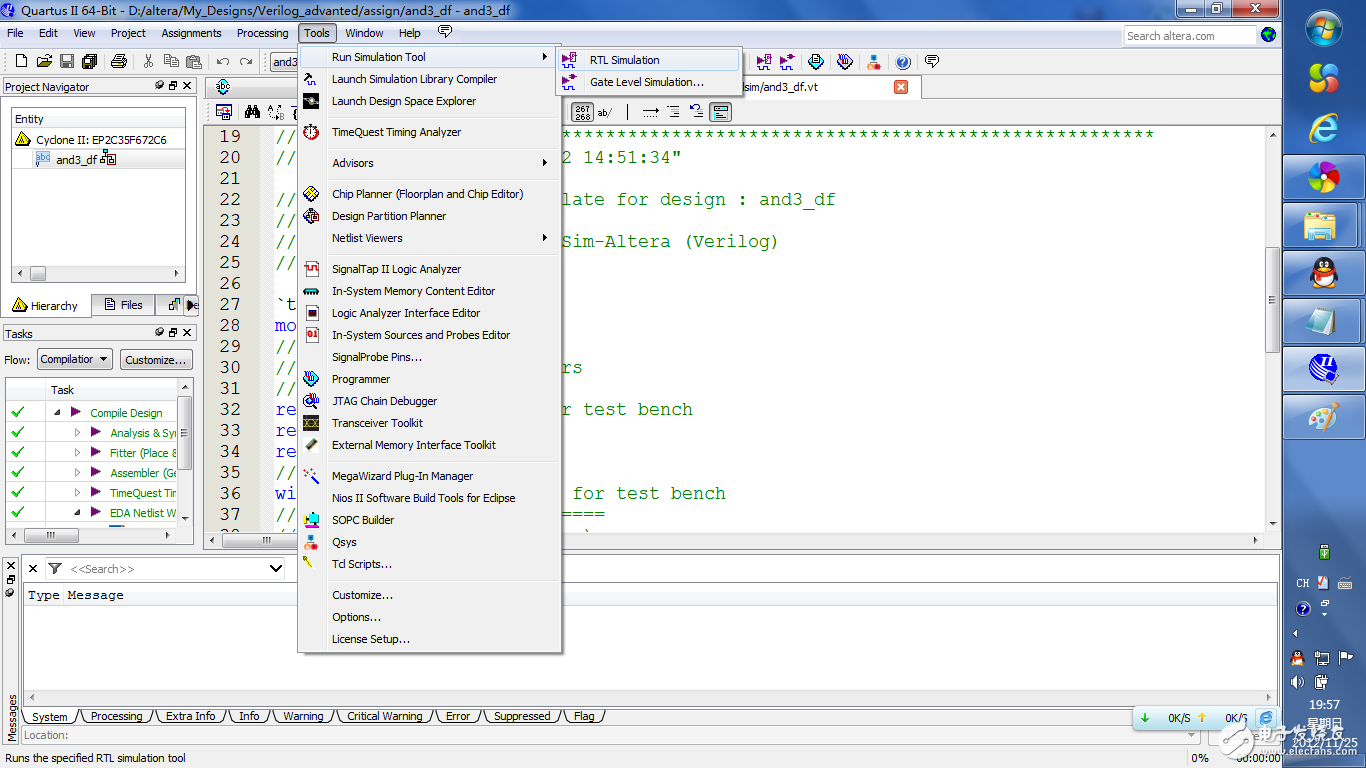

7、开始仿真Tools-》run-》simulation tool

8.结果(若没有自动运行,需按simulation和add wave)

程序

//and3 dataflow

module and3_df(x1,x2,x3,z1);

input x1,x2,x3;

output z1;

wire x1,x2,x3;

wire z1;

assign z1= x1 & x2 & x3;

endmodule

test bench

`timescale 1 ns/ 1 ps

module and3_df_vlg_tst();

// constants

// general purpose registers

//========================

reg x1;//inputs are reg for test bench

reg x2;

reg x3;

// wires

wire z1;//outputs are wire for test bench

//============================

// assign statements (if any)

and3_df i1 (

// port map - connection between master ports and signals/registers

.x1(x1),

.x2(x2),

.x3(x3),

.z1(z1)

);

initial

begin :APPlicable

// code that executes only once

// insert code here --》 begin

//=============================================

reg [3:0] invect; //test invect

for(invect =0;invect《8;invect=invect+1)

begin

{x1,x2,x3} = invect [3:0];

#10 $display (“x1 x2 x3 = %b ,z1 = %b”,

{x1,x2,x3},z1);

end

//==============================================

// --》 end

end

endmodule

- 相关推荐

- 热点推荐

- quartus

-

20 Lesson20:BJ-EPM240学习板实验13——Quartus.II调用ModelSim仿真实例充八万 2023-08-18

-

基于ModelSim使用二联合Quarus自动仿真教程2021-07-23 3293

-

在Altera Quartus II下如何调用ModelSim进行仿真?2021-04-30 1753

-

Quartus II调用ModelSim仿真实例2019-11-15 4347

-

如何在Quartus13.0中调用Modelsim详细的步骤说明2019-07-01 2690

-

FPGA视频教程之Quartus.II调用ModelSim仿真实例详细资料说明2019-03-05 1604

-

关于quartus如何调用modelsim详细解说2018-05-18 37909

-

quartus.ii免费安装2012-11-14 1085

-

Quartus II的仿真实验资料2010-02-08 751

-

基于Quartus II + ModelSim SE的后仿真2009-07-22 514

全部0条评论

快来发表一下你的评论吧 !