高速SI应用中对各种层压材料进行介电常数和介电损耗精确提取的方法

描述

本文介绍了在高速SI应用中对各种层压材料进行介电常数(Dk)和介电损耗(Df)精确提取的方法。 TOD去嵌算法和优化算法用于该Dk / Df提取流程。 由此得到的频变材料参数模型可以用于市场上的任何电磁场仿真工具。

1

简介

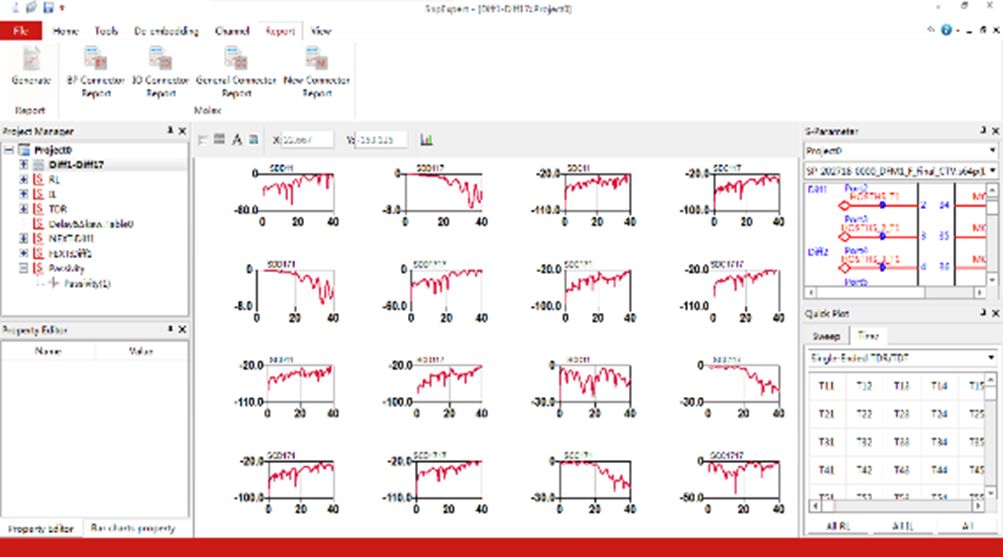

芯禾科技SnpExpert工具,提供了一种快速了解系统中无源互连器件电气特性的方法,不仅可以查看S参数频域特性,还可以查看时域反射结果(TDR)。该方案亮点包括:差分对和victim/aggressor设置的一键定义,以及内置的NEXT/FEXT/PSXT/ILD/ICR和ICN,允许用户快速评估串扰;内置delay和skew计算器无需繁琐的电路原理图绘制;采用内置IEEE 802.3ap,802.3ba,802.3bj,SAS,PCIe,SATA,USB和OIF CEI 25G / 28G的合规性指标可快速显示S参数合规性;内置模板自动执行从S参数绘图到生成Word或PPT报告的流程;TOD方法帮助SI工程师通过去除夹具效应来快速获得DUT结果;使用均衡和预加重技术进行精确的NRZ和PAM-4眼图计算,帮助SI工程师获得关于高速通道性能的直观感受。

图1 SnpExpert 用户界面

2

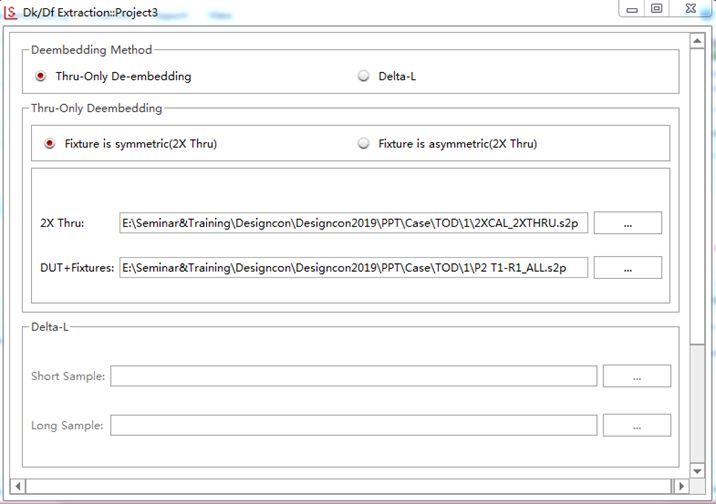

Through-Only De-embedding(TOD)

为了计算介电常数(Dk)和介电损耗(Df),需要制作常规的传输线结构,以探索PCB材料的射频和微波参数。 SnpExpert为设计人员提供了一种简单的方法,可以从复合测量中去嵌夹具,以提取DUT特性,这对于对称和非对称夹具结构的测试、测量和dk / df提取至关重要。

图2 Through-Only De-embedding 流程

3

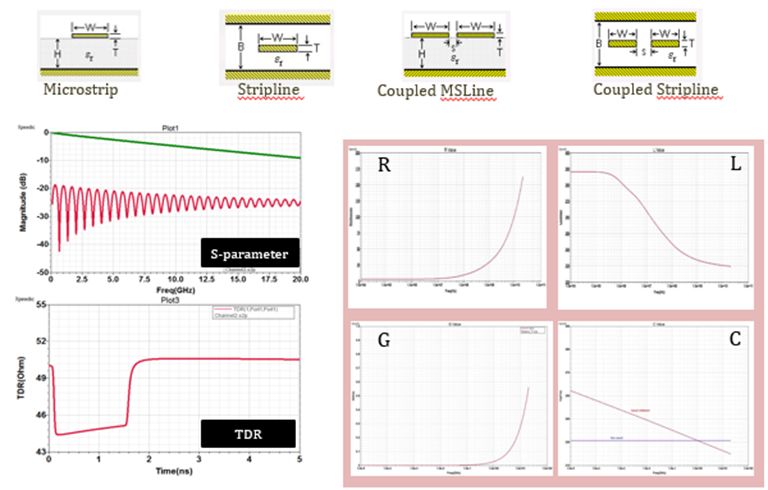

快速 2D RLGC 求解器

我们在Dk / Df提取流程中集成了具有因果介电模型和表面粗糙度模型的基于2D FEM的RLGC快速场求解器,这能显著提高PCB材料特性的提取精度。 Dk / Df提取流程将重复调用RLGC求解器,直到插入损耗的幅度和相位满足收敛误差。

图3 2D RLGC 求解器

4

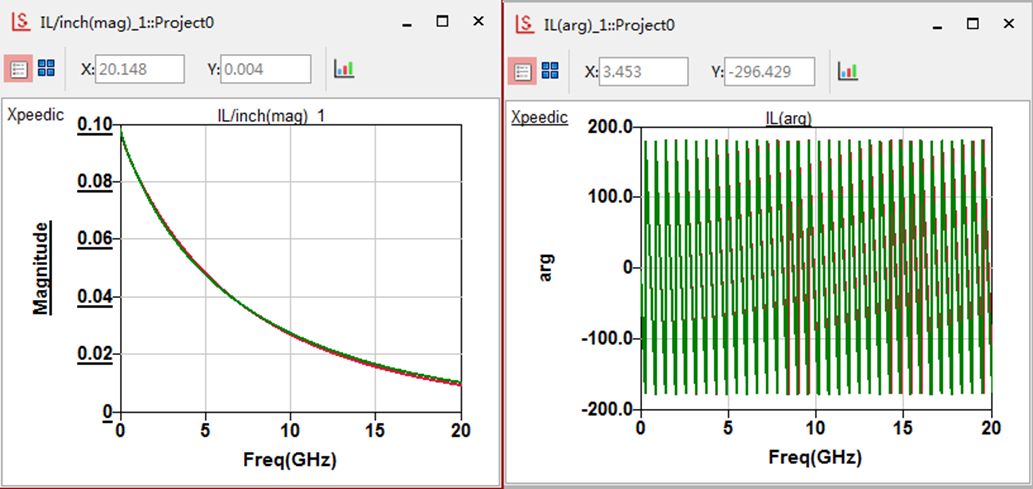

Dk/Df 提取流程中的遗传算法

在Dk/Df和表面粗糙度的初始猜测之后,我们使用了基于自然选择过程的改进遗传算法(GA)优化来适配IL,这显著减少了在Dk / Df提取中调用2D FEM RLGC求解器的迭代次数。

图4 基于遗传算法的 IL 匹配过程

5

总结

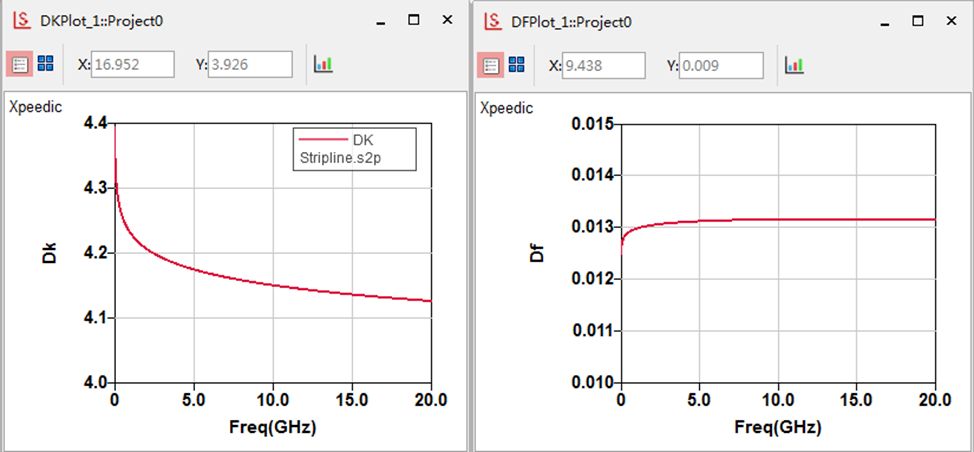

本文描述了基于TOD和GA优化算法的Dk / Df提取流程,适用于高速和宽带应用。 该流程可以显著简化具因果性的电介质模型和表面粗糙度模型的提取。

图5 dk 与 df 曲线

-

材料介电常数会影响电子元器件哪些性能2025-01-20 2517

-

如何测量材料的相对介电常数2025-01-10 3372

-

介电常数的定义及应用 不同材料的介电常数比较2024-11-25 25211

-

介电常数只需要测试容值?介电常数与介电损耗有什么区别#同惠电子 #介电常数 #介电损耗安泰小课堂 2024-07-09

-

相对介电常数和介电常数的关系2024-01-14 19495

-

介电常数测定仪介绍2024-01-11 1763

-

低介电常数材料的失效分析2023-10-12 3228

-

介电常数用什么仪器测量?2023-03-24 2434

-

关于高频绝缘材料介电常数介质损耗测试系统的介绍2021-04-26 2990

-

介电常数怎么测试_介电常数测试方法2017-12-05 74500

-

低介电常数微波介质陶瓷基覆铜板的研究2017-09-19 3083

-

高频PCB基材介电常数与介电损耗的特性与改性进展2012-04-11 1798

-

PCB层压材料制做2010-09-20 813

全部0条评论

快来发表一下你的评论吧 !