简单的Testbench设计

电子说

1.4w人已加入

描述

Testbench

testbench是一种验证的手段。首先,任何设计都是会有输入输出的。但是在软环境中没有激励输入,也不会对你设计的输出正确性进行评估。那么此时便有一种,模拟实际环境的输入激励和输出校验的一种“虚拟平台”的产生。在这个平台上你可以对你的设计从软件层面上进行分析和校验,这个就是testbench的含义。

简单的Testbench设计

//timescale 仿真时间单位/时间精度(时间精度不能比时间单位还要大)

timescale 1ns/1ps

//定义一个无输入无输出的Moudle

module Led_clg_tst();

//被测设计的输入信号,对应测试脚本的输出信号(注意要定义成reg)

reg clk;

reg rst_n;

//被测设计的输出信号,对应测试脚本的输入信号(注意要定义成wire)

wire led;

//例化待测模块

Led led_test

(

.clk(clk),

.rst_n(rst_n),

.led(led)

);

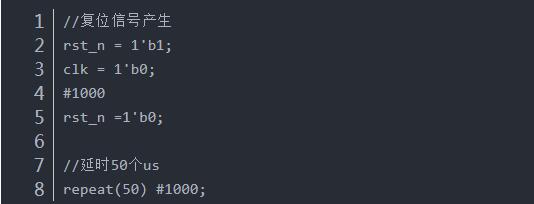

//使用Initail生成rst_n激励

initial

begin

//监控Led信号变化

monitor(monitor(time,”led value= %b\n”,led);

end

//使用alwasys模拟产生25M的时钟信号

always #20 clk = ~clk;

endmodule

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 设计

-

编写高效Testbench的指南和示例2024-10-29 2892

-

Lesson08:简单的Testbench设计 - 第1节充八万 2023-08-20

-

testbench是什么? testbench测试的机制是什么?2023-06-28 6522

-

#硬声创作季 #FPGA 玩转FPGA-08 简单的Testbench设计-1水管工 2022-10-29

-

课程8:简单的Testbench设计2019-12-24 2453

-

深入浅出玩转FPGA视频:简单的Testbench设计2019-12-17 2462

-

FPGA视频教程:简单的Testbench设计2019-12-11 2605

-

FPGA教程之简单的Testbench设计的详细资料说明2019-03-01 1532

全部0条评论

快来发表一下你的评论吧 !