ADC电源抑制中如何计算允许的电源纹波

电源/新能源

3626人已加入

描述

在这篇博文中,我们将完成模数转换器(ADC)表征,解释结果,并深入了解元件选择,以了解电源规格权衡与ADC性能的关系。

让我们首先看一下ADC PSRR特性。为了保持连续性,我们将使用ADC3444作为示例。该ADC3444是一款四通道,14位,125MSPS流水线ADC。使用“在ADC中测量PSRR”中开发的方法,我们创建了这些PSRR图:

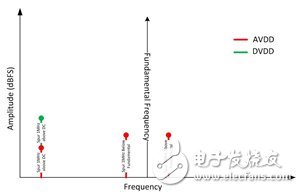

图1:由ADC电源上的AC信号引起的杂散位置

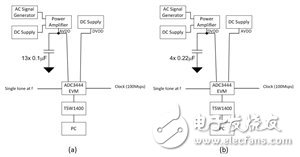

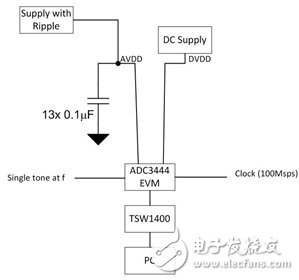

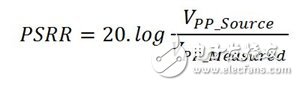

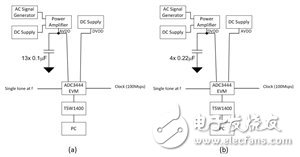

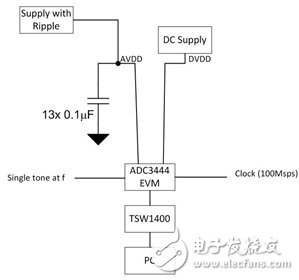

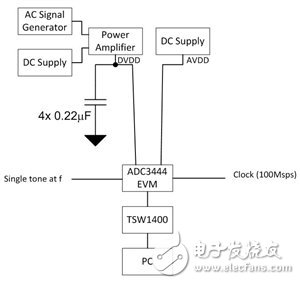

该ADC3444 AVDD和DVDD提供完整的PSRR特性,如下图所示。请注意,每个ADC的本地旁路都已到位,每个AVDD电源引脚上的电流为0.1μF,每个DVDD电源引脚上的电流为0.22μF,AVDD上的总电流为1.3μF,DVDD上的电流为0.88μF。图2是测试配置框图。

图2:(a)AVDD测试电路配置; (b)DVDD测试电路配置

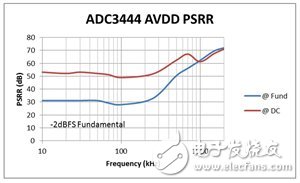

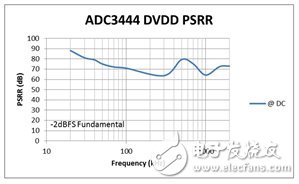

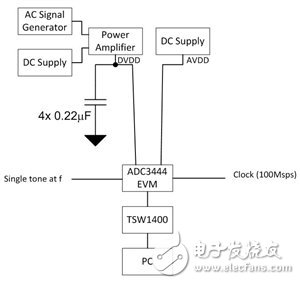

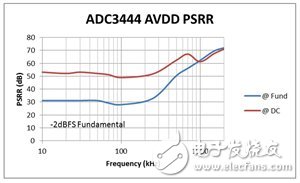

图3显示了-2dBFS时基波的PSRR与频率的关系。两个结论突然出现在你面前:

PSRR与频率的改善不是由ADC PSRR引起的,而是由旁路电容衰减的干扰信号引起的。

图3:AVDD PSRR与频率的关系

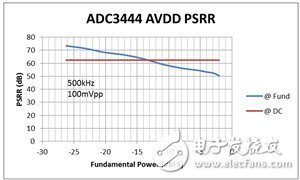

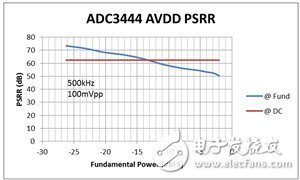

为了验证AVDD电源的PSRR是否依赖于基波,测量了图4。它显示了带有基波的杂散的dB / dB依赖性。换句话说,干扰源存在于基波周围,具有设定的dBc(低于载波的dB)响应。在DC,干扰源对于ADC的动态范围内的任何信号保持恒定。

图4:AVDD PSRR与模拟输入功率的关系

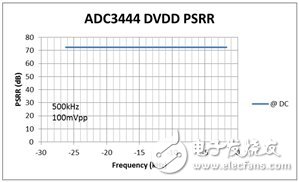

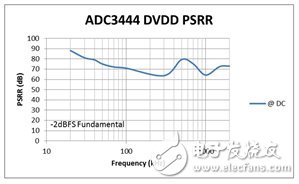

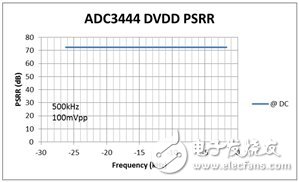

我对ADC的数字电源采用了相同的方法,如图5和图6所示。正如预期的那样,数字电源PSRR比模拟电源的PSRR要好一个数量级,即20dB。还可以感觉到旁路电容的存在,但超过300kHz,但不会像模拟电源一样长。也没有依赖于基波的幅度。

图5:DVDD PSRR与频率的关系

图6:DVDD PSRR与输入功率的关系

这是一项有趣的练习,但我们可以从结果中得出什么结论呢?

第一个结论是ADC3444中使用的架构对模拟电源最敏感。请记住,上述结果是典型的,应添加保护带。由于28dB是-2dBFS时的最差结果,PSRR降低了dB / dB,因此全摆幅0dBFS将具有26dB的PSRR。考虑到过热和过载变化至少10dB的保护带,使ADC3444 AVDD 的最小PSRR为16dB。10dB保护带是一种估计值,需要额外的特性以确保足够的性能水平。

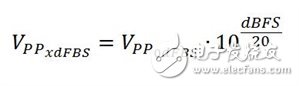

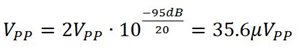

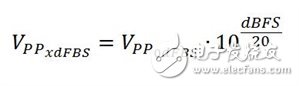

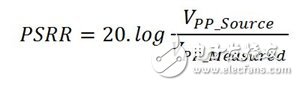

使用与“在ADC中测量PSRR”中相同的等式,参见下面的等式1和2。现在可以估计DC / DC转换器中存在的最大允许纹波,现在考虑到ADC直接由包含纹波的电源供电。

图7:非理想AVDD电源的电路配置

系统设计公差将揭示维持所需性能的最大可接受刺激。我们在这里考虑最差的杂散不能超过-95dBFS。这意味着使用16dB最坏情况PSRR并使用下面的等式1和2,我们可以确定最大允许电源纹波。

(ADC PSRR衰减后允许的最大纹波幅度)

(ADC PSRR衰减后允许的最大纹波幅度)

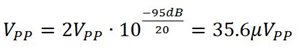

这导致我们:

这是AVDD电源引脚上可能出现的最大纹波。

我们可以通过以下方式放宽这一严格要求:

图8:非理想AVDD电源的电路配置

DVDD最差为62dB。在这个典型值上保持10dB的余量,我们可以计算出DVDD电源引脚上的最差干扰,以确保FFT中的-95dBFS性能为14.17mVpp。

这些计算提供了ADC两种电源所需性能的指导原则。在我的下一篇文章中,我将讨论为每种供应开发适当的电源解决方案及其对性能的影响。

打开APP阅读更多精彩内容

让我们首先看一下ADC PSRR特性。为了保持连续性,我们将使用ADC3444作为示例。该ADC3444是一款四通道,14位,125MSPS流水线ADC。使用“在ADC中测量PSRR”中开发的方法,我们创建了这些PSRR图:

- 模拟VDD(AVDD)PSRR在DC和基波与频率之间。

- AVDD PSRR与基波输入功率。

- 数字VDD(DVDD)PSRR与频率的关系。

图1:由ADC电源上的AC信号引起的杂散位置

该ADC3444 AVDD和DVDD提供完整的PSRR特性,如下图所示。请注意,每个ADC的本地旁路都已到位,每个AVDD电源引脚上的电流为0.1μF,每个DVDD电源引脚上的电流为0.22μF,AVDD上的总电流为1.3μF,DVDD上的电流为0.88μF。图2是测试配置框图。

图2:(a)AVDD测试电路配置; (b)DVDD测试电路配置

图3显示了-2dBFS时基波的PSRR与频率的关系。两个结论突然出现在你面前:

- 基波周围的两个杂散的PSRR比DC的PSRR差20dB。

- 两种PSRR均为~200kHz,并且实际上正在改善。

PSRR与频率的改善不是由ADC PSRR引起的,而是由旁路电容衰减的干扰信号引起的。

图3:AVDD PSRR与频率的关系

为了验证AVDD电源的PSRR是否依赖于基波,测量了图4。它显示了带有基波的杂散的dB / dB依赖性。换句话说,干扰源存在于基波周围,具有设定的dBc(低于载波的dB)响应。在DC,干扰源对于ADC的动态范围内的任何信号保持恒定。

图4:AVDD PSRR与模拟输入功率的关系

我对ADC的数字电源采用了相同的方法,如图5和图6所示。正如预期的那样,数字电源PSRR比模拟电源的PSRR要好一个数量级,即20dB。还可以感觉到旁路电容的存在,但超过300kHz,但不会像模拟电源一样长。也没有依赖于基波的幅度。

图5:DVDD PSRR与频率的关系

图6:DVDD PSRR与输入功率的关系

这是一项有趣的练习,但我们可以从结果中得出什么结论呢?

第一个结论是ADC3444中使用的架构对模拟电源最敏感。请记住,上述结果是典型的,应添加保护带。由于28dB是-2dBFS时的最差结果,PSRR降低了dB / dB,因此全摆幅0dBFS将具有26dB的PSRR。考虑到过热和过载变化至少10dB的保护带,使ADC3444 AVDD 的最小PSRR为16dB。10dB保护带是一种估计值,需要额外的特性以确保足够的性能水平。

使用与“在ADC中测量PSRR”中相同的等式,参见下面的等式1和2。现在可以估计DC / DC转换器中存在的最大允许纹波,现在考虑到ADC直接由包含纹波的电源供电。

图7:非理想AVDD电源的电路配置

系统设计公差将揭示维持所需性能的最大可接受刺激。我们在这里考虑最差的杂散不能超过-95dBFS。这意味着使用16dB最坏情况PSRR并使用下面的等式1和2,我们可以确定最大允许电源纹波。

(ADC PSRR衰减后允许的最大纹波幅度)

(ADC PSRR衰减后允许的最大纹波幅度)

这导致我们:

这是AVDD电源引脚上可能出现的最大纹波。

我们可以通过以下方式放宽这一严格要求:

- 减少PSRR上的保护频带。

- 不在完全动态范围内运行ADC。

- 允许FTT中的杂散大于-95dBFS。

图8:非理想AVDD电源的电路配置

DVDD最差为62dB。在这个典型值上保持10dB的余量,我们可以计算出DVDD电源引脚上的最差干扰,以确保FFT中的-95dBFS性能为14.17mVpp。

这些计算提供了ADC两种电源所需性能的指导原则。在我的下一篇文章中,我将讨论为每种供应开发适当的电源解决方案及其对性能的影响。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

在LED电源设计中抑制输出电流纹波的方法2023-09-04 2918

-

ADC电源抑制,计算允许的电源纹波2018-07-24 5248

-

如何抑制开关电源的纹波噪声2022-05-01 10529

-

DC/DC电源中的纹波抑制设计2011-07-05 16995

-

基于Buck电路的开关电源纹波的计算和抑制2015-11-20 975

-

开关电源纹波的几种抑制方法2016-09-20 1306

-

如何对ADC中的电源抑制PSR进行有效测量 (2)2019-04-17 3118

-

开关电源的纹波噪声抑制(下)2021-03-14 1460

-

测试电源纹波及抑制电源纹波的方法2022-04-25 5635

-

如何测量开关电源纹波 开关电源的纹波抑制2023-05-02 5101

-

开关电源的五种纹波噪声如何抑制?2023-11-06 2818

-

如何抑制开关电源的输出纹波?2023-12-05 2893

-

对于电源的纹波你知道多少?如何测量又是如何抑制它呢?2023-11-29 2120

-

电源纹波与电源抑制比解析2024-05-21 2743

-

开关电源的纹波噪声如何抑制2024-05-30 2066

全部0条评论

快来发表一下你的评论吧 !