一种基于FPGA采用重采样技术的HD-SDI到SD-SDI的下变换实现设计

可编程逻辑

描述

随着我国数字广播电视技术的日趋成熟,电视台采用高清数字串行信号(HD-SDI)下变换系统,目前大多数下变换采用ASIC进行高清数字电视信号下变换,成本较高且系统的硬件电路设计复杂、移植性差、不容易升级。而利用FPGA开发,就可以体现出周期短、成本低、集成度和可移植性好,可随时更改程序以适应电视制式标准的变更等优点,本文提出了一种基于FPGA采用重采样技术的HD-SDI到SD-SDI的下变换实现方法。

1 HD-SDI与SD-SDI的区别

根据ITU-R BT.709-3标准,我国SDI的高清演播室电视信号接口标准规定为1125/50扫描标准,水平、垂直有效像素为1 920×1 080,4:2:2编码格式,亮度信号Y的抽样频率为74.25 MHz,两个色差信号Cb/Cr的抽样频率为37.125 MHz,采用10 bit量化,Y与Cb/Cr信号分成两个通道传输,每个通道并行数据传输率74.25 MB·s-1;根据ITU-R BT.656标准,我国标清演播室信号接口规定为625/50扫描标准,水平、垂直有效像素为720×576,4:2:2编码格式,亮度信号Y的抽样频率为13.5 MHz,两个色差信号Cb/Cr的抽样频率为6.75MHz,采用10 bit量化,时分复用Y,Cb/Cr一个通道传输,并行数据传输率27 MB·s-1。

2 HD-SDI下变换的系统描述

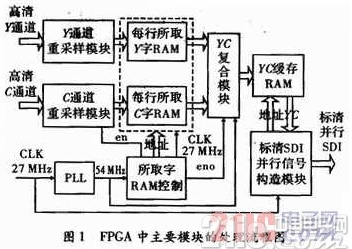

高清数字电视信号下变换的主要原理是一帧图像中水平行与垂直像素点的减少。文中的研究主要是以FPGA为核心,HD-SDI信号以并行的形式输入FPGA,在FPGA中进行视频信号重采样算法、所取字RAM控制和YC复合处理、SD-SDI的并行信号格式的重构等处理,从而完成HD- SDI的下变换。FPGA中对信号的整个处理过程用Verilog HDL语言来编程实现,FPGA中的各主要处理模块的流程图,如图1所示。

2.1 重采样处理

由下变换原理可知,从HD分量信号获得低分辨率的SD分量信号,可分别在垂直方向和水平方向上的有效视频区去抽取有效像素点来实现图像格式的转换。考虑到二维空间的数据计算量和复杂性,常用两个一维滤波器实现二维空间的转换,即先在垂直方向上抽值,然后再在水平方向上抽值,这样减少计算复杂性,提高运算速度。抽出的值可以是相邻几个样点去抽一个。

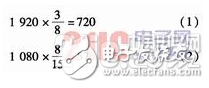

图像下变换时,通过抽取滤波器抽取原有信号的取样点值,增大采样的点空间距离,降低每行的有效像素和垂直行。高清1 920×1 080格式下变换为标清720×576格式,由于高清信号的水平与垂直分解力不是标清信号4:2:2编码的整数倍,所以本文主要通过以下两个计算式抽取像素点来实现

有效行处理原理:由视频分量信号的特性,先找到一帧视频信号的有效行,然后按式(2)在高清一帧共1 080条有效行中按每15行取8行循环抽取,从而得到标清所要求的576行的有效行。

有效垂直像素点处理原理:找到一行数据中的有效图像像素点,然后按式(1)在高清一行1 920个有效像素点中按照16个点取6个点循环抽取,从而得到标清所要求的720个有效像素点。有效行处理与有效垂直像素点处理程序流程图,如图2所示。

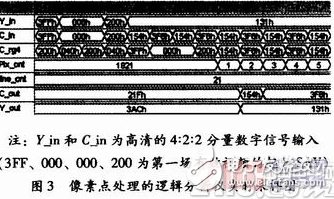

有效行处理与有效垂直像素点处理的逻辑分析仪实时采样图如图3所示。由图3可以看出,C_rg4为C_in的4个寄存器延时,行计数line_e- nt=21可以看出此图采样是的高清分量视频有效视频21行的数据,在检测到有效视频行起始SAV后对有效像素点进行计数(计数值为Pix_ent),然后针对Pix_ent进行抽取处理得到标清分量信号所需要的像素点通过Y_out和C_out输出。

2.2 所取字RAM控制和YC复合处理

所取字RAM控制主要是对有效行所取Y、C字的存取RAM进行控制的模块。有效行所取字RAM模块用来完成所取的像素缓存和时钟的转换与匹配,由图1可以看出,首先把重采样针对高清信号行所取的构造标清信号所要有效像素点存进有效行所取字的RAM,同时把重采样模块输出的存720个有效像素点时间长度控制使能en信号给所取字RAM控制模块。所取字RAM控制模块主要是给读地址、读使能与读时钟27 MHz去读取所取Y、C字RAM中的有效像素点送给YC复合模块。YC复合模块主要作用是把所得的色度信号Y与色差信号C两个通道的数据合成一个通道的时分复用Y/C数据,其处理方式是根据输入的有效像素的时间长度使能eno,用54 MHz的时钟去读取27 MHz的Y和C数据,从而完成时分复合,再送给YC缓存RAM存下数据。其YC复合处理图如4所示。

YC缓存RAM作用主要是缓存几行标清所要的有效像素数据。由于高清视频信号一帧图像中,其开始的场消隐时间比标清视频信号短,而有效行数据的出现就比标清视频快,为了不让一帧图像的有效信息丢失,使用了RAM去缓存了几行的有效数据。除此以外,YC缓存RAM模块也起到了时钟转换与匹配的作用,把54 MHz的数据转换为27 MHz的数据输出给标清视频构造模块。

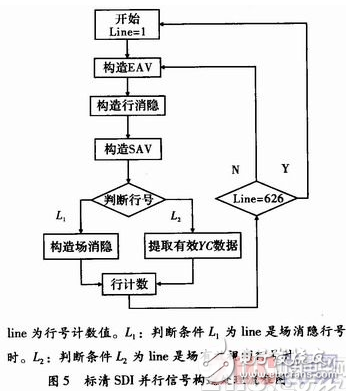

2.3 标清SDI并行信号构造处理

标清SDI并行构造模块主要是提取标清图像所要的标清像素点的YC数据,并把数据构造成满足标清SDI并行分量信号所要求的格式输出。其处理过程是根据传输标清数据所要的27 MHz时钟来构造标清分量信号中的视频定时基准码(有效视频开始SAV和有效视频结束EAV)、行消隐数据、场消隐数据。处理过程的流程图,如图5所示。

标清SDI并行信号构造处理的逻辑分析仪实时采样图如图6所示。由图6可以看出Y_in和C_in为高清视频输入的并行数据经下变换处理后变成标清视视频并行数据q1(3FF、000、000、200为第一场有效视频的起始SAV,154 h和131 h为有效像素点)。图中line=24为标视频的第一场中的有效行,data_in为标清构造模块从YC缓存RAM由相应读地址addre获得的有效像素的数据。

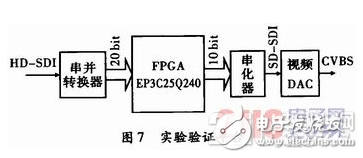

3 验证

本设计通过基于Altera CycloneⅢ系列FPGA芯片EP3C25Q240实验平台的验证。整个实验验证平台结构如图7所示,视频信号处理流程简要如下:我国高清标准HD- SDI信号经过串并转换芯片变成符合文中设计所要的10 bit的Y分量和10 bit的C分量,高清分量信号进入FPGA进行下变换处理后变成10 bit的时分复用YC的标清视频分量信号,标清视频分量信号再串化为SD-SDI信号送给视频DA板变成普通模拟CVBS视频信号给电视机显示。通过 QuanusⅡ自带的嵌入式逻辑分析仪观察FPGA中的处理数据,数据符合要求,CVBS视频信号送给电视机显示,图像满屏显示,比较清晰且无抖动。

4 结束语

本设计是针对演播室内的HD-SDI信号进行的下变换,直接对图像信号中的有效像素进行处理,将1 920×1 080(HDTV)视频SDI流转换为720×576(SDTV)视频SDI流,经过上述验证得出:此下变换设计没有丢失图像信号,只是降低了图像清晰度,且实现简单,成本较小,易于在工程中实现。对于规模较小的地方数字电视台实现了高清节目共享,合理地利用了信道资源,节约了扩建高清设备的成本。

-

Intersil推出新款HD-SDI发射器和接收器2014-06-24 1665

-

基于FPGA的HD-SDI到SD-SDI变换该怎么实现?2019-10-16 1371

-

hd-sdi接口转u***/csi接口2020-04-17 4337

-

怎么实现基于FPGA的3G/HD/SD-SDI信号光纤传输系统的设计?2021-05-20 2405

-

怎么设计一种基于HD-SDI技术的高清图像处理系统?2021-06-01 1882

-

FPGA的HD-SDI下变换研究2012-02-08 665

-

浅谈HD-SDI传输中芯片技术的具体应用2012-12-21 4205

-

HD-SDI光端机方案2016-11-05 1501

-

汉邦HD-SDI高清摄像机2016-12-29 1136

-

基于HD-SDI技术的高清图像处理系统设计2018-01-22 2857

-

HD-SDI高清矩阵,监控系统的主角2020-04-03 1446

-

hd-sdi转hdmi转换器常见故障有哪些2020-04-21 4298

-

HD-SDI监控系统与IP高清监控系统的区别2020-05-16 1384

-

hd-sdi转hdmi转换器产品规格参数及接口的介绍2020-12-26 1875

-

LCC262 SDI高清视频采集编码卡(H264编码)2023-05-26 799

全部0条评论

快来发表一下你的评论吧 !