ESD断路过压保护,ESD产生的高压和高峰值电流会损坏IC

描述

ESD断路过压保护

在安装于印刷电路板之前,必须对线性IC(如运算放大器、仪表放大器和数据转换器)进行保护。这即所谓断路(out-of-circuit)状态。在这种条件下,IC可能遇到多大的浪涌电压完全取决于其环境。多数情况下,有害的浪涌电压来自静电放电,即常说的ESD。这是一种单次、快速、高电流的静电荷传输现象,源于两种条件,它们是:

* 两个处于不同电位的物体之间的直接接触传输(有时称为接触放电)* 两个物体靠近时之间产生的高静电场(有时称为气隙放电)。

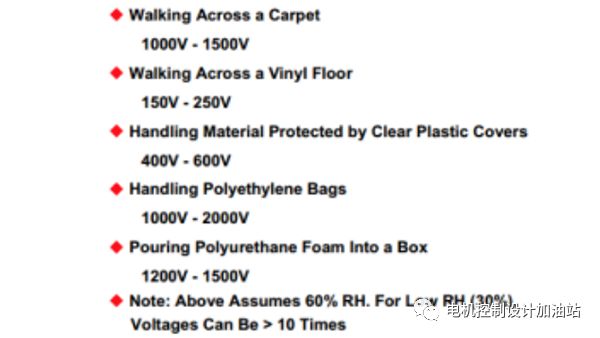

静电的主要来源基本都是绝缘器并且一般都是合成材料,如乙烯或塑料工作表面、绝缘鞋、经过表面加工的木质椅子、透明胶带、气泡袋、尖端未接地的烙铁等。这些来源产生的电平极高,因为它们的电荷并不容易分布在表面上或者传导给其他物体。两个物体相互摩擦产生静电被称为摩擦电效应。一些常见行为会产生较大的ESD电压,部分示例见图1。

ESD产生的高压和高峰值电流会损坏IC。

精密模拟电路通常具有极低的偏置电流,比普通数字电路更容易遭到损坏,因为用于ESD保护的传统输入保护结构会增加输入泄漏——因此不能使用。

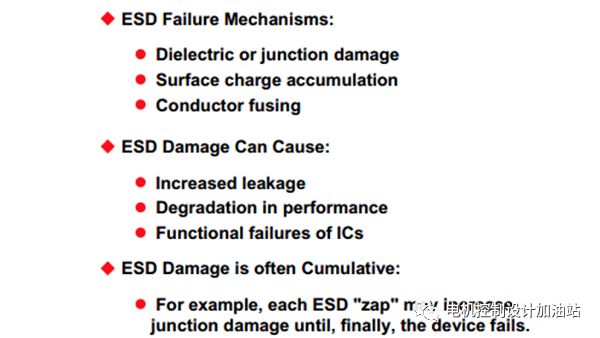

对于设计工程师或技师来说,ESD损坏最常见的表现是IC发生灾难性故障。然而,暴露在ESD之下也可能导致泄漏增加,或者使其他参数下降。如果某个器件在评估期间似乎达不到数据手册上的规格指标,则应考虑ESD损坏的可能性。图2列出了ESD引起的故障的一些相关点。

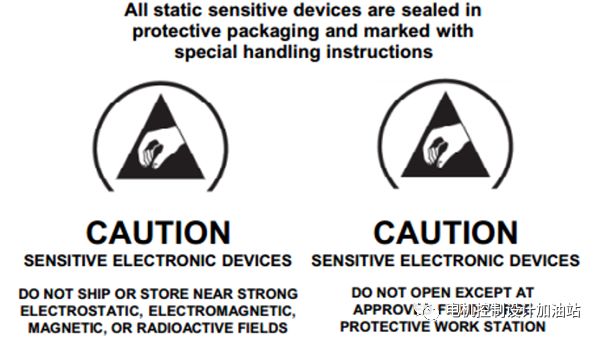

所有ESD敏感器件均采用保护性封装。IC通常装在导电泡沫中或者防静电包装套管中,而后将容器密封在一个静电耗散塑料袋中。密封后的塑料袋用一个明显的标签标好(如图3所示),标签上标明正确的操作程序。

如图3所示外部封装说明旨在告知用户,必须遵循ESD保护所需要的操作程序。

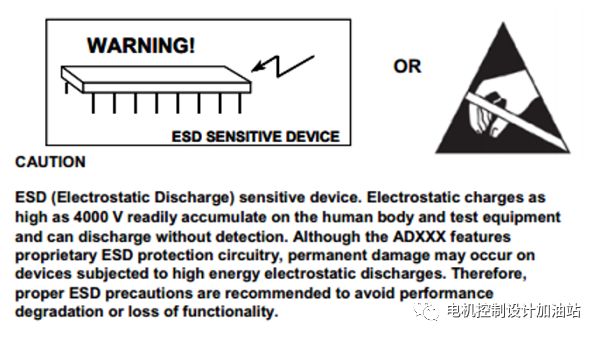

另外,ESD敏感型IC的数据手册都有一条醒目的声明,如图4所示。

一旦识别出ESD敏感型器件,保护起来就相对容易些。很明显,首先应尽量把IC保存在原来的保护性封装中。下一步是给存在破坏可能性的ESD源放电,以防患于未然。这种电压放电可以通过高阻抗快速而安全地实施。

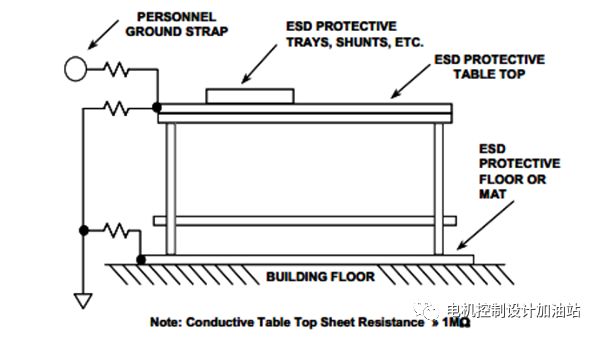

ESD安全IC操作需要的一个关键组件是一个具有静电耗散表面的工作台,如图5所示。其表面通过一个1MΩ电阻接地,可以耗散任何静电荷,同时还能保护用户,免除接地故障电击危险。如果现有的工作台顶部不导电,则应添加一块静电耗散垫和一个放电电阻。

请注意,工作台的表面具有较高的薄膜电阻。工作表面不需要,也不适合使用低阻表面材料(如铜箔PC板)。请记住,如果通过低阻抗释放IC电荷,则可能产生高峰值电流。这正是带电IC接触接地铜箔板时发生的情况。然而,当将同一个带电IC放在如图5所示高阻抗表面时,峰值电流不足以损坏器件。

对于减少ESD相关损坏,有几点人员操作技巧是至关重要的。在工作台时,建议在操作ESD敏感型器件时带上一个导电手环。手环可以确保正常的任务(如从包装上撕下胶带)不会导致IC损坏。另外,出于安全考虑,需用一个1MΩ的电阻从手环接地。在构建原型实验板或者装配含有ESD敏感型IC的PC板时,应在IC之前插入和焊接全部无源元件。结果将降低敏感型器件的ESD风险。当然,烙铁尖需要接地。

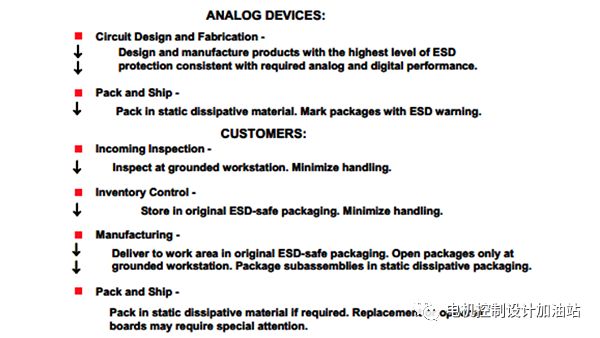

保护IC、使其免受ESD影响需要IC制造商和客户的共同参与。对IC制造商来说,为其产品提供最高水平的ESD保护是其既得利益。IC电路设计师、工艺工程师、封装专家和其他人则不断探索,试图找到更好的新型电路设计、工艺和封装方法以承受或分流ESD能量。然而,完整的ESD保护方案不仅仅需要在IC中内置ESD保护机制。IC用户也需要为其员工提供必要知识和培训,使其了解和遵守ESD操作程序,从而在整个过程的各个关键环节都建立起有效的保护,如图6所示。

在构建实验板以及评估IC时,需要特别小心。ESD损坏可能具有累加效应,因此,如果器件反复操作不当,结果可能导致故障。在试验插座上插入和移除IC时、评估期间存储器件时以及在实验板上添加或移除外部元件时,均须遵循适当的ESD预防措施。同样,如果器件在原型系统开发期间发生故障,其原因可能是不断反复的ESD应力。

对于ESD,需要记住一个关键词:预防。ESD损坏一旦发生则无法挽回,也无法补偿。

ESD模型和测试

有些应用对ESD的敏感度高于其他应用。位于PC板上且周围有其他电路的IC遭受ESD损坏的可能性一般远远小于那些必须与其他PC板或外部世界接口的电路。这些IC一般没有任何特定ESD保护的额定规格,也不提供此类保证(MIL-STD-883方法3015类器件除外)。ESD敏感型接口的一个良好示例是计算机上的RS-232接口端口IC,该IC很容易暴露在高电压之下。为了保证此类器件的ESD性能,必须指定测试方法和限制。

人们提出了多种测试波形和规格,用以评估器件对ESD的敏感性。半导体或分立式器件目前仍在使用的最重要的三种波形为:人体模型(HBM)、机器模型(MM)和充电器件模型(CDM)。每一种模型均代表着一种完全不同的ESD事件,因此,这些模型的测试结果之间的相关性很小。

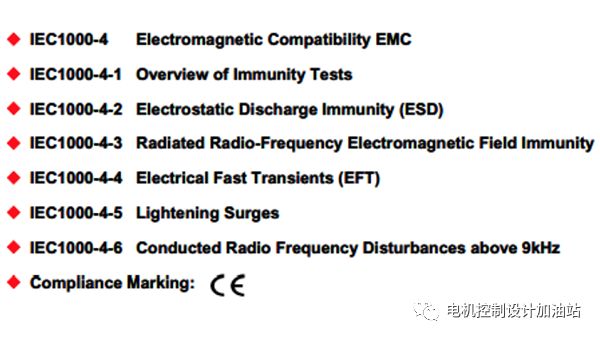

1996年以来,销往欧共体或者在欧共体内部销售的所有电子设备都必须达到IEC1000-4-x规范中规定的电磁兼容性(EMC)等级。请注意,这并不适用于单片IC,而是适用于最终设备。各种IEC1000规范规定了此类标准和测试方法,详见图7。

IEC1000-4-2规定,合规测试要使用两种耦合方法,即接触放电和气隙放电。接触放电要求直接连接测试的装置。气隙放电使用更高的测试电压,但不会直接接触测试的装置。在气隙放电法下,放电枪朝向测试装置移动,在整个气隙上形成一道弧,气隙放电即由此而来。这种方法受湿度、温度、气压、距离和放电枪逼近速率的影响。接触放电法虽然现实性较低,但具有更高的可重复性,其应用呈现出赶超气隙放电法之势。

虽然ESD脉冲含有的能量极少,但极快的上升时间和高电压却可能给未受保护的IC带来故障。电弧或热效应可能立即给器件带来灾难性损坏。即使灾难性故障不会立即发生,器件的参数也可能下降,结果会降低性能。连续暴露具有累积效应,可能最终导致器件完全失效。

I/O线路尤其容易遭到ESD损坏。即使是简单地接触一下,或者是插入一条I-O线缆,也可能导致静电放电,结果可能损坏或完全损毁与I/O端口相连的接口产品(如RS-232线路驱动器和接收器)。

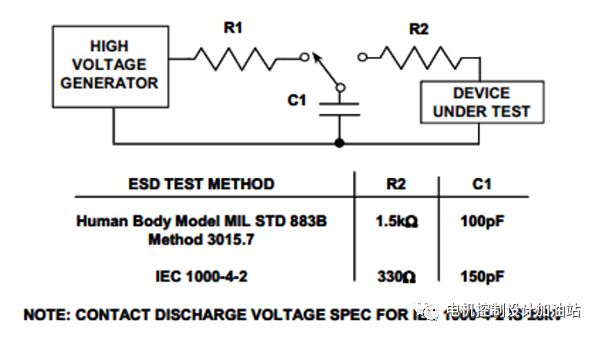

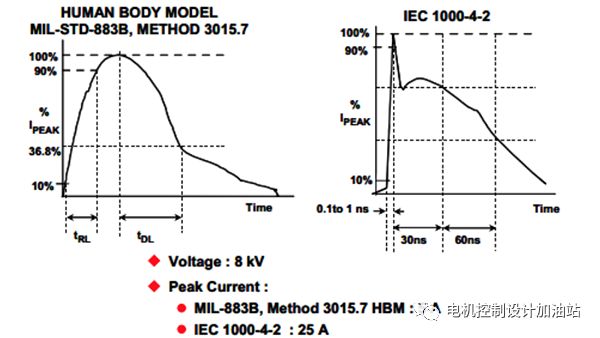

传统的ESD测试方法(如MIL-STD-883B方法3015.7)并不会全面测试产品对这种放电的敏感性。该测试方法旨在测试产品在操作期间遭受ESD损坏的可能性。每个引脚都是相对于所有其他引脚进行测试的。MIL-STD-883B方法3015.7测试与IEC测试之间存在重要差异,如下所示:

IEC测试在放电能量方面要求更严格。注入的峰值电流大四倍以上。在IEC测试中,电流上升时间明显更快。IEC测试是在器件带电期间进行的。ESD放电有可能导致测试器件闩锁。因此,该测试更能代表现实I-O放电,因为设备一般都是带电运行的。然而,保险起见,应该对接口器件进行这两种测试,以确保操作期间以及随后的现场维修期间,器件均能获得最大程度的保护。

图8比较了IEC1000-4-2模型与MIL-STD-883B方法3015.7人体模型的测试电路值。

MIL-STD-883B方法3015.7和IEC1000-4-2两种测试的ESD波形分别列于图9的左右两栏。

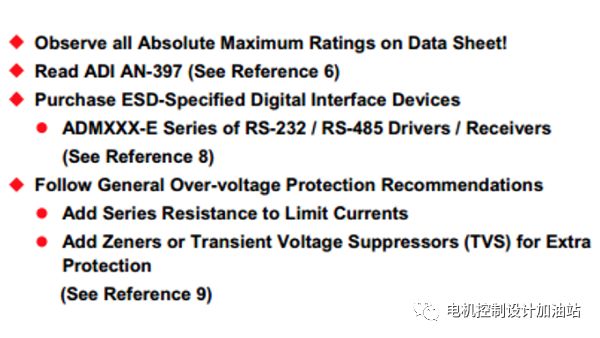

适用的ESD保护设计措施实现起来相对容易,本节已讨论过的多数过压保护方法都有用。也可以获得额外的保护措施。对于RS-232和RS-485驱动器和接收器,ADMXXX-E系列提供15kV(HBM)ESD担保规格。对于更通用的应用,在系统适当位置增加TransZorb保护电路也可提供ESD保护功能。

图10从断路和在线两个角度总结了ESD预防的要点。

-

ESD保护策略解析2010-08-18 3790

-

ESD损坏PCB板的原理分析2013-12-25 3295

-

什么是ESD(静电放电)及ESD保护电路的设计2016-07-22 4287

-

电子器件的ESD静电保护2018-01-16 7115

-

ESD静电保护器件的特点2018-01-26 4796

-

ESD(静电放电)介绍及ESD保护电路的设计2018-10-11 6188

-

ESD保护管2018-10-17 4053

-

汽车模块中ESD保护解决问题2018-10-25 1972

-

NFC天线的ESD保护组件2019-06-13 1937

-

用于电力线浪涌保护的高峰值电流 ESD 二极管2020-05-08 943

-

ESD静电放电产生的原理和危害2021-01-06 1904

-

晶闸管断路过压保护电路图2009-05-06 1389

-

静电放电(ESD)断路过压保护说明2021-03-22 1127

-

I/O端口的ESD保护2023-03-28 6604

-

ESD断路过压保护指南2023-11-29 333

全部0条评论

快来发表一下你的评论吧 !