基于ZU+系列MPSoC芯片的USB3.0/2.0接口硬件设计

嵌入式技术

描述

本文主要介绍Zynq UltraScale + MPSoC系列芯片的USB3.0/2.0接口硬件设计。

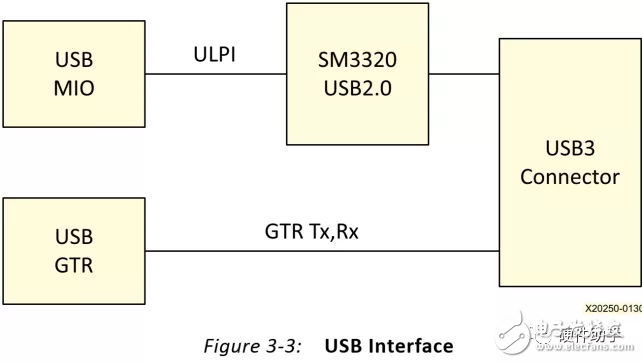

ZU+系列MPSoC要实现USB3.0/2.0的全部功能,需要同时使用MIO和GTR。因为GTR接口中的USB接口只支持USB3.0,对USB2.0的支持需要通过MIO接口外接USB PHY实现。

ZU+系列MPSoC包括两个USB接口,根据实际需要可以进行如下表所示的配置:

当USB接口配置成3.0模式时,USB2.0也必须使能(在SDK的PCW配置界面),因为外部VBUS有效的反馈信号只能从USB PHY的ULPI接口得到。在非OTG模式下,VBUS信号也可以通过PL侧信号得到,但只能通过命令的方式获得。反之,USB2.0则可以单独使用。

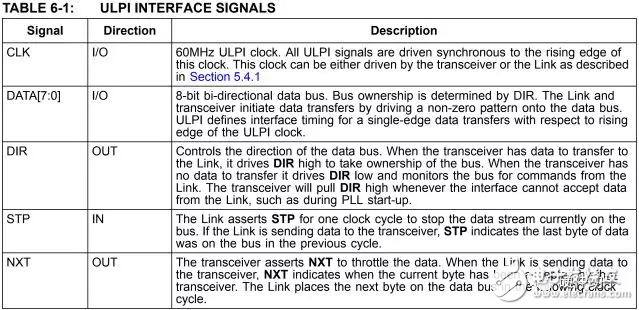

MIO侧的USB2.0接口只支持ULPI接口,关于ULPI的更多信息可参考之前的文章《USB系列之“外部PHY接口”》,PHY芯片可以选择和官方开发板一样的USB3320(也可以选择其他支持ULPI接口,且接口电压为1.8V的PHY芯片)。

USB3320和ZU+的连接关系如下:

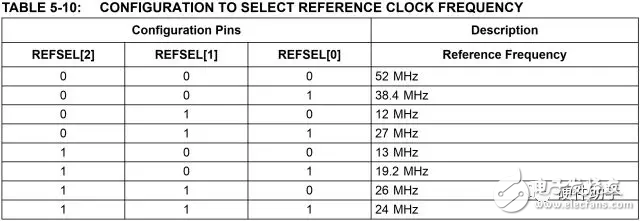

USB3320的外部时钟输入可以配置,通过REFSEL[2..0]上下拉实现。时钟输出固定为60MHz,通过CLKOUT引脚输出,给到Link端。USB3320支持同步和异步两种传输模式,当采用同步传输时,使用SDR模式,所有的数据都是在CLK的上升沿同步传输;当采用异步模式时,CLK关闭。数据总线的方向通过DIR控制,如果两端都不驱动数据总线时,DIR的改变将产生“turn-around” cycle。

USB3320的外部时钟配置选择如下:

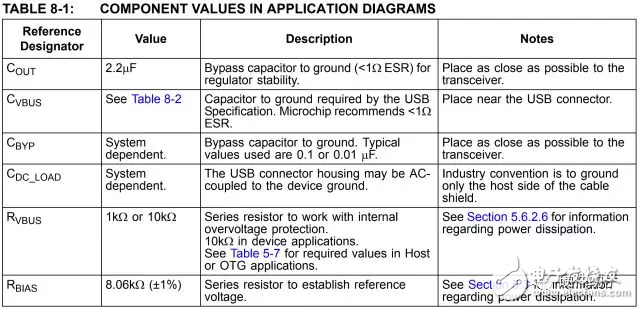

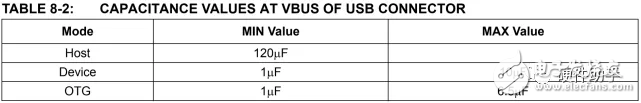

USB3320的电源去耦电容、偏置电阻要求如下:

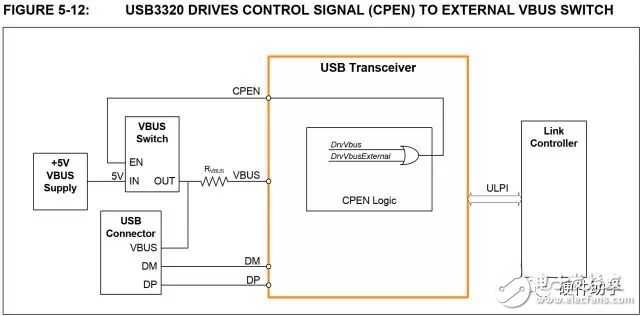

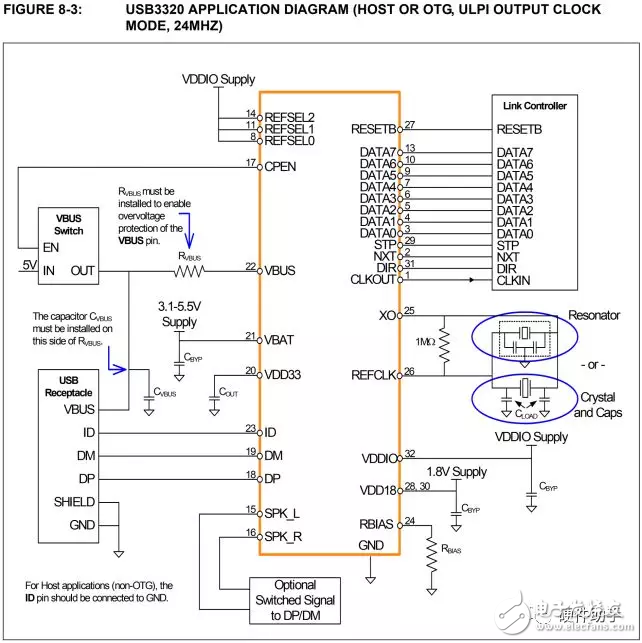

USB3320的连接示意图如下:

其中,ID引脚可以根据实际应用需求固定死(为高时ZU+作为DEVICE,为低时ZU+作为HOST)。

最后,针对PCB设计,为了阻抗匹配,在设计过程中注意以下几点:

PCB and package delays should be kept to 1.30 ns or below.

PCB and package delay skews for DATA[7:0]/DIR/NXT/STP and CLK should be within ±100 ps.

For optimum signal integrity, add a 30Ω series resistor to the DATA and STP lines near the Zynq UltraScale+ MPSoC.(对于NXT、DIR和CLK,对于Link端是输入,不能在末端串联电阻匹配)

-

USB3.0和USB2.02011-11-22 14738

-

USB2.0与USB3.0接口的PCB布局布线要求2023-08-17 6536

-

ZU+系列MPSoC的外围接口详细分析2020-12-26 6421

-

USB3.0知识扫盲 u***3.0和2.0的区别详解2012-11-07 20591

-

fx3 USB3.0翻译USB2.02018-10-10 2320

-

MPSoC可扩展集成电源参考设计包括BOM及框图2018-10-25 2507

-

USB2.0/USB3.0接口与eSATA对比2010-03-25 4707

-

USB3.0芯片速度测试比较2011-01-01 8321

-

USB 3.2接口的特征, USB 3.0和USB 2.0的区别2018-05-31 89193

-

USB3.0与USB2.0速度、工作原理的对比2019-01-06 36169

-

USB3.0和USB2.0有什么区别USB3.0接口定义的详细资料说明2019-12-18 4583

-

USB3.0接口和USB2.0接口在功耗等方面的比较2021-11-20 7797

-

什么是USB3.0?usb3.0与usb2.0有什么区别?2023-10-27 12623

-

USB3.0如何辨别2023-11-07 3637

-

usb3.0和2.0的!!!2024-04-07 3096

全部0条评论

快来发表一下你的评论吧 !