基于电路分割技术的查表法实现根升余弦脉冲成形滤波器FPGA设计

可编程逻辑

描述

0 引言

数字通信系统中,基带信号的频谱一般较宽,因此传递前需对信号进行成形处理,以改善其频谱特性,使得在消除码间干扰与达到最佳检测接收的前提下,提高信道的频带利用率。目前,数字系统中常使用的波形成形滤波器有平方根升余弦滤波器、高斯滤波器等。设计方法有卷积法或查表法,其中:卷积法的实现,需要消耗大量的乘法器与加法器,以构成具有一定延时的流水线结构。为降低硬件消耗,文献提出了一种分布式算法(Distributed Arithmetic,DA)的滤波器设计结构。它将传统的乘、累加运算转化为移位、累加运算,当运算数据的字宽较小时,极大地降低了硬件电路的复杂度,提高了响应速度;当运算数据的字长较长时,因其需要更多的移位迭代运算而不适合高速处理的需求。为此,文献提出了采用滤波器的多相结构与改进DA算法相结合的一种设计方法。当考虑ISI码元数目较多时,该设计所需要的ROM表个数就会增多,同时访问ROM所需的地址的产生电路就会变得更为复杂。文献提出了采用存储器分割技术,可以降低ROM单元的数量,但是它是以增加系统的复杂性与响应时延、信号毛刺为代价的。文献在滤波器设计时采用了CSD编码,虽然减少了乘法运算,但是需要设计CSD编解码电路。

文中论述的是二进制基带信号的连续查表法平方根升余弦波形成形滤波器(SRRC)的FPGA实现(滚降系数取0.22),取冲击响应截断时间为8T,每T内样点数为8个,所用ROM单元数为2(8+3),每单元数据为16 b有符号整型数。查找ROM表所需11 b的地址由一个长8 b的数据移位寄存器与一个模8的采样时钟计数器链接而成。给出了设计在Modelsim 6.3下的时域仿真波形,经与理论相比较,文中的设计方法是可行的,且当二进制码元的码间干扰数增多(码间样点增加)时,地址电路简单增长即可(不影响响应时间),便于FPGA的实现。

1 二进制基带信号平方根升余弦成形原理

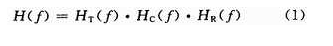

实际系统中,广义信道传递函数H(f)由发送滤波器HT(f)、信道HC(f)、接收滤波器HR(f)三部分共同构成,即:

根据乃奎斯特第一准则,当H(f)幅频特性满足的滚降系数为α升余弦滤波器特征时,可以实现无ISI传输时刻降低对采样时钟精度的要求,当信道噪声可以忽略时,取HC(f)≈1,按照接收滤渡器的输出信噪比最大准则,有:

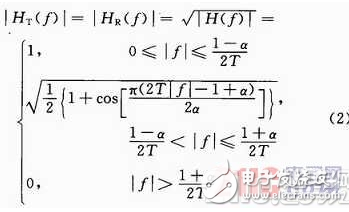

式中:T为输入码元的周期;α为滚降系数。记f0=1/(2T),由式(2)可推出滚降系数为α平方根升余弦冲击响应为:

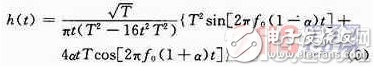

其时域响应如图1所示。在数字化波形成形时,为确保h(t)采样后的h[n]保持第一类线性相位,舍去h(t)|t=0样点,同时对N(偶数)点h[n]右移N/2。文中采用的h(t)中t∈[-4T,4T],采样间隔为T/8,于是,采样后根升余弦成形滤波器的64个归一化h[n]如表1 所示。

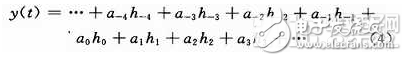

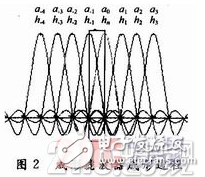

设发送端传递的二进制数据是{…,a-4,a-3,a-2,a-1,a0,a1,a2,a3,a4,a5,…},则发送滤波器的输出如图2所示,该波形函数可表示为:

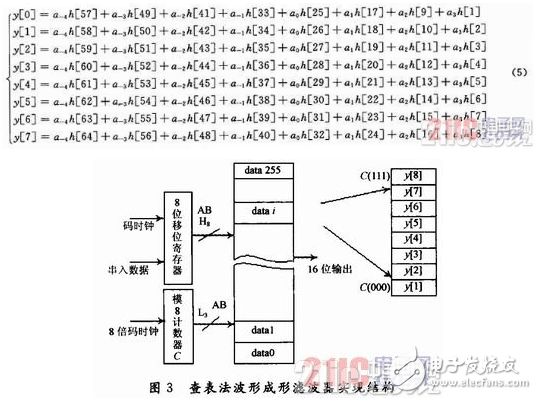

可以看出,当前传递信息{a0}时刻对应的波形信号的上升沿y[1..8]分别由h-4[57..64],h-3[49..56],h-2[41..48],h-1[33..40],h0[25..32], h1[17..24],h2[9..16]与h3[1..8]线性表示,如式(5)所示:

2 二进制基带信号平方根升余弦成形滤波器的FPGA实现

在分析文献的基础上,文中波形成形滤波器的实现采用的查表法结构如图3所示。其中,ROM单元存储待成形的数据与成形滤波器的冲击响应的卷积结果。模8计数器的工作时钟速率是待成形数据速率的8倍。待成形数据从8位移位寄存器的低位移入后,选择ROM表中的数据块da-ta i,同时模8计数器C从(000)2~(111)2计数,并用该计数结果C(j)选择输出data i中的y[j]。当计数器C计数归零时,新的待成形数据从低位移入8位移位寄存器。该设计的一个优点是:ROM表中的数据在计算时,ai可采用双极性码,而查找表地址产生电路使用单极性码。文中设计时,波形数据的计算采用了反逻辑、双极性、不归零码,即输入信息符号序列{0,1)映射为{+1,-1),持续时间不变。

2.1 连续查找表法的一种改进实现

由图3不难实现采用本文的波形成形设计方案,共需要的ROM单元数目达2 048个。为此,可采用电路分割技术,将图3所示的8位移位寄存器输出的高8位地址同时给一个11位的中间寄存器,该中间寄存器的高8位又分为高4位与低4位,分别用于查找两个各具有16个单元的ROM表,之后再将各自的输出相加,此时消耗的ROM单元数共为256个。采用分割技术时,模8计数器、中间寄存器、ROM表三个部分的工作时钟相同。

2.2 根升余弦成形滤波器的VHDL实现

文中所述滤波器是在Modelsim 6.3d环境下采用VHDL实现的。Quarts环境中以文本方式调用LPM_ROM宏功能模块,定制ROM元件data_ rom_16,元件的地址宽度分别是4 b,输出数据字宽同为15 b。加法器的输出字宽16 b。实现的部分VHDL代码如下:

2.3 Modelsim时序仿真结果

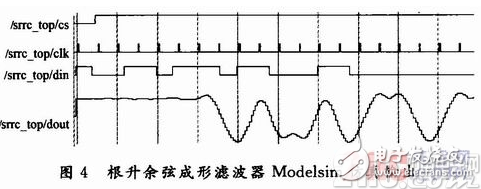

Modelsim环境不能直接对mif格式的ROM初始化数据进行仿真,应在QuartsⅡ环境下先打开mif文件,再另存为hex格式,然后在Modelsim环境下编译后即可仿真。同时,如此操作又可将负值数据转为补码表示。Modelsim仿真结果如图4所示,其中clk的周期为160 ns,正好是一个din码元的宽度T,系统中地址产生电路的时钟周期是20 ns,以确保在一个码元持续时间内系统有8个样点输出。从图4中发现,一个码元成形后波形值延迟6T。

3 结论

文中所述的基于电路分割技术的查表法,实现通信系统发送端根升余弦滚降成形滤波器的FPGA实现方法简单可行,且当截断码元数目增多时或码内样点数目增加时,仅通过改变地址移位寄存器的长度或计数器的长度与ROM的长度即可,不至于使电路的复杂度成倍增加。

-

刘着过年

2019-03-18

0 回复 举报不错哦 收起回复

刘着过年

2019-03-18

0 回复 举报不错哦 收起回复

-

实现一组二进制数据通过根升余弦滤波器后的波形的实验工程文件2021-03-11 724

-

WCDMA上下行链路中平方根升余弦滤波器的设计与实现2020-11-28 9546

-

基于FPGA器件FLEX10k30A实现成形滤波器的设计2020-09-24 1534

-

fdatool设计升余弦滤波器阶数2019-08-27 2869

-

如何利用3G移动通信中脉冲成形FIR滤波器实现ASIC?2019-08-02 1142

-

平方根升余弦滤波器在simulink中模块参数怎么设置?2019-07-18 6546

-

labview如何设计一个升余弦FIR滤波器2014-01-16 3292

-

求助 高斯脉冲成形滤波器2013-04-11 4624

-

基带信号QPSK调制与脉冲成型滤波器ASIC实现2011-08-13 11357

-

根余弦滤波器(Root-raised cosine filt2009-11-22 1001

-

基于Xtensa LX处理器实现RRC滤波器设计2009-11-21 931

-

基于多速率DA的根升余弦滤波器的FPGA实现2009-11-13 1938

-

什么是滚降系数?为什么要采用脉冲成形滤波器?2008-05-30 25932

全部0条评论

快来发表一下你的评论吧 !