一起看看“神器”究竟都有哪些?

电子说

描述

Hello!Everybody!今天陆妹给大家带来了三款神器,是我们EDA365特邀版主自主开发的哦。版主老师们不仅有着大咖的段位、浑身使不完的超强电子硬件技术能力,同时还有着一颗“造福”于工程师们的大爱之心,德玛西亚万岁!

一起看看“神器”究竟都有哪些?(工具1——毛老师提供;工具2——杜老师提供;工具3——贾老师提供。)

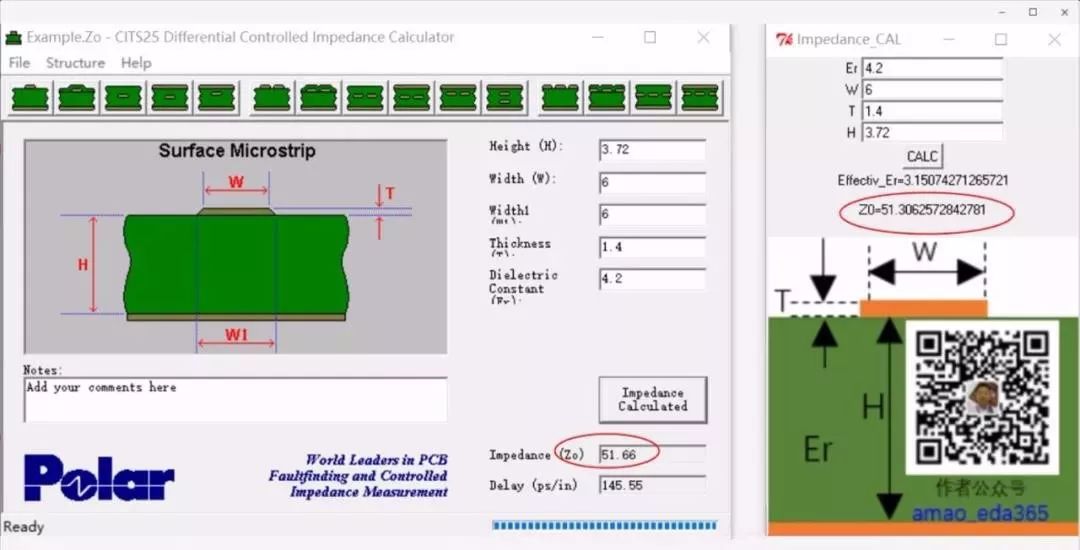

01微带线阻抗计算小工具

微带线阻抗计算(小工具)的结果与专业软件POLAR在相同输入条件下算出的结果进行比较:二者的阻抗结果居然小于1Ohm(51.66---51.30)!!!(其它不同数据组合精度会有差异,带状线的计算太易这个版本先不加)。

结果比较:

上图小工具除可以提供微带线的准确计算外,还提给供了有效介电常,这个非常重要。

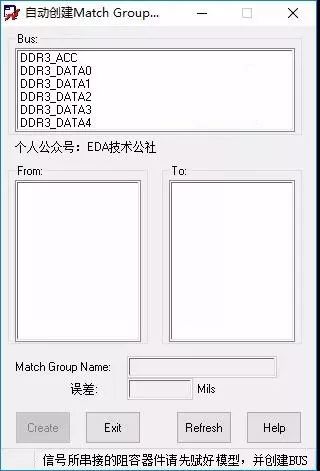

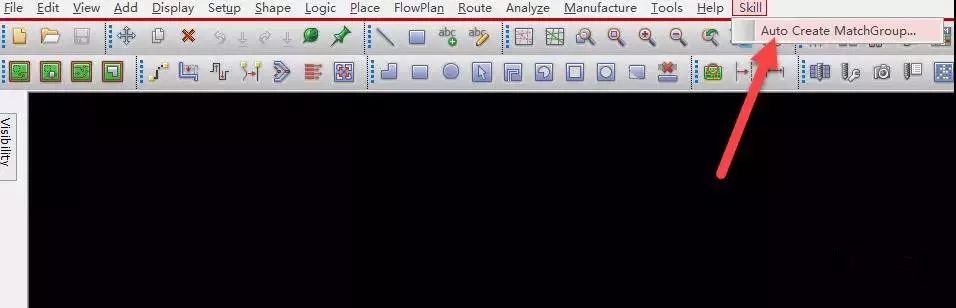

02等长约束破解篇

众(wu)所(zhi)周(wu)知(wei),对于数字信号通常要做时序控制,让同步信号能在彼此约定的时间内同时到达目的地。尤其是在设计高速PCB时,为了满足日益严格的时序要求,通常会对这些同步信号设置等长约束,使其电气长度相互接近。

对于攻城狮而言,简单的点到点结构的同步信号,设置等长约束非常easy。But,对于有4、6、8、、、等多颗DDR芯片的ACC同步信号来说,要设置等长约束简直就是一场噩梦,不仅信号数量较多,而且拓扑结构十分复杂(如下图)。

对于多负载的信号来说,在Allegro中通常有两种令攻城狮们喜闻乐见的等长设置方法:【拓扑模版法】&【手工创建PinPair法】。但这两种方法都有着说不尽的心酸,所以今天给大家分享一个插(niu)件(bi)神器:

1

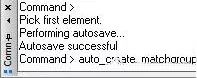

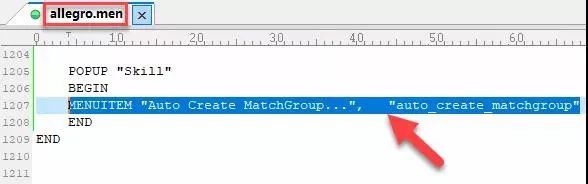

【程序加载方法】

(1)

将作者免费提供的Auto_Create_Match_Group.il文件复制到Home\PCBENV目录下(Home为系统环境变量);

(2)

编辑Home\PCBENV目录下的allegro.ilinit文件(如无此文件,可新建文本文件,更名之),添加一行加载语句(建议按原文复制过去):loadi("./Auto_Create_Match_Group.il","dzkcool");

(3)

重启Allegro软件,在命令栏输入:auto_create_matchgroup;

(4)

有能力的小伙伴还可以修改Allegro的菜单文件allegro.men,添加菜单命令(菜单文件修改需谨慎,注意提前做好备份);

(5)

这样就可以愉快的直接使用菜单命令了。

2

【程序使用说明】

(1)

将需要设置相对延时等长约束的同步总线创建到一个Netgroup或Bus中;

(2)

如果信号线上有串接的阻容器件(并联的不用管),需事先赋好模型,再创建Netgroup或Bus;

(3)

在插件程序中选择Bus后,再在From和To中分别选择起始点,设置好等长误差(默认为mil单位),单击Create后即可;

(4)

同一个Bus的多个负载可以在前一个MatchGroup单击Create后,直接选择新的负载,再次单击Create就能快速创建;

(5)

注意,本程序暂时不支持带T点的信号,使用前需清除信号上的T点,此问题将在下一版解决。

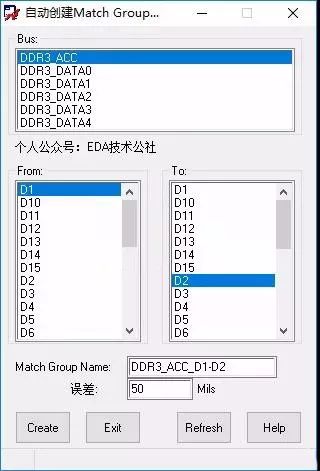

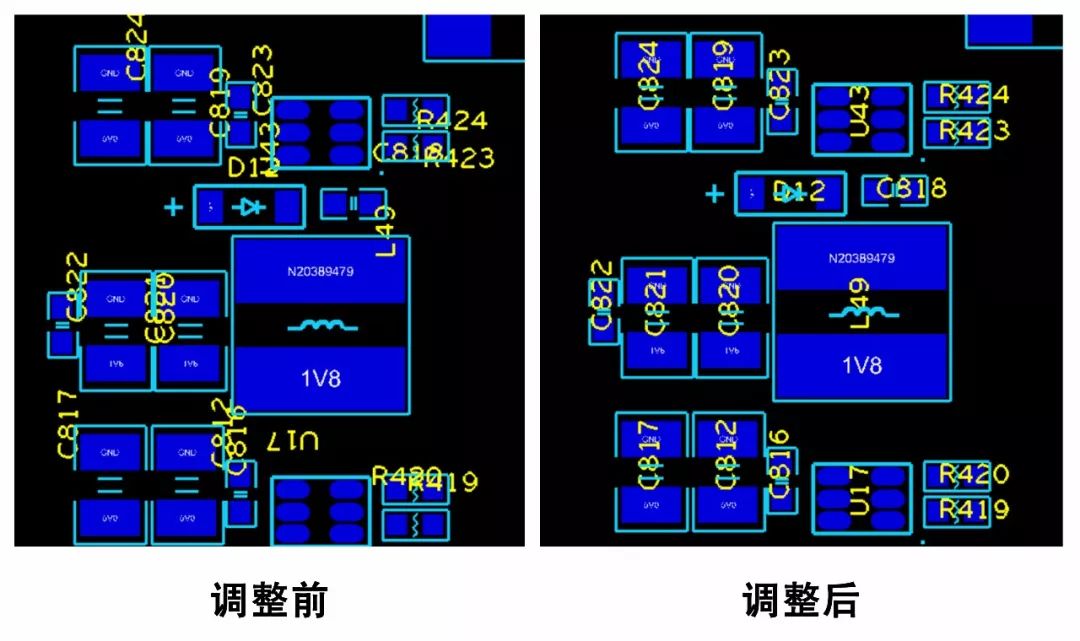

03丝印方向及位置调整

【痛点】

通常在后处理调整丝印时,Allegro Layout往往需要逐个调整丝印方向和位置,简单而机械的动作,需要耗费大量时间。由于人为操作,也很容易出现丝印交错现象,以致于设计完的PCB板出现严重质量问题。

接下来我们通过SKILL程序来解决这个问题,无论多复杂的PCB板,一个”click“,就已调整好方向,并整齐地摆放于丝印框内。

【功能】

1、调整顶层和底层的丝印方向,并放置于器件丝印框内;

2、顶层丝印按从左至右,从下至上摆放;底层丝印按从右至左、从下至上摆放。

【应用】

1、打开丝印未调整的Allegro brd文件;

2、将“ref.il”程序文件(见附件)放置到brd文件同目录下;

3、在Allegro命令窗口,输入:(load "ref.il")加载程序,将返回:t,然后输入:(ref)执行丝印调整命令;

4、检查丝印——原来混乱的丝印,已调整好方向,并放置于器件丝印框内。其后,仅需将丝印成组移到合适的位置。

-

一起进步2011-03-23 3025

-

和好友一起创建相册的正确方式2016-05-20 6558

-

一起探讨一下这个可行?2016-05-30 3952

-

为什么GND跟地线连在一起?2017-06-07 10994

-

Molex莫仕就“未来汽车”发布全球汽车调研结果,一起来看看都有什么内容吧!!2021-01-07 49175

-

中兴V5手机配置如何?我们一起来看看吧!2017-03-24 2692

-

坚果R1拆解 内部设计究竟如何2018-10-29 5388

-

海思究竟做了多少芯片呢?一起看看吧!2020-09-10 4275

-

智慧灯杆新标准出台,一起看看这其中都有哪些内容2020-11-30 1270

-

一起看看镗孔究竟应如何加工2020-11-04 4907

-

从万能充到嵌入式,大家一起看看手机电池的“进化之路”吧2021-03-17 4734

-

如何利用土壤采样器如何提取土壤溶液,一起来看看2021-05-17 3547

-

十种常用电子元器件一起看看都有哪些?2021-12-27 13796

-

与Arduino一起使用Relay2022-11-08 950

-

MOS管究竟是什么,三个级怎么判定2022-12-08 5931

全部0条评论

快来发表一下你的评论吧 !