dma控制器的组成

电子说

描述

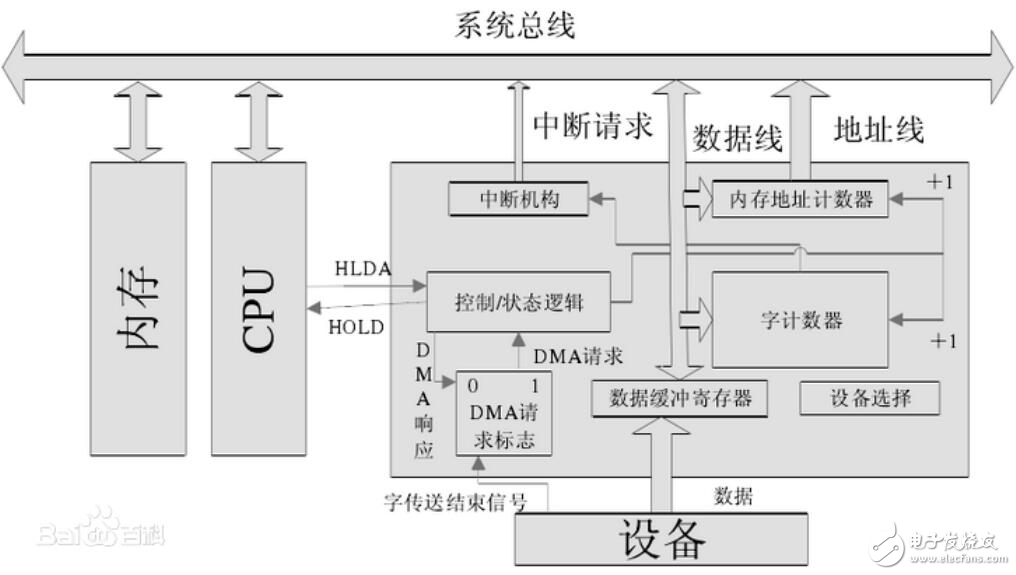

一个DMA控制器,实际上是采用DMA方式的外围设备与系统总线之间的接口电路,这个接口电路是在中断接口的基础上再加DMA机构组成。习惯上将DMA方式的接口电路称为DMA控制器。

(1)内存地址计数器:用于存放内存中要交换的数据的地址。在 DMA传送前,须通过程序将数据在内存中的起始位置(首地址)送到内存地址计数器。而当 DMA 传送时,每交换一次数据,将地址计数器加“1”,从而以增量方式给出内存中要交换的一批数据的地址。

(2)字计数器:用于记录传送数据块的长度(多少字数)。其内容也是在数据传送之前由程序预置,交换的字数通常以补码形式表示。在DMA传送时,每传送一个字,字计数器就加“1”。当计数器溢出即最高位产生进位时,表示这批数据传送完毕,于是引起DMA控制器向CPU发出中断信号。

(3)数据缓冲寄存器:用于暂存每次传送的数据(一个字)。当输入时,由设备(如磁盘)送往数据缓冲寄存器,再由缓冲寄存器通过数据总线送到内存。反之,输出时,由内存通过数据总线送到数据缓冲寄存器,然后再送到设备。

(4)DMA请求”标志:每当设备准备好一个数据字后给出一个控制信号,使“DMA请求”标志置“1”。该标志置位后向“控制/状态”逻辑发出DMA请求,后者又向CPU发出总线使用权的请求(HOLD),CPU响应此请求后发回响应信号HLDA,“控制/状态”逻辑接收此信号后发出DMA响应信号,使“DMA 请求”标志复位,为交换下一个字做好准备。

(5)控制/状态”逻辑:由控制和时序电路以及状态标志等组成,用于修改内存地址计数器和字计数器,指定传送类型(输入或输出),并对“DMA请求”信号和CPU响应信号进行协调和同步。

(6)中断机构:当字计数器溢出时,意味着一组数据交换完毕,由溢出信号触发中断机构,向CPU提出中断报告。

-

请问DMA控制器可以减轻CPU负担吗?2024-03-28 1940

-

AN4104_STM32F0xx的DMA控制器的使用2022-11-21 602

-

ZYNQ开发案例之DMA控制器系统设计2020-12-05 5525

-

dma控制器是什么_dma控制器工作方式2019-11-15 14365

-

NiosⅡ系统中DMA控制器的原理及应用2017-12-07 3213

-

基于AMBA总线的DMA控制器IP核设计2017-12-06 4508

-

DMA控制器功能及特点2017-09-19 1690

-

基于DMA控制器的UART串行通信设计2012-04-20 1404

-

适应多种时序的DMA控制器设计2011-03-26 3963

全部0条评论

快来发表一下你的评论吧 !