在设计低功耗同步解调器时需要注意的事项

描述

简介

“同步检波器助力精密低电平测量,” 一文刊于2014年11月的《模拟对话》杂志,该文讨论了存在相对较高噪声电平情况下使用同步解调测量低电平信号的优势。本文讨论在严格的功耗和成本限制系统中使用同步解调进行传感器信号调理时的一些设计考虑因素,进一步深入该话题。经仔细设计后,模拟系统在简洁性、低成本和低功耗方面将会是无与伦比的。该架构将在模拟域中执行大部分信号处理。

传感器激励

传感器随处可见,它们用来测量温度、光照、声音和其他各种环境参数。一些传感器的输出电压或电流取决于某些物理参数。例如,热电偶产生与参考结点和测量点之间温度差成比例的电压。大部分传感器的传递函数相对于物理参数遵循已知的关系。传递函数通常是一个阻抗,电流是传感器输入,而传感器两端的电压表示目标参数。阻性传感器(比如称重传感器、RTD和电位计)分别用来测量应力、温度和角度。就一阶而言,阻性传感器与频率无关,并且没有相位响应。

很多传感器因为它们的传递函数随频率和相位改变,所以要求使用交流激励信号。这样的例子有感性近距离传感器和容性湿度传感器。生物阻抗测量可以获取有关呼吸率、脉搏率、水合作用和其他各种生理参数。这些情况下,幅度、相位(或两者)都可用来确定检测参数的数值。

在某些应用中,传感器可以把待测样本转换成感应器。例如,色度计使用LED将光线照射穿过待测液体样本。样本的光吸收调制光电二极管检测的光量,以便揭示待测液体的特性。血氧含量可以通过测量血管组织中的红光和红外光吸收之差来确定。超声传感器根据超声在气体中行进的多普勒频移来测量气流速率。所有这些系统都可以使同步解调来实现。

图1显示的是测量传感器输出信号的同步解调系统。激励信号fx用作载波,传感器以幅度、相位(或两者同时)作为待测参数的函数进行调制。信号可能经过放大和滤波,然后再由相敏检波器(PSD)向下调制,回到直流状态。输出滤波器(OF)将信号带宽限制在待测参数的频率范围内。

传感器输出端的噪声可能受内部源或外部耦合的影响。低频(1/f)噪声经常会限制传感器或测量电子设备的性能。很多传感器还容易受到低频环境噪声的干扰。光学测量容易受到背景光照的影响;电磁传感器容易受到电源辐射的影响。自由选择激励频率以避开噪声源是同步解调的重要优势。

选择一个可以降低这些噪声源影响的激励频率是优化系统性能的重要途径。所选激励频率应当具有较低的噪底,并离开噪声源足够距离,以便适当进行滤波便可将噪声降低至可以接受的水平。传感器激励通常是功耗预算中最大的一块。如果传感器的灵敏度与频率的关系已知,则在灵敏度较高的频率处激励传感器即可降低功耗。

相敏检波器

若要理解抗混叠滤波器(AAF)和OF的要求,则需理解PSD。考虑通过激励信号将输入信号同步扩大+1和–1倍的PSD。这等效于输入信号乘以相同频率的方波。图2a显示的是输入信号、基准电压源和PSD输出的时域波形;图中,输入信号为方波,任意相位与基准电压源相关。

当输入和基准电压完全无相移时,相对相位为0°,开关输出为直流,且PSD输出电压为+1。随着相对相位增加,开关输出成为基准频率两倍的方波,且占空比和均值线性下降。相对相位为90°时,占空比为50%,平均值为0。在180°相对相位处,PSD输出电压为–1。图2b显示了相对相位在0°至360°范围内扫描时的PSD平均输出值,输入信号为方波和正弦波。

正弦波情形没有方波情形那么直观,但可以通过逐项相乘并分解为相加项和相减项而计算,如下所示:

正如预计的那样,PSD在基频处生成与输入信号相对相位的余弦成比例的响应,但它同时也会生成针对信号所有奇次谐波的响应。若将输出滤波器视为相敏检波器的一部分,则信号传输路径看上去就会像是一系列以基准信号奇次谐波为中心的带通滤波器。带通滤波器的带宽由低通输出滤波器的带宽确定。PSD输出响应是这些带通滤波器之和,如图3所示。出现在直流端的响应部分落在输出滤波器的通带内。出现在基准频率偶次谐波的响应部分将由输出滤波器抑制。

乍看之下,谐波的无限求和混叠进入输出滤波器通带,似乎使这种方法失效。然而,由于每一个谐波项都成倍缩小,并且各谐波噪声以平方和的平方根方式相加,噪声混叠的影响得以减轻。假设输入信号的噪声频谱密度不变,那么就可以计算谐波混叠的噪声影响。

使Vn成为以基频为中心的传输窗口的积分噪声。总RMS噪声VT为:

使用简便的公式对几何级数求和:

谐波窗口导致的RMS噪声增加量为:

因此,所有谐波窗口产生的RMS噪声使总噪声仅增加11%(或1dB)。输出依然容易受到带通滤波器的通带波动影响,并且PSD之前的传感器或电子器件谐波失真将导致输出信号产生误差。如果这些谐波失真项过大而无法接受,可以使用抗混叠滤波器使其下降。下一个设计示例中将考虑抗混叠和输出滤波器要求。

LVDT设计示例

图4显示的是一个同步解调电路,该电路可从线性可变位移变压器(LVDT,一种特殊的绕线变压器,具有活动内核,贴在待测位置)提取位置信息。激励信号施加于初级端。次级端电压随内核位置成比例变化。

LVDT的类型有很多,此外提取位置信息的方法也各不相同。该电路采用4线模式LVDT。将两个LVDT的次级输出相连使其电压相反,从而执行减法。当LVDT内核位于零点位置时,次级端上的电压相等,绕组上的电压差为零。随着内核从零点位置开始移动,次级绕组上的电压差也随之增加。LVDT输出电压符号根据方向而改变。本例选择的LVDT测量±2.5 mm满量程内核位移。电压传递函数为0.25,意味着当内核偏离中心2.5 mm时,施加于初级端的每伏特电压的差分输出等于250 mV。

集成式同步解调器

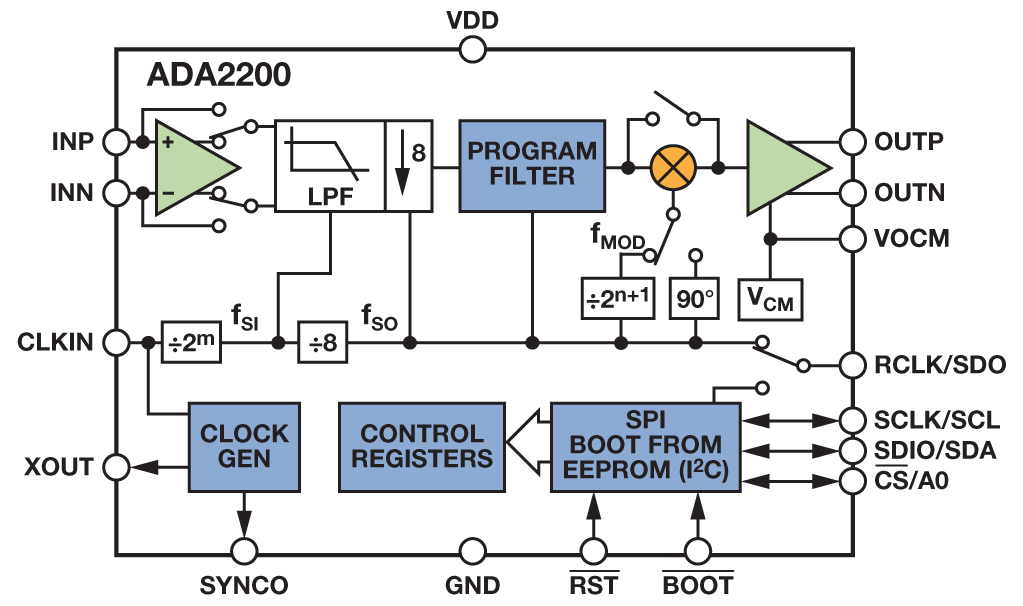

24位Σ-Δ型ADCADA2200集成式同步解调器采用独特的电荷共享技术来执行模拟域内的分立式时间信号处理。该器件的信号路径由输入缓冲器、FIR抽取滤波器(进行抗混叠滤波)、可编程IIR滤波器、相敏检波器以及差分输出缓冲器组成。其时钟生成功能可将激励信号与系统时钟同步。通过SPI兼容接口可配置可编程特性。

The 4.92-MHz clock generated by the AD7192生成的4.92 MHz时钟用作主机时钟。ADA2200生成滤波器和PSD时钟所需的一切内部信号,此外还在RCLK引脚上生成激励信号。该器件将主机时钟进行1024分频,以便生成4.8 kHz信号,控制CMOS开关。CMOS开关将低噪声3.3 V源转换为LVDT的方波激励信号。用于激励源的3.3 V电源还用作ADC基准电压源,因此电压源中的一切漂移都不会降低测量精度。在满量程位移处,LVDT输出1.6 V峰峰值输出电压。

抗混叠滤波

LVDT输出和ADA2200输入之间的RC网络为LVDT输出信号提供低通滤波,同时产生使解调器输出信号最大所需的相对相移。如前所述,图2b显示了最大PSD输出发生在相对相移为0°或180°处。ADA2200具有90°相位控制,因而还可以使用±90°相对相位失调。

解调频率奇数倍的信号能量将出现在输出滤波器的通带内。FIR抽取滤波器实现抗混叠滤波,能为这些频率提供至少50 dB衰减。

如有需要,IIR滤波器可提供额外的滤波或增益。由于IIR滤波器在相敏检波器前面,其相位响应将会影响PSD信号输出带宽。设计滤波器响应时,必须考虑这一点。

输出滤波器

应选择输出滤波器的通带,使其匹配待测参数的带宽,但限制系统的宽带噪声。输出低通滤波器必须还要能够抑制PSD偶数倍产生的输出杂散。

该电路使用Σ-Δ型ADC AD7192内置的LPF。它可以通过编程实现sinc3或sinc4响应,并且传递函数在输出数据速率的倍数处为零。

将ADC的输出数据速率设为解调频率可以抑制PSD输出杂散。ADC的可编程输出数据速率用作可选带宽输出滤波器。可用的输出数据速率(fDATA)为4.8 kHz/n,其中1 ≤ n ≤ 1023。因此,ADC对每个输出数据数值的n个解调时钟周期内求解调器输出的平均值。由于主机时钟和ADC时钟同步,ADC输出滤波器传递函数的零点将直接落在调制频率的每一个谐波上,并且抑制任意n值的所有输出杂散。

可编程输出数据速率具有噪声和带宽/建立时间之间的直观权衡取舍关系。输出滤波器噪声带宽为0.3 × fDATA、3 dB频率为0.272 × fDATA,建立时间为3/fDATA。

在最高4.8 kHz输出数据速率下,ADC数字滤波器具有1.3 kHz左右的3 dB带宽。在不超过此频率的范围内,解调器和ADC之间的RC滤波器相对平坦,最大程度降低了ADC的带宽要求。在最大数据速率较低的系统中,RC滤波器转折频率可以按比例降低。

噪声性能

该电路的输出噪声是ADC输出数据速率的函数。表1显示数字化数据相对于ADC采样速率的有效位数,假设满量程输出电压为2.5 V。噪声性能与LVDT内核位置无关。

表1. 噪声性能与带宽的关系

| ADC数据速率(SPS) | 输出带宽 (Hz) | ENOB (rms) | ENOB (p-p) |

| 4800 | 1300 | 13.8 | 11.3 |

| 1200 | 325 | 14.9 | 12.3 |

| 300 | 80 | 15.8 | 13.2 |

| 75 | 20 | 16.2 | 13.5 |

如果ADA2200输出噪声与频率无关,则预计有效位数将在输出数据速率每4×下降时增加一位。ENOB在较低输出数据速率下不会上升太多,这是由于ADA2200输出驱动器的1/f噪声所导致的;该噪声在较低的输出数据速率下成为噪底的主要成分。

线性度

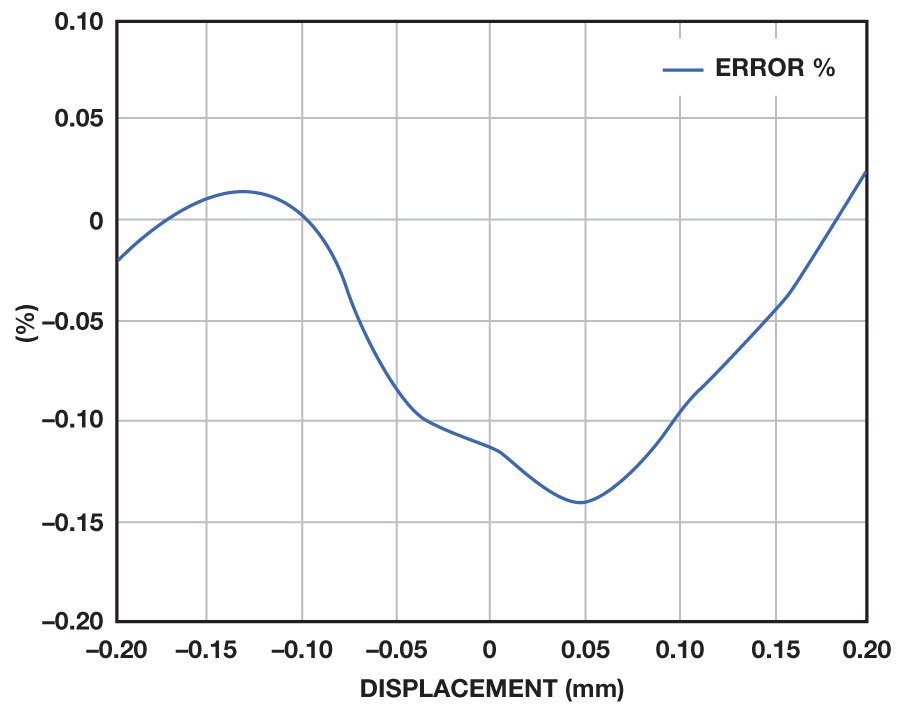

首先在±2.0 mm内核位移处执行一次两点校准即可测量线性度结果。由这些测量结果可确定斜率和失调,从而实现最佳直线拟合。然后,在±2.5 mm满量程范围内测量内核位移。从直线数据中减去测量数据即可确定线性度误差。

用于电路评估的E系列LVDT线性度额定值为±0.5%(±2.5 mm位移范围)电路性能超过了LVDT的规格。

功耗

电路总功耗为10.2 mW,包括驱动LVDT的6.6 mW以及电路其余部分的3.6 mW。电路SNR可以通过增加LVDT激励信号而得到改善,但代价是功耗更高。或者,可以通过降低LVDT激励信号从而降低功耗,同时使用低功耗双通道运算放大器来放大LVDT输出信号,以便保留电路的SNR性能。

结论

同步解调可以解决很多传感器信号调理所共有的特性挑战。低于1 MHz激励频率且动态范围要求为80 dB至100 dB的系统可以采用低成本、低功耗模拟电路;该方法所需的数字后处理极少。了解相敏检波器的工作原理以及传感器输出端的噪声特性是确定系统滤波器要求的关键。

-

使用调制解调器的注意事项2024-11-10 1940

-

电源滤波器在接线时有哪些需要注意的事项?2024-01-31 1389

-

设计软板pcb需要注意哪些事项2023-12-19 1324

-

低功耗同步解调器设计考虑的因素2023-11-23 327

-

螺杆支撑座在使用中需要注意的事项2023-04-10 1484

-

低功耗同步解调器设计注意事项2023-01-09 1591

-

STM32进入低功耗模式和唤醒有些需要注意的事项2022-02-11 661

-

低成本低功耗的同步解调器设计怎么简单化?2021-05-20 1086

-

AD5700/AD5700-1:低功耗HART调制解调器2021-03-21 1329

-

FPGA低功耗设计需要注意哪些事项?2019-11-05 1868

-

小巧灵活的低功耗调制解调器IC改进HART通信网络2018-10-22 2831

-

相敏解调器2016-03-16 6939

-

低功耗同步解调器设计考虑因素2015-08-25 1835

全部0条评论

快来发表一下你的评论吧 !