AN143模型可精确预测PLL系统中参考杂散电平的产生

描述

介绍的是一个简单的模型,可用于精确预测由于PLL系统中的电荷泵和/或运算放大器泄漏电流引起的参考杂散电平。知道如何预测这些电平有助于在PLL系统设计的早期阶段明智地选择环路参数。

PLL的快速回顾

锁相环(PLL)是一种负反馈系统,可锁定较高频率器件(通常为压控振荡器,VCO)的相位和频率,其频率和频率在温度和时间上不是非常稳定,而是更稳定和更低频率的器件(通常温度补偿或恒温控制晶体振荡器,TCXO或OCXO)。作为黑盒子,可以将PLL视为倍频器。

当需要高频本振(LO)源时,使用PLL。示例应用很多,包括无线通信,医疗设备和仪器。

图1显示了用于生成LO信号的PLL系统的构建模块。 PLL集成电路(IC)通常包含所有时钟分频器(R和N),相位/频率检测器(PFD)和电荷泵,由两个电流源ICP_UP和ICP_DN表示。

将两个信号的频率按其各自的整数分频器(分别为N和R)分频后,将VCO输出与参考时钟(此处为OCXO输出)进行比较。 PFD模块控制电荷泵以fPFD速率吸收或提供电流脉冲进入环路滤波器,以调整VCO调谐端口(V_TUNE)上的电压,直到时钟分频器的输出频率相等且同相。当它们相等时,可以说PLL被锁定。 LO频率通过以下等式与参考频率f REF 相关:

f LO = N / R * f REF

图1所示的PLL称为整数N PLL,因为反馈分频器(N分频器)只能采用整数值。当此分频器可以采用整数和非整数值时,该循环称为小数N分频PLL。这里的重点仅在整数N个PLL上,因为不同的机制在小数N分频PLL中起作用。

整数N分频器非理想性

PLL IC为系统提供了自己的非理想性,主要是相位噪声和杂散。

相位噪声

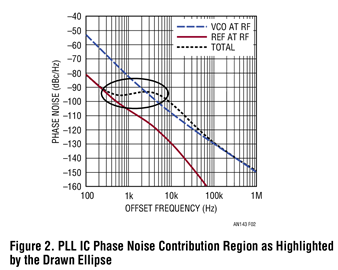

图1的PLL系统充当参考时钟相位噪声的低通滤波器,并作为VCO的高通滤波器。低通和高通滤波器截止频率由PLL的环路带宽(LBW)定义。理想情况下,LO相位噪声遵循转换为LO频率的参考时钟(即,乘以N / R)直到LBW并随后跟随VCO的相位噪声。 PLL IC的噪声贡献会提升过渡区域的相位噪声。

图2是PLLWizard生成的相位噪声图,PLLWizard是凌力尔特公司的免费PLL设计和仿真工具。该图显示了总输出相位噪声(TOTAL)以及由于参考(RF上的REF)和VCO(RF上的VCO)引起的输出的单个噪声。可以在突出显示的区域轻松看到IC的噪声贡献。

杂散

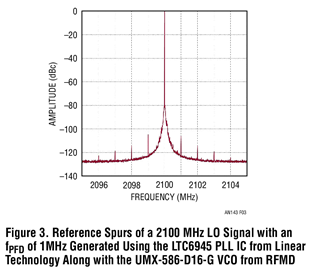

图1所示电源上的任何不需要的信号(V_OCXO,V_CP和V_VCO)可以转换为LO信号上的杂散(杂散)。仔细设计这些耗材可以大大减少甚至消除这些刺激。然而,电荷泵相关的马刺是不可避免的。但是,通过仔细的PLL系统设计可以减少它们。这些杂散通常被称为参考杂散,但这里的参考并不意味着参考时钟频率。相反,它指的是fPFD。由整数N PLL产生的LO信号在fPFD及其谐波处具有双边带杂散。

例如,图3显示了2.1GHz LO信号的频谱。 fPFD为1MHz(N = 2100),参考时钟为10MHz(R = 10)。环路带宽为40kHz。作为旁注,值得一提的是,由于凌力尔特公司的超低噪声和寄生PLL IC LTC6945的高性能,此测量中实现的杂散电平是世界一流的。

参考杂散的原因

在稳态操作中,PLL被锁定,理论上,不再需要使用图1的ICP_UP和ICP_DN电流源在每个PFD周期中。然而,这样做会在循环响应中产生死区,因为小信号环增益(实际上是开环)显着下降。通过强制ICP_UP和ICP_DN在每个PFD周期期间产生极窄的脉冲来消除该死区。这些通常被称为反间隙脉冲。这会在fPFD及其谐波上产生VCO调谐线上的能量含量。负反馈无法抵消这些脉冲,因为这些频率超出了正确设计的PLL的环路带宽。然后,VCO通过这种能量内容进行频率调制(FM),并且相关的杂散出现在fPFD及其谐波处,全部以LO为中心。

在反间隙脉冲之间,电荷泵电流源是关(三重)。固有地,电荷泵在三态时具有一些漏电流。由于运算放大器的输入偏置和偏移电流,在有源环路滤波器(如图7中)中使用运算放大器引入了另一个漏电流源。这些不需要的电流的总和,无论是源电流还是漏电流,都会导致环路滤波器两端的电压漂移,从而导致VCO的调谐电压发生漂移。环路的负反馈将通过每个PFD周期从电荷泵引入单极电流脉冲来校正该异常,使得平均调谐线电压从VCO产生正确的频率。脉冲在fPFD处产生能量,这也会导致杂散以LO为中心,并被fPFD及其谐波所抵消,如前所述。

在整数N分频PLL中,由于系统的频率步长要求,fPFD通常选择相对较小。这意味着与PFD周期相比,抗间隙脉冲宽度,特别是当前的高速IC技术,非常小。因此,大的漏电流导致总电荷泵脉冲是单极性的并且往往是参考杂散的主要原因。这种现象将得到更深入的研究。

-

最麻烦的PLL杂散信号——整数边界杂散2023-05-22 10201

-

CN0232 将集成VCO和外部PLL电路的频率合成器杂散输出降至最低2021-05-28 1092

-

AN143-一种准确预测泄漏电流引起的PLL参考杂散电平的简单方法2021-05-11 849

-

可预测由泄漏电流引起的PLL基准杂散噪声的方法2019-05-27 736

-

带VCO的锁相环的整数边界杂散信号的产生与消除方法2019-04-12 13055

-

导致PLL相位噪声和参考杂散的原因及解决方案2019-04-04 25271

-

快速跳频PLL优化杂散抑制比分析2011-09-01 1105

全部0条评论

快来发表一下你的评论吧 !