你了解uboot的at91sam9g45移植

嵌入式技术

描述

一、第一阶段,无修改

二、第二阶段

u-boot-1.3.4\lib_arm\board.c

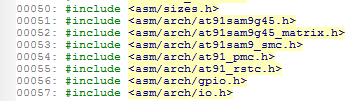

1.增加头文件

2.增加版本号

3.start_armboot中初始化部分

板级初始化部分init_sequence->board_init

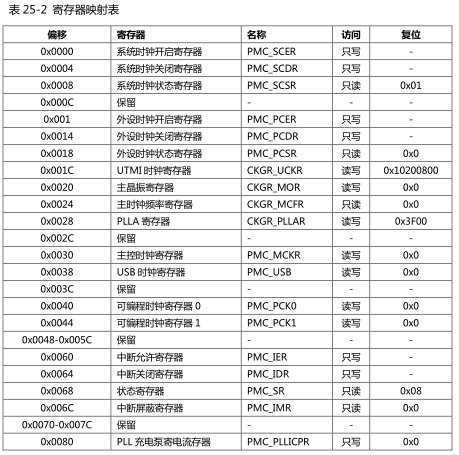

3.1创建新单板资源头文件include\asm-arm\arch-at91sam9\at91sam9m10g45ek.h(地址与中断号)

文件书写思路:

1.参考同系列芯片的at91sam9263.h文件

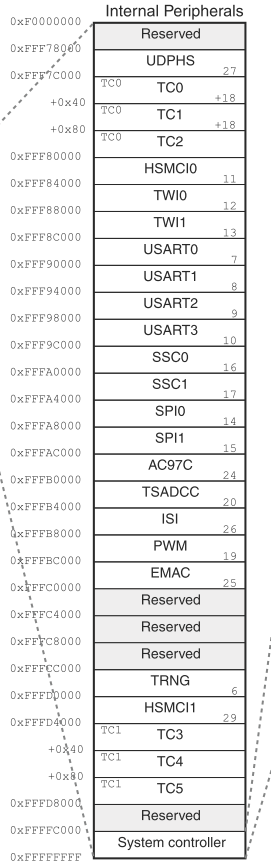

2.外设标识符

3.用户外围物理基地址

4.系统外设物理基地址(基于系统控制寄存器)

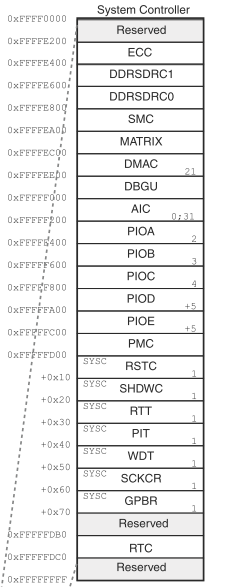

5.内部存储基地址

参照图表:

附上源代码:

at91sam9m10g45ek.h

at91sam9m10g45ek.h

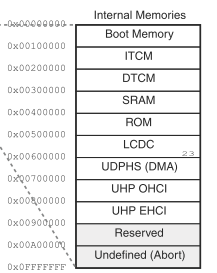

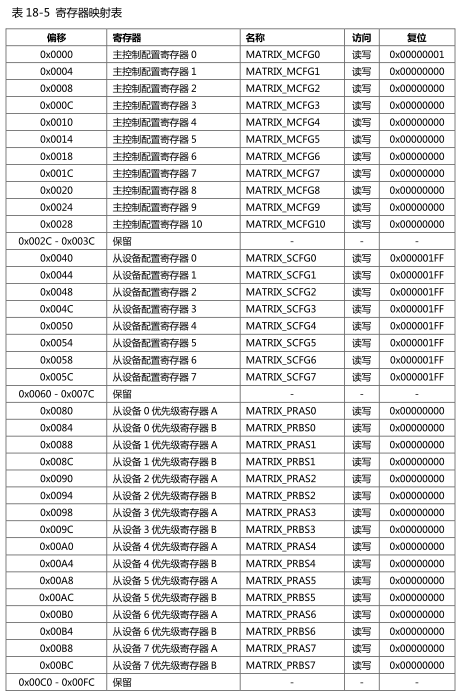

3.2 创建单板总线矩阵头文件include\asm-arm\arch-at91sam9\at91sam9g45_matrix.h(地址)

文件书写思路:

1.参考同系列芯片的at91sam9263_matrix.h文件

2.寄存器映射表

参照图表:

附上源代码:

at91sam9g45_matrix.h

at91sam9g45_matrix.h

3.3 创建单板初始化文件u-boot-1.3.4/board/atmel/at91sam9m10g45ek/at91sam9m10g45ek.c

文件书写思路:

1)参考同系列芯片的at91sam9263ek.c文件

2)初始化队列中board_init()

2.1)控制台初始化

2.2)机器ID初始化

2.3)启动参数存储地址初始化

2.4)串口硬件初始化

2.4.1)设置复用GPIO口为A设备

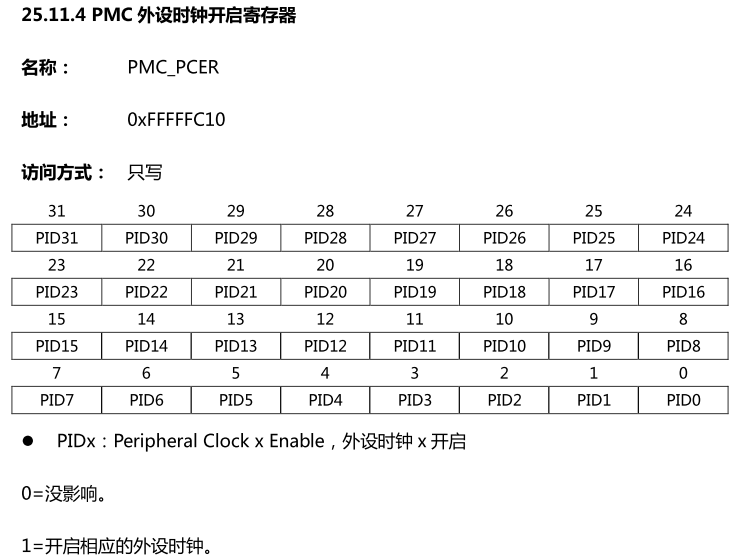

2.4.2)写寄存器,使能时钟开启(参数是外设标识符)

2.5)nandflash硬件初始化

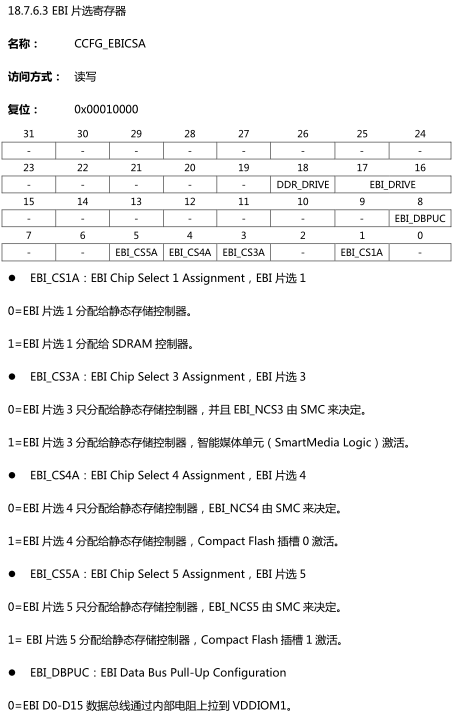

2.5.1) 读取片选寄存器

2.5.2) 设置EBI片选3分配给静态存储控制器

2.5.3) 设置静态存储控制器

2.5.4) 外设时钟开启寄存器,并行IO控制器C

2.5.5) C8初始化为输入

2.5.6) C14初始化为输出

2.6)spi硬件初始化

2.6.1) 设置B3为复用GPIO口B设备,用作NPCS0

2.6.2) 设置B0为复用GPIO口B设备,用作MISO0

2.6.3) 设置B1为复用GPIO口B设备,用作MOSI0

2.6.4) 设置B2为复用GPIO口B设备,用作SPCK0

2.6.5) 写寄存器,使能时钟开启(参数是外设标识符SPI0)

2.7)macb硬件初始化

2.7.1) 禁止上拉A15 A12 A13

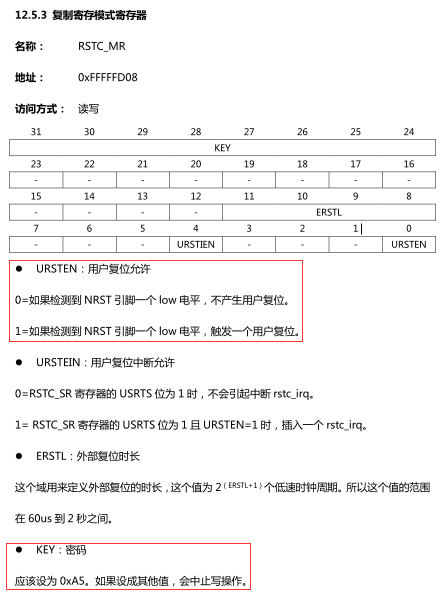

2.7.2) 读取复位寄存模式寄存器

2.7.3) 设置复位寄存器周期,允许复位

2.7.4) 设置外部复位

2.7.5) 等待硬件复位结束

2.7.6) 设置允许复位

2.7.7) 使能上拉A15 A12 A13

2.7.8) 复用IO A10-19 为A设备 功能:ETXCK_EREFCK、ERXDV、ERX0、ERX1、ERXER、ETXEN、ETX0、ETX1、EMDIO、EMDC

2.7.9) 复用IO A6-9 A27-30 为B设备 功能:ECRS、ECOL、ERX2、ERX3、ERXCK、ETX2、ETX3、ETXER

2.7.10) D5引脚复位

2.8)lcd硬件初始化

2.8.1) 复用IO E0 E4-30 为A设备 功能:LCDDPWR、LCDHSYNC、LCDDOTCK、LCDDEN、LCDD0-23

2.8.1) 外设时钟开启寄存器,LCD

3) 初始化队列中dram_init()

3.1) 初始化RAM起始地址0x70000000

3.2) 初始化RAM大小0x08000000

附上源码:

1 #include 2 #include 3 #include 4 #include 5 #include 6 #include 7 #include 8 #include 9 #include 10 #include 11 //#include //have udelay() 12 #include 13 #if defined(CONFIG_RESET_PHY_R) && defined(CONFIG_MACB) 14 #include 15 #endif 16 17 DECLARE_GLOBAL_DATA_PTR; 18 19 /* ------------------------------------------------------------------------- */ 20 /* 21 * Miscelaneous platform dependent initialisations 22 */ 23 24 static void at91samm10g45ek_serial_hw_init(void) 25 { 26 #ifdef CONFIG_USART0 27 at91_set_A_periph(AT91_PIN_PB19, 1); /* TXD0 */ 28 at91_set_A_periph(AT91_PIN_PB18, 0); /* RXD0 */ 29 at91_sys_write(AT91_PMC_PCER, 1 << AT91SAM9G45_ID_US0); 30 #endif 31 32 #ifdef CONFIG_USART1 33 at91_set_A_periph(AT91_PIN_PB4, 1); /* TXD1 */ 34 at91_set_A_periph(AT91_PIN_PB5, 0); /* RXD1 */ 35 at91_sys_write(AT91_PMC_PCER, 1 << AT91SAM9G45_ID_US1); 36 #endif 37 38 #ifdef CONFIG_USART2 39 at91_set_A_periph(AT91_PIN_PD6, 1); /* TXD2 */ 40 at91_set_A_periph(AT91_PIN_PD7, 0); /* RXD2 */ 41 at91_sys_write(AT91_PMC_PCER, 1 << AT91SAM9G45_ID_US2); 42 #endif 43 44 #ifdef CONFIG_USART3 /* DBGU */ 45 at91_set_A_periph(AT91_PIN_PB12, 0); /* DRXD */ 46 at91_set_A_periph(AT91_PIN_PB13, 1); /* DTXD */ 47 at91_sys_write(AT91_PMC_PCER, 1 << AT91_ID_SYS); 48 #endif 49 } 50 51 #ifdef CONFIG_CMD_NAND 52 static void at91samm10g45ek_nand_hw_init(void) 53 { 54 unsigned long csa; 55 56 /* Enable CS3 */ 57 //EBI 片选 3 分配给静态存储控制器 58 csa = at91_sys_read(AT91_MATRIX_EBICSA); 59 at91_sys_write(AT91_MATRIX_EBICSA, csa | AT91_MATRIX_EBI_CS3A_SMC_SMARTMEDIA); 60 61 /* Configure SMC CS3 for NAND/SmartMedia */ 62 //NWE 建立时长=(128 X NWE_SETUP[5] + NWE_SETUP[4:0])时钟周期 63 //NCS 建立时长=(128 X NCS_WR_SETUP[5] + NCS_WR_SETUP[4:0])时钟周期 64 //NRD 建立时长=(128 X NRD_SETUP[5] + NRD_SETUP[4:0])时钟周期 65 //NCS 建立时长=(128 X NCS_RD_SETUP[5] + NCS_RD_SETUP[4:0])时钟周期 66 at91_sys_write(AT91_SMC_SETUP(3), 67 AT91_SMC_NWESETUP_(1) | AT91_SMC_NCS_WRSETUP_(0) | 68 AT91_SMC_NRDSETUP_(1) | AT91_SMC_NCS_RDSETUP_(0)); 69 //NWE 脉宽=(256 X NWE_PULSE[6] + NWE_PULSE[5:0])时钟周期 70 //NCS 脉宽=(256 X NCS_WR_PULSE[6] + NCS_WR_PULSE[5:0])时钟周期 71 //NRD 脉宽=(256 X NRD_PULSE[6] + NRD_PULSE[5:0])时钟周期 72 //NCS 脉宽=(256 X NCS_RD_PULSE[6] + NCS_RD_PULSE[5:0])时钟周期 73 at91_sys_write(AT91_SMC_PULSE(3), 74 AT91_SMC_NWEPULSE_(4) | AT91_SMC_NCS_WRPULSE_(3) | 75 AT91_SMC_NRDPULSE_(3) | AT91_SMC_NCS_RDPULSE_(2)); 76 //写周期长度=(NWE_CYCLE[8:7] X 256 + NWE_CYCLE[6:0])时钟周期 77 //读周期长度=(NRD_CYCLE[8:7] X 256 + NRD_CYCLE[6:0])时钟周期 78 at91_sys_write(AT91_SMC_CYCLE(3), 79 AT91_SMC_NWECYCLE_(7) | AT91_SMC_NRDCYCLE_(4)); 80 //读操作是由 NRD 信号来控制的。 81 //写操作是由 NWE 信号控制的 82 //NWAIT 是用来扩展当前的读或写信号的,它只在读和写控制信号的脉宽才会被考虑。如果NWAIT 启用了,在读和写控制信号中必须设置至少一个周期。 83 //数据总线宽度8-位总线 84 //数据浮动时间: 外部设备在读控制信号上升沿后释放数据的整数个周期时间 85 at91_sys_write(AT91_SMC_MODE(3), 86 AT91_SMC_READMODE | AT91_SMC_WRITEMODE | 87 AT91_SMC_EXNWMODE_DISABLE | 88 #ifdef CFG_NAND_DBW_16 89 AT91_SMC_DBW_16 | 90 #else /* CFG_NAND_DBW_8 */ 91 AT91_SMC_DBW_8 | 92 #endif 93 AT91_SMC_TDF_(3)); 94 //外设时钟开启寄存器 并行IO控制器C 95 at91_sys_write(AT91_PMC_PCER, 1 << AT91SAM9G45_ID_PIOC); 96 97 /* Configure RDY/BSY */ 98 //输入初始化 99 at91_set_gpio_input(AT91_PIN_PC8, 1);100 101 /* Enable NandFlash */102 //输出初始化103 at91_set_gpio_output(AT91_PIN_PC14, 1);104 }105 #endif106 107 #ifdef CONFIG_HAS_DATAFLASH108 static void at91samm10g45ek_spi_hw_init(void)109 {110 at91_set_B_periph(AT91_PIN_PB3, 0); /* SPI0_NPCS0 */111 112 at91_set_B_periph(AT91_PIN_PB0, 0); /* SPI0_MISO */113 at91_set_B_periph(AT91_PIN_PB1, 0); /* SPI0_MOSI */114 at91_set_B_periph(AT91_PIN_PB2, 0); /* SPI0_SPCK */115 116 /* Enable clock */117 at91_sys_write(AT91_PMC_PCER, 1 << AT91SAM9G45_ID_SPI0);118 }119 #endif120 121 #ifdef CONFIG_MACB122 /***********md9161 reset test****************/123 //D5脚复位网卡124 static void macb_reset(void)125 {126 int i;127 128 at91_set_gpio_output(AT91_PIN_PD5,0);129 130 //puts("macb_reset... \n");131 for(i=0;i<500000;i++)132 {133 ;134 }135 136 // udelay(200*1000);137 138 at91_set_gpio_output(AT91_PIN_PD5,1);139 140 }141 142 /***************************************/143 static void at91samm10g45ek_macb_hw_init(void)144 {145 unsigned long rstc;146 147 // macb_reset();//reset dm9161148 149 /* Enable clock */150 at91_sys_write(AT91_PMC_PCER, 1 << AT91SAM9G45_ID_EMAC);151 152 /*153 * Disable pull-up on:154 * RXDV (PA15) => PHY normal mode (not Test mode)155 * ERX0 (PA12) => PHY ADDR0156 * ERX1 (PA13) => PHY ADDR1 => PHYADDR = 0x0157 *158 * PHY has internal pull-down159 */160 161 /*AC97*/162 //at91_set_A_periph(AT91_PIN_PD8, 0); /* AC97FS */163 //at91_set_A_periph(AT91_PIN_PD7, 0); /* AC97TX */164 //禁止上拉 A15 A12 A13165 writel(pin_to_mask(AT91_PIN_PA15) |166 pin_to_mask(AT91_PIN_PA12) |167 pin_to_mask(AT91_PIN_PA13),168 pin_to_controller(AT91_PIN_PA0) + PIO_PUDR);169 //读取复位寄存模式寄存器170 rstc = at91_sys_read(AT91_RSTC_MR);171 172 /* Need to reset PHY -> 500ms reset */173 //KEY:应该设为 0xA5。如果设成其他值,会中止写操作174 //外部复位的时长,这个值为 2 (ERSTL+1) 个低速时钟周期。所以这个值的范围175 //检测到 NRST (复位)引脚一个 low 电平,触发一个用户复位176 at91_sys_write(AT91_RSTC_MR, AT91_RSTC_KEY |177 (AT91_RSTC_ERSTL & (0x0D << 8)) |178 AT91_RSTC_URSTEN);179 // 复位控制器控制寄存器180 //外部复位:如果 KEY 正确,插入 NRST (复位)引脚181 at91_sys_write(AT91_RSTC_CR, AT91_RSTC_KEY | AT91_RSTC_EXTRST);182 183 //复位控制器状态寄存器184 //读取以主控制器时钟频率(MCK)锁存 NRST (复位)引脚的电平 目的:等待硬件复位结束185 while (!(at91_sys_read(AT91_RSTC_SR) & AT91_RSTC_NRSTL));186 187 /* Restore NRST value */188 //如果检测到 NRST (复位)引脚一个 low 电平,触发一个用户复位189 at91_sys_write(AT91_RSTC_MR, AT91_RSTC_KEY |190 (rstc) |191 AT91_RSTC_URSTEN);192 //使能上拉 A15 A12 A13193 /* Re-enable pull-up */194 writel(pin_to_mask(AT91_PIN_PA15) |195 pin_to_mask(AT91_PIN_PA12) |196 pin_to_mask(AT91_PIN_PA13),197 pin_to_controller(AT91_PIN_PA0) + PIO_PUER);198 199 //at91_set_gpio_output(AT91_PIN_PA30,1); //pull up PA30200 //复用IO A10-19 为A设备201 at91_set_A_periph(AT91_PIN_PA17, 0); /* ETXCK_EREFCK */202 at91_set_A_periph(AT91_PIN_PA15, 0); /* ERXDV */203 at91_set_A_periph(AT91_PIN_PA12, 0); /* ERX0 */204 at91_set_A_periph(AT91_PIN_PA13, 0); /* ERX1 */205 at91_set_A_periph(AT91_PIN_PA16, 0); /* ERXER */206 at91_set_A_periph(AT91_PIN_PA14, 0); /* ETXEN */207 at91_set_A_periph(AT91_PIN_PA10, 0); /* ETX0 */208 at91_set_A_periph(AT91_PIN_PA11, 0); /* ETX1 */209 at91_set_A_periph(AT91_PIN_PA19, 0); /* EMDIO */210 at91_set_A_periph(AT91_PIN_PA18, 0); /* EMDC */211 212 #ifndef CONFIG_RMII213 //复用IO A6-9 A27-30 为B设备214 at91_set_B_periph(AT91_PIN_PA29, 0); /* ECRS */215 at91_set_B_periph(AT91_PIN_PA30, 0); /* ECOL */216 at91_set_B_periph(AT91_PIN_PA8, 0); /* ERX2 */217 at91_set_B_periph(AT91_PIN_PA9, 0); /* ERX3 */218 at91_set_B_periph(AT91_PIN_PA28, 0); /* ERXCK */219 at91_set_B_periph(AT91_PIN_PA6, 0); /* ETX2 */220 at91_set_B_periph(AT91_PIN_PA7, 0); /* ETX3 */221 at91_set_B_periph(AT91_PIN_PA27, 0); /* ETXER */222 #endif223 macb_reset();//reset dm9161224 //printf("macb_reset...\n");225 }226 #endif227 228 #ifdef CONFIG_LCD229 vidinfo_t panel_info = {230 vl_col: 480,231 vl_row: 272,232 vl_clk: 125000,233 vl_sync: ATMEL_LCDC_INVLINE_NORMAL |234 ATMEL_LCDC_INVFRAME_NORMAL,235 vl_bpix: 3,236 vl_tft: 1,237 vl_hsync_len: 41,238 vl_left_margin: 2,239 vl_right_margin:2,240 vl_vsync_len: 1,241 vl_upper_margin:2,242 vl_lower_margin:2,243 mmio: AT91SAM9G45_LCDC_BASE,244 };245 246 void lcd_enable(void)247 {248 at91_set_gpio_value(AT91_PIN_PE6, 1); /* power up */249 }250 251 void lcd_disable(void)252 {253 at91_set_gpio_value(AT91_PIN_PE6, 0); /* power down */254 }255 256 static void at91samm10g45ek_lcd_hw_init(void)257 {258 at91_set_A_periph(AT91_PIN_PE0, 0); /* LCDDPWR */259 260 at91_set_A_periph(AT91_PIN_PE4, 0); /* LCDHSYNC */261 at91_set_A_periph(AT91_PIN_PE5, 0); /* LCDDOTCK */262 263 at91_set_gpio_input(AT91_PIN_PE6, 0); /* LCDDEN */264 265 at91_set_A_periph(AT91_PIN_PE7, 0); /* LCDD0 */266 at91_set_A_periph(AT91_PIN_PE8, 0); /* LCDD1 */267 at91_set_A_periph(AT91_PIN_PE9, 0); /* LCDD2 */268 at91_set_A_periph(AT91_PIN_PE10, 0); /* LCDD3 */269 at91_set_A_periph(AT91_PIN_PE11, 0); /* LCDD4 */270 at91_set_A_periph(AT91_PIN_PE12, 0); /* LCDD5 */271 at91_set_A_periph(AT91_PIN_PE13, 0); /* LCDD6 */272 at91_set_A_periph(AT91_PIN_PE14, 0); /* LCDD7 */273 at91_set_A_periph(AT91_PIN_PE15, 0); /* LCDD8 */274 at91_set_A_periph(AT91_PIN_PE16, 0); /* LCDD9 */275 at91_set_A_periph(AT91_PIN_PE17, 0); /* LCDD10 */276 at91_set_A_periph(AT91_PIN_PE18, 0); /* LCDD11 */277 at91_set_A_periph(AT91_PIN_PE19, 0); /* LCDD12 */278 at91_set_B_periph(AT91_PIN_PE20, 0); /* LCDD13 */279 at91_set_A_periph(AT91_PIN_PE21, 0); /* LCDD14 */280 at91_set_A_periph(AT91_PIN_PE22, 0); /* LCDD15 */281 at91_set_A_periph(AT91_PIN_PE23, 0); /* LCDD16 */282 at91_set_A_periph(AT91_PIN_PE24, 0); /* LCDD17 */283 at91_set_A_periph(AT91_PIN_PE25, 0); /* LCDD18 */284 at91_set_A_periph(AT91_PIN_PE26, 0); /* LCDD19 */285 at91_set_A_periph(AT91_PIN_PE27, 0); /* LCDD20 */286 at91_set_B_periph(AT91_PIN_PE28, 0); /* LCDD21 */287 at91_set_A_periph(AT91_PIN_PE29, 0); /* LCDD22 */288 at91_set_A_periph(AT91_PIN_PE30, 0); /* LCDD23 */289 290 at91_sys_write(AT91_PMC_PCER, 1 << AT91SAM9G45_ID_LCDC);291 292 gd->fb_base = AT91SAM9G45_SRAM_BASE;293 }294 #endif295 296 #if defined(CONFIG_MACB) && defined(CONFIG_CMD_NET)297 extern int macb_eth_initialize(int id, void *regs, unsigned int phy_addr);298 299 int board_eth_init(bd_t *bis)300 {301 macb_eth_initialize(0, (void *)AT91SAM9G45_BASE_EMAC, 0x00);302 }303 #endif304 305 int board_init(void)306 {307 /* Enable Ctrlc */308 console_init_f();309 /* arch number of AT91SAM9M10G45EK-Board */310 #ifdef CONFIG_AT91SAM9M10G45EK311 gd->bd->bi_arch_number = MACH_TYPE_AT91SAM9M10G45EK;312 #elif defined CONFIG_AT91SAM9G45EKES313 gd->bd->bi_arch_number = MACH_TYPE_AT91SAM9G45EKES;314 #elif defined CONFIG_AT91SAM9M10EKES315 gd->bd->bi_arch_number = MACH_TYPE_AT91SAM9M10EKES;316 #endif317 /* adress of boot parameters */318 gd->bd->bi_boot_params = PHYS_SDRAM + 0x100;//启动参数地址,DDR内存位置319 320 at91samm10g45ek_serial_hw_init();321 #ifdef CONFIG_CMD_NAND322 at91samm10g45ek_nand_hw_init();323 #endif324 #ifdef CONFIG_HAS_DATAFLASH325 at91samm10g45ek_spi_hw_init();326 #endif327 #ifdef CONFIG_MACB328 at91samm10g45ek_macb_hw_init();329 #endif330 331 #ifdef CONFIG_LCD332 at91samm10g45ek_lcd_hw_init();333 #endif334 return 0;335 }336 337 int dram_init(void)338 {339 gd->bd->bi_dram[0].start = PHYS_SDRAM;340 gd->bd->bi_dram[0].size = PHYS_SDRAM_SIZE;341 printf("\n++++++++++++++++++++++++++++++++++++++++++++\n");342 return 0;343 }344 345 #ifdef CONFIG_RESET_PHY_R346 void reset_phy(void)347 {348 #ifdef CONFIG_MACB349 /*350 * Initialize ethernet HW addr prior to starting Linux,351 * needed for nfsroot352 */353 //puts("reset_phy \n");354 eth_init(gd->bd);355 #endif356 }357 #endif

3.4 board.c中NAND初始化

1) drivers\mtd\nand\nand.c标准函数nand_init->nand_init_chip->board_nand_init

2) 增加nand文件board\atmel\at91sam9m10g45ek\nand.c

2.1) board_nand_init初始化函数

2.1.1) 初始化eccmode 软件ECC对应字节数

2.1.2) 初始化options 总线宽度

2.1.3) 初始化hwcontrol 硬件控制函数

2.1.4) 初始化dev_ready 准备就绪函数

2.1.5) 初始化chip_delay 芯片时序延迟参数

2.2) hwcontrol 硬件控制函数

2.3) dev_ready 准备就绪函数

3.5 board.c中NOR初始化 使用的AT45DB161 2M NOR Flash

1) drivers\mtd\dataflash.c标准函数AT91F_DataflashInit->AT91F_SpiInit->AT91F_DataflashProbe 得到ID=c2 即AT45DB161

2) 依据ID初始化页数量、页大小、页偏移、基地址

-

基于AT91SAM9M10-G45-EK微控制器的参考设计2021-07-10 708

-

米尔科技 ATMEL AT91SAM9G45 ARM9单板机概述2019-11-04 6107

-

盈鹏飞科技at91sam9g45-Wince6.0 BSP简介2019-11-01 3229

-

基于AT91SAM9G25 SAM9G25 MCU ARM9系列的评估板AT91SAM9G25-EK2019-04-02 2788

-

AT91SAM9G20-EK评估套件2019-04-01 1716

-

AT91SAM9G45中文数据手册详细资料免费下载2018-06-12 2687

-

at91sam9g45 linux 3.18内核的独家支持!很好的资料,包括移植说明和开发指南2016-03-28 6744

-

at91sam9g45应用开发2014-10-21 3093

-

ATMEL MYS-SAM9G45 单板机(ARM9内核)2014-10-15 3706

-

AT91SAM9G20 Linux快速入门2013-05-16 3110

-

Atmel SAM9G45 32位MCU开发方案2011-08-01 4166

-

天谟公司推广基于Atmel AT91SAM9G45工业级单板2010-07-29 1039

全部0条评论

快来发表一下你的评论吧 !