PCB电路中信号终端电容的作用介绍

EDA/IC设计

描述

信号的接收端可能是集成芯片的一个引脚,也可能是其他元器件。不论接收端是什么,实际的器件的输入端必然存在寄生电容,接受信号的芯片引脚和相邻引脚之间有一定的寄生电容,和引脚相连的芯片内部的布线也会存在寄生电容,另外引脚和信号返回路径之间也会存在寄生电容。

好复杂,这么多寄生电容!其实很简单,想想电容是什么?两个金属板,中间是某种绝缘介质。这个定义中并没有说两个金属板是什么形状的,芯片两个相邻引脚也可以看做是电容的两个金属板,中间介质是空气,不就是一个电容么。芯片引脚和PCB板内层的电源或地平面也是一对金属板,中间介质是PCB板的板材,常见的是FR4材料,也是一个电容。呵呵,搞来搞去,还是回到了最基础的部分。高手不要笑,太简单了。不过确实很多人看到寄生电容就感到有点晕,理解不透,所以在这里啰嗦一下。

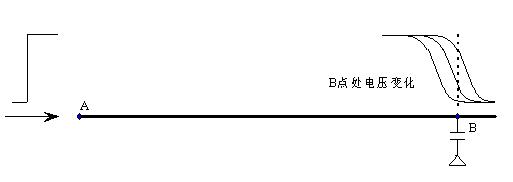

回到正题,下面研究一下信号终端的电容有什么影响。将模型简化,用一个分立电容元件代替所有寄生电容,如图1所示。

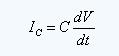

我们考察B点电容的阻抗情况。电容的电流为:

随着电容的充电,电压变化率逐渐减小(电路原理中的瞬态过程),电容的充电电流也不断减小。即电容的充电电流是随时间变化的。

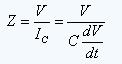

电容的阻抗为:

因此电容所表现出来的阻抗随时间变化,不是恒定的。正是这种阻抗的变化特性决定了电容对信号影响的特殊性。如果信号上升时间小于电容的充电时间,最初电容两端的电压迅速上升,这时阻抗很小。随着电容充电,电压变化率下降,充电电流减小,表现为阻抗明显增大。充电时间无穷大时,电容相当于开路,阻抗无穷大。

阻抗的变化必然影响信号的反射。在充电的开始一段时间,阻抗很小,小于传输线的特性阻抗,将发生负反射,反射回源端A点的信号将产生下冲。随着电容阻抗的增加,反射逐渐过渡到正反射,A点的信号经过一个下冲会逐渐升高,最终达到开路电压。

因此电容负载使源端信号产生局部电压凹陷。精确波形和传输线的特性阻抗、电容量、信号上升时间有关。

对于接收端,很明显,就是一个RC充电电路,不是很严谨,但是和实际情况非常相似。电容两端电压,即B点电压随RC充电电路的时间常数呈指数增加(基本电路原理)。因此电容对接收端信号上升时间产生影响。

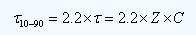

RC充电电路的时间常数为  这是B点电压上升到电压终值的

这是B点电压上升到电压终值的  即37%所需的时间。B点电压10%~90%上升时间为

即37%所需的时间。B点电压10%~90%上升时间为

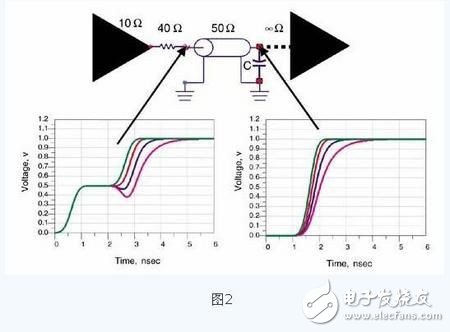

如果传输线特性阻抗为50欧姆,电容量10pF,则10~90充电时间为1.1ns。如果信号上升时间小于1.1ns,那么B点电压上升时间主要由电容充电时间决定。如果信号上升时间大于1.1ns,末端电容器作用是使上升时间进一步延长,增加约1.1ns(实际应比这个值小)。图2显示了终端电容负载对驱动端和接受端产生影响的示意图,放在这里,让大家能有个感性的认识。

至于信号上升时间增加的精确值是多少,对于电路设计来说没必要,只要定性的分析,有个大致的估算就可以了。因为计算再精确也没实际意义,电路板的参数也不精确!对于设计者来说,定性分析并了解影响,大致估算出影响在那个量级,能给电路设计提供指导就可以了,其他的事软件来做吧。举个例子,如果信号上升时间1ns,电容使信号上升时间增加远小于1ns,比如0.2 ns,那么这么一点点增加可能不会有什么影响。如果电容造成的上升时间增加很多,那可能就会对电路时序产生影响。那么多少算很多?看看电路的时序余量吧,这涉及到电路的时序分析和时序设计。

总之接收端电容负载的影响有两点:

1、 使源端(驱动端)信号产生局部电压凹陷。

2、 接收端信号上升时间延长。

在电路设计中这两点都要考虑。

-

旁路电容和去耦电容作用和区别介绍2024-03-01 4694

-

音频功放电路里电容有几种作用2024-02-06 8336

-

沐渥介绍电容电阻电感在电路中的作用2023-03-27 2310

-

电容器在电子电路中的作用介绍(三)2021-06-22 1134

-

CAN系统中信号终端电阻常见问题及解决方法2021-05-28 2073

-

高速PCB设计中信号完整性研究综述2021-05-27 1194

-

电容的作用及其工作原理的介绍(二)2021-03-23 1707

-

电容在电源电路和信号电路的作用2020-03-16 2327

-

PCB电路中信号振铃是怎么产生的2019-06-21 9484

-

PCB设计中电路措施的作用2017-03-16 2184

-

要点普及:电容应用于电源电路和信号电路的作用2016-11-08 2051

-

电容应用于电源电路和信号电路的作用2016-11-07 5681

-

印刷电路PCB的作用及介绍2010-03-13 3184

-

高速数字硬件电路设计中信号完整性在通常设计的影响2009-10-14 2791

全部0条评论

快来发表一下你的评论吧 !