PCB设计人员如何采用拓扑规划和布线工具快速完成PCB设计

EDA/IC设计

描述

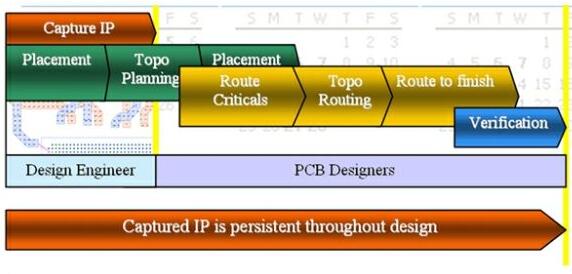

本文探讨的重点是PCB设计人员利用IP,并进一步采用拓扑规划和布线工具来支持IP,快速完成整个PCB设计。从图1可以看出,设计工程师的职责是通过布局少量必要元件、并在这些元件之间规划关键互连路径来获取IP。一旦获取到了IP,就可将这些IP信息提供给PCB设计人员,由他们完成剩余的设计。

图1:设计工程师获取IP,PCB设计人员进一步采用拓扑规划和布线工具支持IP,快速完成整个PCB设计。

现在无需再通过设计工程师和PCB设计人员之间的交互和反复过程来获取正确的设计意图,设计工程师已经获取这些信息,并且结果相当精确,这对PCB设计人员来说帮助很大。在很多设计中,设计工程师和PCB设计人员要进行交互式布局和布线,这会消耗双方许多宝贵的时间。从以往的经历来看交互操作是必要的,但很耗时间,且效率低下。设计工程师提供的最初规划可能只是一个手工绘图,没有适当比例的元件、总线宽度或引脚输出提示。

随着PCB设计人员参与到设计中来,虽然采用拓扑规划技术的工程师可以获取某些元件的布局和互连,不过,这个设计可能还需要布局其它元件、获取其它IO及总线结构和所有互连才能完成。

PCB设计人员需要采用拓扑规划,并与经过布局的和尚未布局的元件进行交互,这样做可以形成最佳的布局和交互规划,从而提高PCB设计效率。

随着关键区域和高密区域布局完成及拓扑规划被获取,布局可能先于最终拓扑规划完成。因此,一些拓扑路径可能必须与现有布局一起工作。虽然它们的优先级较低,但仍需要进行连接。因而一部分规划围绕布局后的元件产生了。此外,这一级规划可能需要更多细节来为其它信号提供必要的优先级。

详细的拓扑规划

图2所示的就是元件完成布局后的详细规划。这条总线共有17位,它们有组织得相当好的信号流。

图2:这些总线的网络线是采用更高优先级的拓扑规划和布局的结果。

为了规划这条总线,PCB设计人员需要考虑现有的一些障碍、各层设计规则和其它重要约束条件。在了解了这些条件后,他们为这条总线规划出了如图3所示的拓扑路径。

图3:规划好的总线。

在图3中,细节“1”对“红色”顶层的元件管脚做了规划,用于从元件引脚引出,并连接到细节“2”处的拓扑路径。这部分用的未封装区域,并且仅把第一层确定为可布线层。从设计角度看这样做似乎是很显而易见的,而且布线算法将使用顶层连接到红色的拓扑路径。不过,在对这根特殊总线自动布线前一些障碍物可能向算法提供其它层布线的选项。

随着总线在第一层上被组织成紧密线迹后,设计人员开始在细节“3”处规划到第3层的转换部分,并考虑总线在整个PCB上的行进距离。注意,第3层上的这条拓扑路径要比顶层宽,因为考虑到了要适应阻抗需要额外的空间。另外,设计还为层转换规定了确切位置(17个过孔)。

当拓扑路径沿着图3中间靠右部分走到细节“4”处时,需要从拓扑路径连接和各个元件引脚处引出许多单比特T型交接点。PCB设计人员的选择是保持大多数连接流在第3层上,并穿透到其它层用于连接元件引脚。因此他们画了一个拓扑区用于指示从主线束到第4层(粉色)的连接,并使这些单比特T型接点连到第2层,然后使用其它过孔连接到器件引脚。

拓扑路径在第3层上继续行进到细节“5”以连接有源器件。这些连接再从有源引脚连接到有源器件下面的下拉电阻。设计人员使用另外一个拓扑区规范从第3层到第1层的连接,那里的元件引脚分属于有源器件和下拉电阻。

这一等级的详细规划只用了约30秒时间就完成了。一旦这个规划被获取后,PCB设计人员可能想立即布线或创建进一步的拓扑规划,然后用自动布线完成所有的拓扑规划。从规划完成到自动布线结果出来不到10秒。其实这个速度并不重要,事实上如果忽略设计人员意图、自动布线质量很糟糕的话,这完全是在浪费时间。下面一些图给出了自动布线的结果。

拓扑布线(Topology Routing)

从左上角开始,从元件引脚出来的所有连线都遵从设计人员表达的意图而位于第1层上,并压缩成紧密的总线结构,如图4中的细节“1”和“2”。 第1层和第3层之间的转换发生在细节“3”处,并采用了很占用空间的过孔形式。需要重申的是,这里考虑了阻抗因素,因此走线更宽,间距更大,如实际宽度路径所表示的那样。

图4:用细节1、3拓扑布线的结果。

如图5中的细节“4”所示那样,由于需要使用过孔适应单比特T型交接点,拓扑路径变大了。这里规划又一次体现了设计人员对这些单比特T型交换点的意图,从第3层布线到第4层。另外,第3层上的线迹非常紧密,虽然在插入过孔的地方有些膨大,但经过过孔后很快又紧密起来。

图5:用细节4拓扑布线的结果。

图6给出了细节“5”处的自动布线结果。第3层上的有源器件连线要求转换到第1层。这里的过孔整齐排列在元件引脚上方,第1层走线先连到有源器件,然后再连到第1层的下拉电阻。

图6:用细节5拓扑布线的结果。

上述例子的结论是,17比特被详细规划成了4种不同的器件类型,代表了设计人员对层和路径流向的意图,这种意图的获取只需约30秒时间。接着就可以进行高质量的自动布线,所需时间也就10秒左右。

通过提升从走线到拓扑规划的抽象等级,总的互连时间被极大地缩短了,而且在互连开始之前,设计人员对密度和完成设计的潜力有真正清晰的理解,比如为何将走线保持在设计的这个点上?为什么不继续规划并在后面增加走线?完整拓扑的规划何时进行?如果考虑上述例子,一个规划的抽象就能与另一个规划一起使用,而不是与具有许多线段和每个网络上有许多过孔的17个单独网络一起使用,在考虑工程变更命令(ECO,Engineering Change Order)时这个概念尤其重要。

工程变更命令(ECO)

在下面这个例子中,FPGA的引脚输出还没有完善。设计工程师已经将这个实际情况告知了PCB设计人员,但由于进度方面的原因,他们需要在FPGA引脚输出完善之前尽可能推进设计的进度。

在已知引脚输出的情况下,PCB设计人员开始对FPGA进行空间规划,在设计人员完成规划的同时还要考虑从其它器件引线到FPGA。本来IO被规划在FPGA的右边,但现在却位于FPGA的左边,造成引脚输出与原始规划完全不同。由于设计人员在更高层抽象工作,他们能通过删除移动FPGA周边所有走线的开销来适应这些变化,代之以拓扑路径的修改。

然而,受影响的不只是FPGA;这些新的引脚输出也会影响从相关器件出来的引线。为了适应扁平封装的引线进入路径,该路径的末端也要移动;否则将导致走线的双绞扭曲,从而浪费高密PCB上的宝贵空间。针对这些比特的扭绞需要给走线和过孔留出额外的空间,在设计最终阶段这种要求可能无法得到满足。如果进度比较紧张,不可能对所有这些走线做出这样的调整。关键是拓扑规划提供了更高层的抽象,因此实现这些ECO要容易得多。

遵循设计人员意图设计的自动布线算法所设置的质量优先级要高于数量优先级。如果确定存在质量问题,让连接失效要胜过产生一个质量劣等的布线,这样做是非常正确的,理由有两个。首先,连接一个失效连接要比清除这种具有不良结果的走线和其它自动布线操作的走线要容易一些。其次,设计人员的意图得到了贯彻,并让设计人员去决定连接的质量。不过,只有当失效走线的连接相对简单和局部化时,这些观点才有用。

布线器无法百分之百地实现规划连接就是一个很好的例子。此时不能牺牲质量,而是允许一些规划失败,从而遗留一些未连接的走线。所有走线都通过拓扑规划做了布线,但不是都引到了元件引脚。这样可确保给失效连接预留一定的空间,并提供一个相对容易连接的连线。

本文小结

拓扑规划是配合具有数字信号PCB设计流程的一种工具,设计工程师对该工具很容易上手,不过它也具有针对复杂规划所考虑的特定空间、层和连接流功能。PCB设计人员可以在设计之初使用拓扑规划工具,也可以在设计工程师获取到他们的IP后使用,具体取决于采用这个灵活工具的对象,以便最好地适应他们的设计环境。

拓扑布线器只是简单地遵循设计人员的规划或意图来提供高质量的布线结果。当面对ECO时,拓扑规划要比单独的连接操作起来迅捷得多,因此能使拓扑布线器更快地采纳ECO,从而提供快速精确的结果。

-

PCB设计布线通道计算和设计规划2017-09-07 4277

-

利用IP以及拓扑规划和布线工具提高PCB设计效率2018-08-30 1282

-

如何规划PCB设计布线层数2018-09-20 2010

-

传统的PCB设计方法2018-11-27 1768

-

PCB设计中的自动布线和手动布线2019-07-10 7420

-

PCB设计中,有哪些布线规则?2019-08-01 4081

-

充分利用IP以及拓扑规划提高PCB设计效率2010-10-07 559

-

利用IP以及拓扑规划的PCB设计流程2010-07-15 984

-

PCB自动布线与流水灯PCB设计2016-06-17 1420

-

如何实现高性能的PCB设计工程2019-07-29 1542

-

PCB设计中,快速消除PCB布线的方法步骤2019-07-21 30807

-

PCB设计过程和提高布线效率的步骤2019-08-02 4880

-

PCB设计人员需要掌握的技能2020-09-08 5239

-

PCB设计自动布线2种方式分享2020-12-29 8754

-

PCB设计后期自检要点2020-11-02 4190

全部0条评论

快来发表一下你的评论吧 !