高速电路信号传输线路的问题分析

EDA/IC设计

描述

前言

类似CPU等超高速、高频电子组件相继问世,过去经常被忽视的整合问题,例如信号传输波形的优化,最近成为非常重要的课题之一。电子组件动作高速化使得封装上必需面对更多短期内不易获得解答的挑战,因此利用模拟分析作事前的检讨与对策,成为设计上不可欠缺的手法。所谓超高速、高频化具体而言例如PC、PDA、因特网、光通信、无线LAN等电子产品,事实上已经成为日常生活中的一部份。

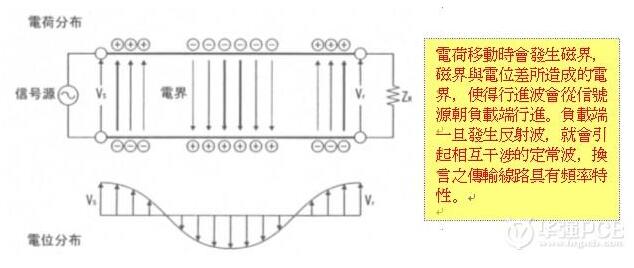

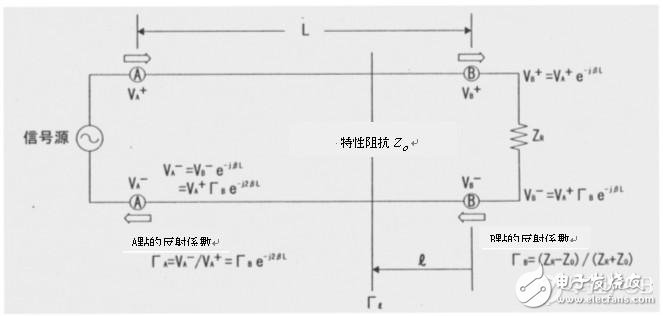

传输线路的电荷与电位分布

线路传输高频信号时,线路长度与信号频率波长两者的微妙关系已经成为无法忽视的课题,例如传输线路会会因频率会呈现天线效应产生噪讯放射现象,进而影响电子机器正常动作等等。图1是每单位波长的传输线路特性,由图可知负载端出现的信号振幅与信号源的振幅相同时,信号的位相则呈现 延迟,假设该信号是高频波时,图1的振幅与位相会因传输线路的位置产生差异。虽然理想状态希望信号源的振幅、位相与负载端完全相同,不过高频波一旦产生上述差异时,就无法忽视两者的关系。

图1 传输线路的电荷与电位分布

当传输线路长度增加时,即使是低频波同样会因信号波长产生与上述相同且无法忽视的问题,例如频率为1KHz时是300Km,依此推算祇要超过300Km,低频波也会产生相同的天线效应与噪讯干预现象。这正是影响导体长度的波长越来越高频化之后,传输线路的设计也越来越困难的主要原因。一般认为传输线路长度与波长的关系大约是1/100以上 的 ,也就是说传输线路的长度低于波长的1/100以下,理论上就不会产生上述困扰,然而实际上不可能有如此长度的传输线路。

如图1所示如果两线路之间产生电位差,两线路之间就会发生电界,随着电荷的变化就会出现高频波的流动(亦即电流),它可视为磁界的变化,因此随着电界与磁界,行进波会流入负载端,如果传输线路的阻抗为不整合状态时,负载端就会产生反射波(亦即反射电力),造成行进波与反射波相互干扰,进而在传输线路上形成类似静止状的波形山谷(亦即定常波),使得传输线路具有频率特性。当传输线路为 时,干涉所产生的波长成为共振状态,传输线路就成为发射噪讯的天线,进而严重影响电子机器的正常动作,也就是说具有电界、磁界的高频波电流的流动所产生的电磁界,经常超越预料将强烈的电波放射至周围空间。

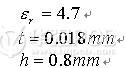

传输线路与反射系数

如果将传输线路、信号源与负载端加以整合,就不会发生反射与信号劣化等问题。在高频波领域不能用低频波的思维将传输线路当作0奥姆阻抗,而是必需将它视为一种电子组件(特性阻抗ZoΩ),也就是说传输高频信号整合时驱动侧的IC祇能见到传输线路的 负载,为了高速驱动特性阻抗Zo具有50~100Ω的负载,因此设计上必需考虑驱动能力所造成的负担。

负载,为了高速驱动特性阻抗Zo具有50~100Ω的负载,因此设计上必需考虑驱动能力所造成的负担。

【计算例1】

试算25pF的负载,1ns的时间内提升至5V时,驱动侧的需求电流 。

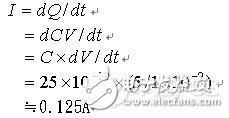

电流 可由下式求得:

亦即的变化越快所需的电流I也越多,相对的噪讯也越大。事实上电路要完全取得整合相当困难,反射所产生的阻抗不整合,会因信号源的电力未被负载消耗,变成反射波折返至信号源。由于反射波是朝着信号源的传输线路方向传播,随着传输线路的长度改变,信号源侧与负载侧的位相差异也越明显。

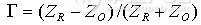

一般而言该反射系数并非电力的反射系数,因此它是使用表示负载端入射波与反射波两者的比,亦即使用电压反射系数 表示,电压反射系数

表示,电压反射系数 可由下式求得:

可由下式求得:

实际上电路的负载 几乎不会是纯阻抗而是复素数,因此反射系数也成为复素数。

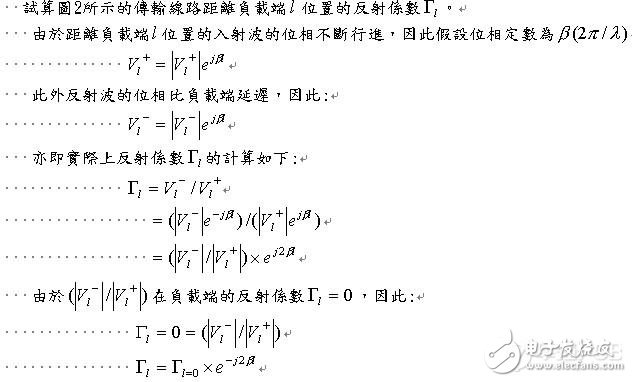

【计算例2】

由上述计算结果获得以下结论:

1.如果将负载的阻抗视为一定值时,反射系数会随着位置变化。

2.传输线路上距离负载端 位置的位相差会有 的差异。

3.反射系数会变成 的位相差。

换言之从信号源观之反射波比入射波延迟 ,因此反射系数是反复波长λ的1/2周期,而负载阻抗则呈现不断变化状态。

图2 传输线路与反射系数的互动关系

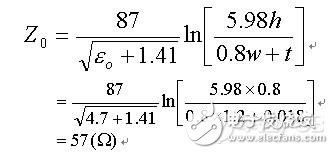

Strip line的信号延迟

图3是印刷电路板Strip line的特性阻抗Zo关系式与传播延迟时间 的关系式。假设电路板的条件分别是:

1.特性阻抗 的计算如下示:

2.传播延迟时间:

图3 印刷电路板Strip line的特性阻抗Zo ,与传播延迟时间 的计算公式

的计算公式

【计算例3】

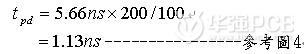

试算长度为200mm strip line所构成的印刷电路板,从信号源到达负载所产生的信号延迟。

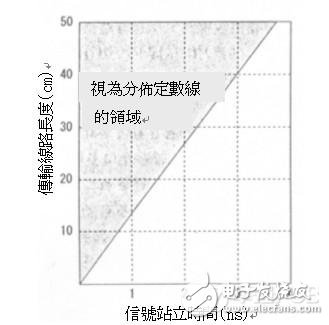

假设因传播造成的信号延迟时间为tpd,则tpd 的计算如下:

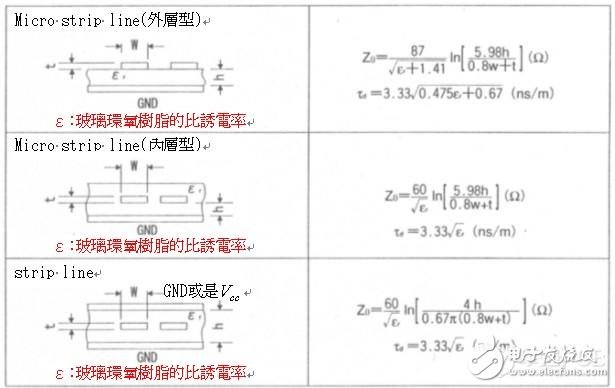

图4 信号的延迟时间

如果传输线路发生信号延迟时,其关系式可由传输线路的长度与数字信号站立时间,两者概括性关系求得:

2Td》tr------------------------------(1)

也就是说2Td是信号在传输线路往返的时间,如果2Td比数位信号站立时间tr更大时就会产生问题,此时会因反射出现over shoot与跳动(bouncing)现象,成为电路误动作的因素之一。假设传输线路的长度为l时,信号延迟时间Td的关系可用下式表示:

Td= x l--------------------------(2)

x l--------------------------(2)

假设高速IC的传播延迟时间为1ns,往复线路的长度为200mm,从上述式(1)与式(2)与计算例3可知,线路的长度是造成传播延迟主要原因,因此必需进行阻抗整合,设法对策避免产生反射波。

防止传输线路反射的方法

如上所述防止反射最佳方法是将信号源输入与输出端的阻抗,与传输线路的特性阻抗整合,也就是说在传输线路上形成相同的特性阻抗。主要考虑是因为从输出到输入之间,一连串的传输线路上若有阻抗非连续点时,该位置便会产生反射,因此即使频率有变动,稳定无变动的阻抗与输出入阻抗成为理想的驱动条件。常用的特性阻抗 计算公式如下:

----------------------------(3)

----------------------------(3)

由式(3)可知该计算式毫无频率概念,亦未包含消耗电力的阻抗与电导(conductance)等项次,因此传输线路没有任何损耗,可说是与频率无关的理想电路,亦即利用整合的分布定数线路传输的信号,在任何位置任何切口的信号源的波形、位相、振幅完全相同。

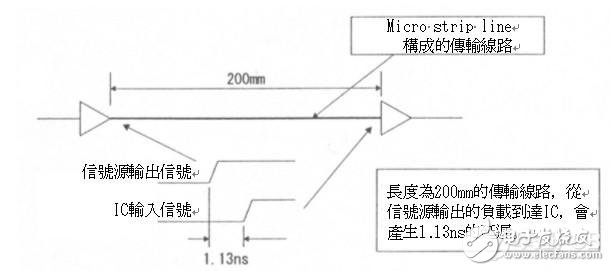

如图5所示设计上一直未受到重视的pattern导线,通常会与传输线路上的IC连接,此时比较有效抑制反射的方法如下示:

1.利用传输线路的长度进行导线layout。

2.利用终端方式抑制反射强度。

3.利用导线layout技巧抑制反射强度。

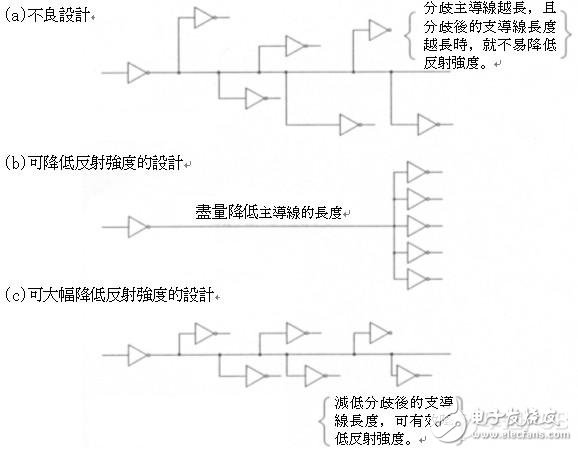

如果考虑IC/LSI的输出入阻抗时,CMOS type的输出阻抗一般为数十Ω,输入阻抗则高达数百Ω,输出阻抗值与传输线路的特性阻抗值非常近似(大约为50~100Ω),相较之下输入阻抗值就非常大,为了有效抑制反射必需在收信端进行与终端相等的特性阻抗,不过基于耗电性等考虑上述方式并非上策,最好的方法是将传输线路当作集中定数线路处理,也就是说在无终端的前提下,利用传输线路的长度进行导线layout使信号能被顺利传送。传输线路使用集中定数线路或是分布定数线路,取决于数字信号的站立时间,图6是信号的站立时间与输线路长度的依存关系。

图5 分歧导线的特性

图6 分布定数线路的特性

设计时祇需读取图6的IC信号站立时间与传输线路的长度,就可在既定的传输线路长度范围内,与无终端处理前提下有效抑制反射强度。需注意的是上述是不需考虑分布定数线路的设计,如果传输线路需作分布定数线路考虑时,就需在收信端撷取终端并设法抑制反射强度。虽然反射起因于linking与over shoot以及under shoot,不过抑制放射反射时必需降低产生噪讯的高频波成份,例如降低linking电流可以有效减缓噪讯的level。

大部分的情况要设计理想状态的传输线路几乎是不可能,不过以理想状态的概念设计电路却非常重要。虽然实际误差可透过检讨与调整补正,如果该误差是因为设计不慎就存在的潜伏因子,最后则会面临无法挽救的窘境。如图5(a)分歧导线layout,信号波形很容易因反射波造成杂乱波,这意味着pattern导线长度的差异造成不整合进而引发杂乱波,会随着分歧数量的变动与噪讯相互干扰更加速波形溃散。图5(b)的导线虽然仍有反射波的问题,但不论是IC输入端或是信号源的波形都很均匀,加上无位相差异因此反射波干涉造成的波形杂乱相对的大幅降低,这种情况就可利用dumping阻抗改善波形。

基板层的结构对高频电路的性能具有决定性的影响,基于成本考虑双面电路基板成为设计者最爱,但是值的注意的是双面电路基板并无法确保电源与grand稳定性,一旦发生问题几乎没有充分的裕度可作改善,尤其是10MHz以上高频电路最好能改用多层板。此外高密度封装电路基板经常使用BGA/CSP等方式,虽然电源与接地层看似均匀,实际上有关低阻抗的对策却经常被忽略,其结果极易造成特性阻抗溃散,因此事前的检讨变得格外重要。

随着电路高速化,数字电路经常发生误动作与精度误差等问题,因此设计时必需特别注意data sheet记载的细项tinning规定,因为tinning error往往是误动作的主要原因。此外高速化后clock的周期会变短,加上输出入之间信号的延迟传输,造成metastable与tinning偏差等现象。使用高速IC组件时则需注意switching噪讯与ground bounce的出现,同时在pattern导线layout时透过精密检讨,设法避免发生上述机能性的障碍。

信号传输延迟

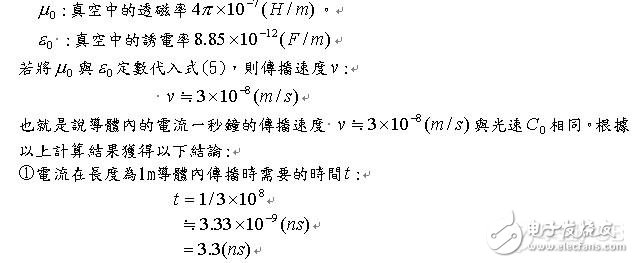

(1)流动于导体内的电流传播速度

频率f与该信号变化1周期T所需要的时间由下式表示:

T =1/f(s)--------------------------(4)

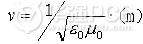

流动于导体内的电流一秒钟的传播速度v可由下式表示:

---------------------(5)

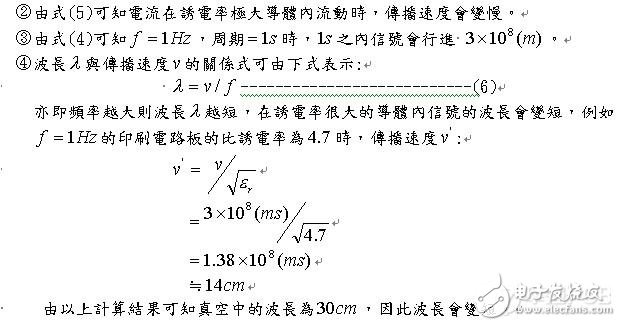

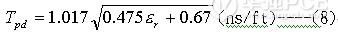

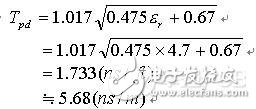

印刷电路板的比诱电率为4.7 时,传输延迟时间 :

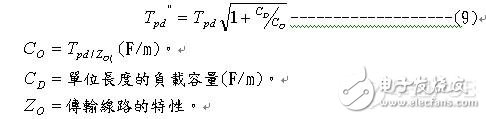

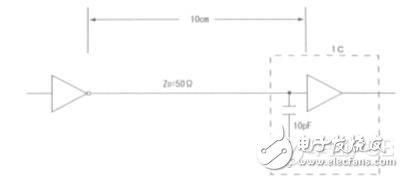

传输线路上有容量性负载时会影响传输延迟时间 “,它的传输延迟时间 是用下式表示:

【计算例4】

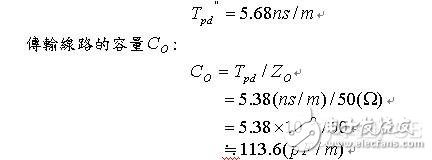

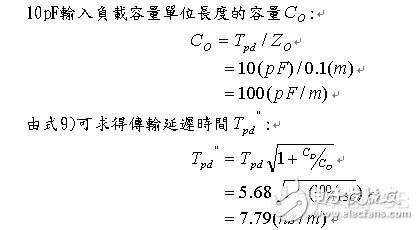

如图7所示由micro strip line所构成的传输线路,从该线路(特性阻抗为)距离信号端100mm的位置具有10pF输入负载容量时,试算它的传输延迟时间 ”。

如以上介绍利用micro strip line传输延迟时间 “时:

由于连接10pF的负载,会增加7.79-5.68(ns/m) 的传输延迟。传输线路的长度对电路阻抗与位相具有重大影响,以计算例4而言传输线路究竟要使用分布定数线路,或是集中定数线路,传输线路的长度成为判断上重要的指标。如果将波形动乱列入考虑时,无终端整合可传输信号的界限传输线路长度Lmax 关系示如下所示:

tr :信号的站立或下降时间(ns)

由式(10)获得以下结论:

※※信号的站立时间越缓慢且传输延迟时间增大时,无终端整合可传输信号的传输线路长度可延长。

图7 micro strip line所构成的传输线路的传输延迟时间

IC的动作速度与误动作

为了要使电路的动作特性能符合预期目标,不单是组合封装技术的问题,包含电路设计上若有任何疏失或是欠缺周详考虑,经常事后需耗费庞大资源解决问题,其中又以IC的动作tinning error造成电路误动作的比例最多。

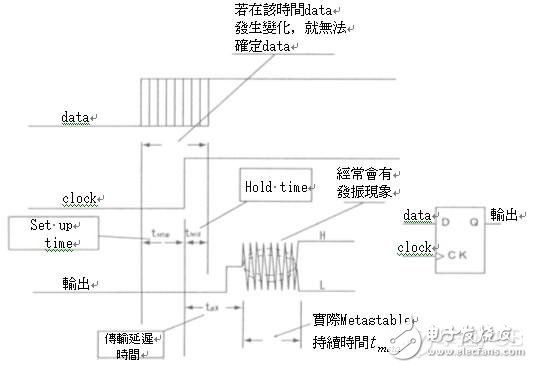

(1)Metastable

如图8所示flip flop IC内具备set up time tsetup 与hold time thold 两种规格,如果没有充分的tinning裕度维持tsetup 与thold 时间,data一旦发生变化就无法确定是输出的H或是L,形成不稳定状态进而产生如图8所示的须状脉冲波形,往往还会有发振现象,这种状态称为「Metastable」。

图8 Metastable现象

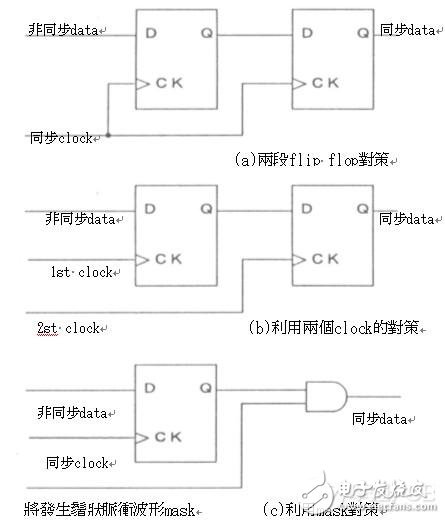

比较有效的对策共可分为三种,具体方法如下所述:

1.flip flop分成两段使用

如图9所示即使因Metastable发生须状脉冲波形,利用两段flip flop方式(以下简称为FF)亦能去除下个tinning,具体方法是用第一段flip flop读入数据并将数据latch,接着再用第二段flip flop输出数据,如此便可去除须状脉冲波形。

2.图9(b)的对策是用第一个clock(1st)将数据latch,再输出时间稍为延缓的数据(利用共通clock将数据latch时,会选则具备所有数据的tinning)。

3.图9(c)的对策是在发生须状脉冲波形期间使用mask方式,由于发生须状脉冲波形的时间随着IC高速化会变得很短,因此clock的周期很快的场合,使用高速IC反而变成非常smart。

事实上即使因Metastable造成误动作,不过它的发生机率却比预期低(例如一周或二周发生一次左右),因此大多数的情况都无法追究真正的发生原因。由于高速clock电路会有信号延迟传输的困扰,因此设计上必需设法满足set up time与hold time规格。此外Meta stable经常因电源与温度发生变动也是必需加以防范。

图9 Metastable的对策

(2)tinning偏差

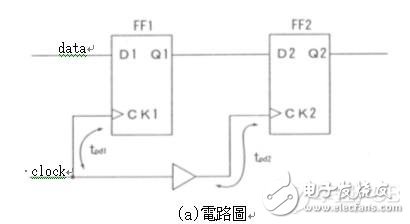

如果未预留考虑tinning偏差裕度时,经常会成为电路误动作的原因。如图10(a)的电路所谓tinning偏差(skew)是指FF1的clock CK1的延迟时间tpd1 ,与FF2的clock CK2的延迟时间tpd2 两者的差亦即tpd2-tpd1 。

图10(b)表示可忽略tinning偏差亦即tpd2-tpd1≈0,换言之从输出端子祇输出IC规格书标示的信号传输延迟时间内的延迟信号,实际上由于IC的延迟与pattern长度所造成的影响有大小区分,因而产生clock之间产生延迟时间差异,如果延迟时间差异过多时,会发生数据异常现象,此时FF2的clock无法维持读入的FF1输出数据set up时间与hold时间,最后导致FF2的输出变得非常不稳定。

图10 可忽略tinning skew 时shift resistor的输出特性

【计算例5】

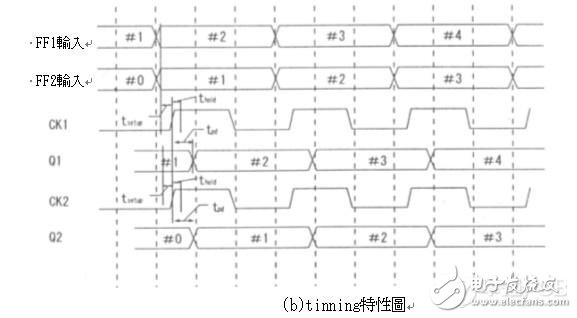

如图11(a)所示shift resistor电路上的复数个FF1,连接于相同的clock line,而clock line基于驱动能力的考虑,因此被连接于buffer上。请检讨该电路的问题点与改善对策。

※问题点

图11(a)的电路clock line上,a、b、c的延迟时间依序加算配置导线,因此tinning skew会变得非长大,该导线与电路不易维持set up time与hold time,而且有可能发生误动作甚至不会动作的窘境。

※改善对策

如图11(b)所示为了抑制clock之间的信号传输延迟时间,因此缩短导线的长度以维持set up time与hold time。

图11 tinning skew的问题点与改善对策

(3)cross talk

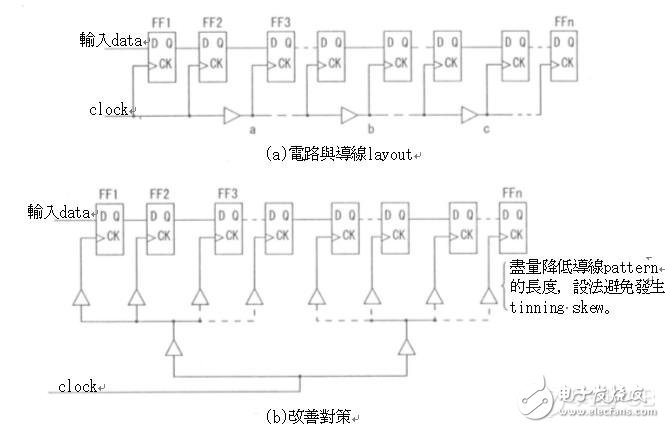

如图12所示由于数据线(data line)产生的cross talk,使得噪讯渗入其它信号线,往往是造成电路误动作的原因之一。数据线有复数个数据同步变化,所以电流变化相当大,如果噪讯渗入信号线就会造成重大影响。如果该信号线是同步化逻辑电路时,即使受到cross talk噪讯干扰,祇要同步化tinning的噪讯未渗入,也不会造成电路误动作。相隔很近的信号线同步化对抑制噪讯也具有很好的效应。

图12 同步化的动作机制

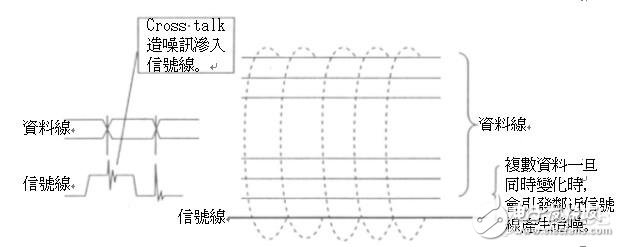

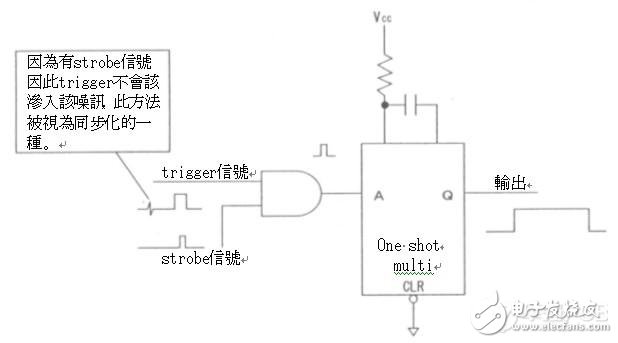

图13是将one shot multi vibrate同步化,提高对外部噪讯的noise margin方法。

基于组立作业等考虑因此必需尽量缩短电路板pattern的导线长度,也就是说高密度导线layout技术,对pattern的导线最短化具有实质的含意,除此之外回路(loop)面积的最小化也很重要,如果信号线是由micro strip line所构成时,便可大幅降低cross talk,而四层板对构成电源与接地(ground)面具有很大的帮助。

图13 同步化的动作机制

(4)ground bounce

数字电路的电源与接地流有CMOS贯穿电流与充放电电流等高频过渡电流,在ground

的组件ground一般是用下列式子表示:

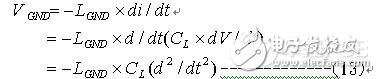

图14是IC switching时表示等价电路的诱起电力、形成inductance、负载容量。假设流动于负载容量 的电流,施加于容量的电压为 时:

利用式(11)、(12)计算诱起电力 时:

由式(13)可知为了降低grand bounce

*抑制电压的振幅与时间变化振幅,增加dV/dt。

*降低负载容量。

结语

(以上介绍有关tinning error与电路误动作的互动关系,由于调查tinning error造成电路误动作的原因必需耗费庞大资源,因此设计高速电路时除了慎选IC组件之外,事前密致的检讨与模拟分析,成为无法忽视怠慢的过程。

-

信号在传输线路上的传播机制2025-10-09 2618

-

简述光纤传输线路的基本组成2024-08-09 2838

-

什么是传输线?什么是信号完整性分析?为什么传输线要测试差分信号?2023-10-23 1911

-

高频传输线讯号分析基础2023-10-19 2036

-

高速电路信号完整性分析与设计--传输线理论2022-02-10 1085

-

PCB高速数字设计和信号完整性分析的传输线理论知识详细说明2020-04-02 1314

-

传输线有什么特征?2019-08-12 5391

-

什么是传输线的分布模型2019-07-24 1746

-

传输线效应是什么 如何减少传输线效应2019-01-22 13659

-

PCB传输线原理2018-11-23 2036

-

基于高速PCB传输线建模的仿真2018-08-27 2766

-

高速电路传输线效应分析与处理2009-11-17 1072

-

传输线的特性阻抗分析2009-09-28 9648

全部0条评论

快来发表一下你的评论吧 !