DFM软件在PCB设计中的应用

EDA/IC设计

描述

面对电子产品向小型化、高密度和高速度发展,PCB设计的复杂程度大大增加,如何有效地对复杂PCB设计进行全面的质量控制是我们面临的一个课题。阐述了引入VALOR的Trilogy 5000软件后,对产品PCB设计的全流程进行DFM(可制造性分析技术)应用的过程,并与传统的PCB设计和检查方法进行了比较。该PCB设计审查机制可协助设计、工艺、制造和质量检查人员进行产品全生命周期过程的质量控制,作为PCB设计完成到投产前进行自动评审的有力工具,它提高了PCB设计的一次成功率,缩短了产品的研制周期。

首先给大家推荐“全球首款国产专业DFM分析软件”,这是免费使用,且能分析制造中的设计不足的软件,很多工程师开始始人。

随着电子产品的高速发展,PCB设计中已大量选用BGA、QFP、PGA和CSP等高集成度器件,PCB的复杂程度也大大增加,随之而来的PCB的设计和制造难、测试困难、焊接不良、器件不匹配和维修困难等生产问题。这样导致整个产品工期延误,研制周期加长,成本增大,产品返修率高,并且产品可能存在质量隐患。这样的产品同时更无法满足军工产品时间短、高可靠和高稳定性的要求。

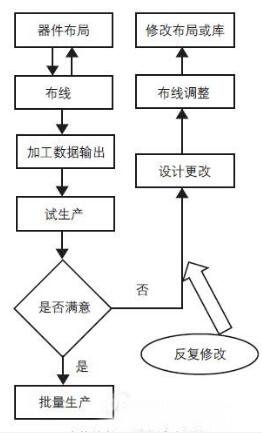

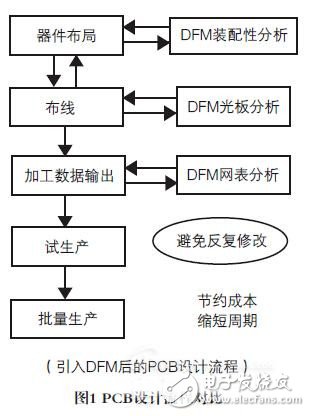

在实际设计生产过程中,我们通过对VALOR软件Trilogy 5000 DFM功能的应用,引入“可制造性设计”理念,将产品设计质量重心前移。在设计阶段融入制造规则,建立新的PCB设计流程,如图1所示。以减少设计的变更带来的周期延长,保证生产质量和效率。在制造前期解决或发现所有可能的质量隐患,将产品研制的迭代次数降到最低,减少成本,提高产品的市场竞争力。也使得产品质量与所用的设计软件无关,与设计人员的水平无关,让企业进入规范化管理。

1、DFM技术概念

DFM技术,即可制造性技术,主要研究产品本身的物理设计与制造系统各部分之间的相互关系,并把它用于产品设计中以便将整个制造系统融合在一起进行总体优化。DFM技术可以降低产品的开发周期和成本,使之能更顺利地投入生产。换而言之,DFM就是要在整个产品生命周期中及早发现问题并加以解决。

2、DFM软件应用

Trilogy 5000 DFM分析主要包括光板制造设计分析、装配分析和网表分析等。

2.1分析准备

DFM的分析准备工作是非常重要的,是所有分析的基础,也是DFM分析是否能够进行下去的前提。以下五项就是主要的准备工作。

2.1.1通过EDA工具输出PCB设计所生成的ODB++数据

ODB++数据是业界标准的数据格式,它将传统的加工装配数据如PCB的网络信息、层叠关系、元件信息、提供给厂家的印制板加工信息、物料信息、各种生产数据包括贴片程序和测试程序等集中在一起。通过EDA设计工具中嵌入的ODB++数据生成器来产生。为VALOR Trilogy 5000 DFM提供完善和真实的检查依据。

2.1.2基于每个PCB设计的完整BOM清单

读入BOM清单即是将PCB设计的BOM整理为VALOR Trilogy 5000系统可认的BOM形式,并对应每一个器件的厂家和VPL封装库。批量生产(传统的PCB设计流程)在对应BOM清单时我们遇到的问题是,我们的 EDA工具自动产生的BOM与企业的物资采购系统一致,而物资采购系统为了可读性,将所采购的国产器件的厂家名称一栏,大多以中文形式体现,器件型号中一般也会带有一些标注性的中文,这对于VALOR软件中BOM清单的匹配来说,对应厂家这一环节是无法实现的。通过反复的实验,考虑到物料编码是对应每一种器件的,不会发生不同器件用一个物料编码的情况,具有唯一性。所以在BOM解读时我们就将物料编码的属性设为MPN(Manufactor Part Number厂家编号),而将厂家和器件型号两栏的属性设为Describe(描述),将本单位的代号属性设置为Manufactor(厂家),所有的器件型号对应的厂家只有一个,就是本单位的代号。这样实施以后,大大简化了对应BOM清单的步骤,而且巧妙地避免了对应厂家时产生的厂家名称不准确和中文不识别等诸多一直困扰我们的问题。

读入BOM的过程,可以验证PCB设计BOM清单的准确性,并较早发现PCB设计中所用的封装与元器件的实际器件库不匹配的现象,并生成检查结果的报告,这对于PCB设计来说是一个很好的先期检查过程。如果企业的BOM格式是一定的,就可以通过制作模板来再次简化读入BOM的过程。

2.1.3建立基于企业物料编码的VPL实际封装库

通过查阅器件手册,利用VALOR Trilogy 5000的建库工具PLM来建立每一个器件的实际封装库。VPL库包含制造商的品牌、规格型号和元器件的实际封装尺寸。VPL库不同于PCB设计的封装库,是描述元器件实际尺寸的三维立体元器件封装库。

在VPL封装库的命名上我们采用VPL默认的命名方法,但在这个封装的属性中加入U_PCB_PACKAGE属性,将这个属性的值写入EDA的封装名称。这样做的好处是:在DFM分析时点击要关注的器件,可以很直观地看到这个器件所对应的EDA封装名称,便于有问题的封装定位和查看,节省了时间。

VPL封装库的建立是一个慢慢积累的过程,可以先从电阻和电容建起,利用VALOR公司提供的COPYPART软件,将一种封装的电阻或电容整理到一个Excel表中,通过批处理运行,可以将所有表中器件的VPL封装库一次性建好。一般单位的EDA封装库里的几千种封装,其中三分之二应该都是电阻和电容组成,如果通过上述方法,将电阻和电容先建立好,为VPL库的建立奠定坚实的基础和信心;其次就应该建立一些重要器件如接插件和CPU等器件,这样做可以保证每块印制板在做可装配分析后,投产的印制板至少不会出现不可用的情况;再其次应该建立较为贵重的器件的VPL封装,这样保证了含有贵重器件印制板投板的一次成功率,如果因为封装错误导致贵重器件在装配过程中遭到破坏,对企业来说将是一个不小的损失。再下来建立常用器件的VPL库,随着VPL库的慢慢充实,VPL库逐渐建立起来,这样大多数印制板就可以进行可装配性分析了。

2.1.4定义器件的属性

作为所有检查的依据,ERF规则管理库的建立是至关重要的。在实际设计生产中,我们汇集了印制板生产厂家的制造规范,并对设计单位的设计规范及生产工艺规范进行了整理,逐条分析比对,建立了符合本单位的ERF规则管理库,并在实践中对它逐步完善。ERF规则管理库包括光板分析规则管理库和装配性分析规则管理库。

2.2可装配性设计

在印制板的PCB布局基本完成的情况下:

1)导入ODB++数据;

2)导入该设计的BOM清单;

3)调用与已建立的物料编码相对应的VPL实际封装库及ERF装配性分析规则管理库;

4)根据不同的印制板装配要求,设置相应的装配工艺,并对印制板划分出工艺区域;

5)定义器件属性;

6)进行装配性检查,生成了可视化图形,并自动生成可装配性分析报告。

可装配性检查包含了元器件封装检查、标识点检查、元件分析、焊盘分析、焊盘和引脚对应关系分析、测试点分析及模板开口分析等检查。上述检查项目都包含子项目,如元件分析包含有元件间距、元件方向、元件高度、元件丝印和元件禁布区等。通过检查,可以看出元件与PCB焊盘不匹配、元件碰撞干涉和元件焊接不良等问题。

随着PCB设计的复杂度越来越高,一块印制板会含有上千个器件,插装器件和表贴器件都分布的十分密集,在印制板布局布线完成后,要对这上千种器件的丝印进行调整,也是一个不小的工作量,而这种繁杂的工作难免会出现位号放的位置不合理甚至颠倒的情况。而普通的EDA设计软件是不提供这种问题的检查项的,所以一旦这种问题发生以后,往往在印制板加工和器件安装后,经过调试才能够发现。给后期的装配和调试带来了很多麻烦,耽误了产品的研发进度,带来了经济损失。通过元件分析,图2所示的位号错位的问题就会很轻易地被检查出来。替代了PCB设计人员的人工检查过程,提高了效率,也为我们的PCB设计质量提供了保证,该项检查对我们的PCB设计是非常有意义的。

图2位号错位

元件间距分析为我们PCB设计时经常遇到的器件间距过近的检查提供了方法。不同元器件之间的间距要求是不同的,高度也不同,可以通过ERF和器件属性的对应表来设置。我们通过调用VPL库,分析各类元件的不同间距是否符合要求。如图3所示,两元器件间距太近,导致过波峰焊时由于两器件高度不一,矮元件管脚上锡不足,可造成空焊或虚焊。

图3 两元器件间距太近

元件封装分析,主要是检查PCB上元器件封装的正确性。该项检查尤为重要,在PCB设计中元器件封装对应错误或者封装库建立错误直接导致加工好的印制板无法使用,只好重新生产。这不仅浪费成本,降低了效率,更是失去了市场的竞争力。

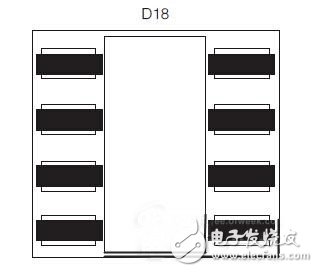

如图4所示,灰色框为VPL库的实际器件大小,对比下方黑色PCB设计数据,很明显封装的焊盘设计不合理,焊盘焊接部分预留太短,且焊盘宽度不够,容易导致焊接过程中虚焊。

通过可装配性分析的应用,提高了PCB设计的准确性。由于我们在ERF规则中融入了加工厂家的许多加工要求,所以也就减少了与加工厂家的来回沟通的次数,提高了效率和印制板投产的一次成功率。

图4焊盘设计不合理

2.3网表分析

在PCB布局布线完成的情况下,提取设计时所生成的ODB++数据,进行网表分析。通过对比标准网路,网路完整性的设计错误(开路或短路)会很直接地在图形中标识出来。即使电源地的开路和短路也可以通过转换成Pin-Point的检查模式精准地报告出来。该项功能可以帮助PCB检查人员发现因为经验不足造成的PCB检查不全面的问题,使PCB检查人员可以在产品投入生产前验证最终的设计数据完整性。

2.4光板分析

依据ERF的光板分析规则管理库,提取PCB设计所生成的ODB++数据,进行PCB光板可制造性检查。PCB光板分析主要包括钻孔分析、信号分析、电源地层分析、阻焊分析和丝印分析等。

由于不同的PCB设计人员设计的水平和方法不同,所以在PCB设计过程中,由于经验的不同,导致设置布局布线的规则不同,设计的质量也有很大的差别,如何使送到加工厂家前的PCB质量受到控制,我们将所有的设计要求和规范,通过设置ERF光板分析规则管理库的形式,体现在光板分析的各项检查中。

例如在PCB设计中,隔热花盘的大小要根据不同电源地的功率要求来设置,如果隔热花盘太小或者堵塞,就会造成焊接时散热太快、可焊性差和连接无法满足功率要求等问题。但是PCB设计软件只要达到连接线宽要求是不提示错误。

如图5所示,是隔热花盘太小的情况,光板分析会根据ERF规则的设置检查,分级提示,是否满足了散热和连接功率的要求,避免了因经验等因素造成的错误。

图5隔热花盘太小

另外,我们的PCB设计工具只提供印制线与焊盘之间的检查项,并不提供印制线与阻焊之间距离的检查。如图6所示,光板分析后,能够发现印制线与阻焊过近的问题,避免了生产出的印制线漏铜,而铜氧化后会直接影响信号的质量。这些长时间使用后才可能暴露出来的质量问题,也是我们PCB检查时应该考虑的。

图6制线与阻焊过近

光板分析中,如果将每一个检查步骤拷贝制作成检查表(Checklist),便可简化各项检查的操作,还可以指定快捷键,按一个按键就能够进行光板分析,大大减少了检查的工作量。

2.5软件的同步

一旦EDA数据库被阅读成ODB++,Trilogy 5000就可以提供智能图形连接到EDA工具中。利用软件设置的快捷键,设计人员可从Trilogy5000画面直接同步到EDA工具上显示的同一图框及位置,这为我们在EDA工具方便快捷地找到错误点,提供了很大的便利。

3、DFM软件与PCB设计软件规则检查功能的区别

DFM软件工具是基于实际生产规则进行的,而PCB设计软件的检查只基于设计规则,是两个不同领域的工具。

PCB设计软件内的分析一般应用于设计部门,在

设计后端对数据进行检验,确保无违反电气规则的问题出现,侧重于逻辑功能的实现;DFM则应用于工艺部门和生产装配部门,确保设计数据满足所有加工制造、装配和测试的要求。

PCB设计软件中相关模块光板可制造性分析的功能相对简单,规则不够丰富,如可装配性分析和可测试性分析等工具都不具备。

4、结论

DFM软件为我们提供了全面的PCB设计自动化评审方案,使我们的产品更加规范化,即使是不同的PCB设计软件,不同经验的PCB设计人员设计出来的产品,质量都得到了保证。使得工艺评审并行参与到产品设计的各个阶段,在设计阶段解决和发现所有可制造性质量隐患,大大提高了我们的PCB设计质量。印制板的加工、工艺管理及电装工艺效率大幅度提升,产品的质量得到了提高,降低了产品的成本和研制周期,增加了产品的竞争力。

此外,DFM软件的应用,也有利于流程的标准化,通过DFM的规范,将设计和制造部门有机地联系起来,同时达到生产测试设备的标准化。基于目前的产品制造外包的趋势,将能够实现产品技术的专业化转移,有利于企业实现更大的发展。

-

PCB设计中常见的DFM问题2024-10-25 2609

-

DFM技术在PCB设计中的应用2023-10-20 519

-

PCB设计DFM可制造性设计.zip2022-12-30 746

-

【8.25直播】PCB设计电源处理及整体PCB DFM检测2021-08-20 14293

-

华秋DFM-pcb设计专业分析软件-LLZL2021-07-30 1319

-

DFM-专业PCB设计分析软件2021-07-21 1295

-

华秋DFM-一键检测PCB设计隐患专业软件2021-07-16 1465

-

请问隐藏在PCB设计中的DFM问题有哪些?2021-06-17 1834

-

影响PCB设计的一些DFM问题2020-11-20 5762

-

在促成PCB设计的所有要素中必不可少的要素 DFM2020-09-24 3374

-

PCB设计DFM可制造性设计2020-04-24 6986

-

深入探讨DFM在PCB设计中的注意要点2014-10-24 3920

全部0条评论

快来发表一下你的评论吧 !