PCB电路的串扰设计原则分析

EDA/IC设计

描述

随便问一位硬件设计人员:松散耦合的带状线对跟紧密耦合的带状线对,哪一种会带来更少的通道间差分串扰。99%的人会选择后者。但他们错了。

目标阻抗和横切面

在超过10Gbps的高速串行连接中,损耗是影响互联设计的主要因素。不论介质损耗有多小,导体损耗仍然是主导地位。影响导体损耗的唯一设计因素是介质宽度。

这意味着在高速数据通道中,应尽一切可能使用可用的最宽的线。大多数高密度多层板上,在互连线密度或者主板总厚度尚未达到可用的限制时,最大可用线宽约为7mils。

如果目标差分阻抗是100Ohms,线宽是7mils。改变差分对之间的耦合就会改变差分阻抗。差分对之间间距越小,差分阻抗就越小。在带状线拓扑结构中,为了弥补这种情况(差分对之间靠近而阻抗值变小),电介质层的厚度则会相应的增加。

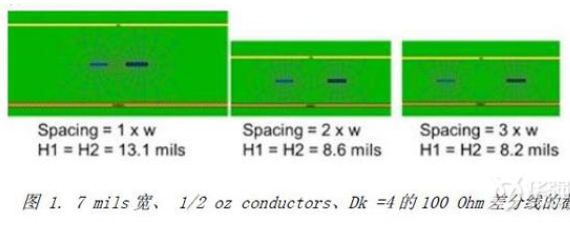

图一展示了三种不同耦合的100Ohm差分对的横截面,紧耦合,松耦合,没有耦合。

耦合跟边缘场分布

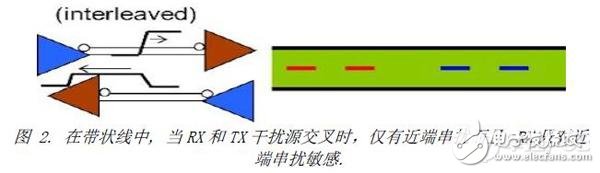

在带状线几何结构中,没有远端串扰。当TX跟RX在相邻通道中交叉时,接收端只对近端串扰敏感(接收端只受近端串扰的影响)。如图2所示。

在带状线中,两对差分对之间的电磁场边缘耦合会引起近端串扰。两对差分对之间,边缘场越强烈,串扰越大。叠层结构,除了控制差分对的差分阻抗外,也能限制边缘场并影响通道间的串扰。

返回层之间的空间越大,边缘场延伸到相邻通道上的距离就越远,通道间的串扰越强烈。层与层之间的空间是影响边缘长的主要因素,而不是两线间的耦合。

对紧密耦合的一对带状差分线,为了达到1000hm的阻抗,层与层之间的介质厚度大约为26mils,线宽为7mil,半盎司铜,材质的介电常数为4。如果差分对之间的线宽加倍,如果阻抗仍然要求为100Ohm,介质厚度应该减少到17mils。

松散耦合的差分对由于层间距更小(相比于紧耦合),减少了边缘场效应和串扰。这就是相比于疏耦合,紧密耦合会带来更多通道间串扰的原因。

建立稳健的设计原则:

串扰多大是不能接受的?大部分Spec会要求信噪比在20dB左右。这里所说的信号指的是在接收端看到的信号,不采用均衡,接收端通道中的信号会小到-10dB,在高衰减的通道中,接收端通道中的信号甚至小到-25dB,如果所有噪声只有通道间串扰,可以接受的信噪比为20dB。

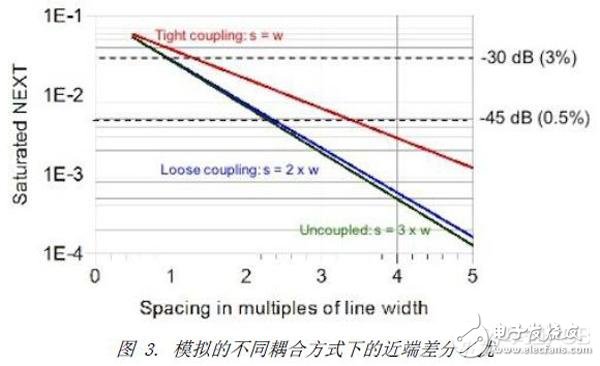

对于串扰噪声的可接受标准,这里定义了两种可接受的标准。在一个没有应用均衡技术的通道中,-30dB的通道间串扰是可以接受的底限;在高衰减的通道中,-45dB是可以接受的串扰底限。

带状线两通道之间的近端串扰取决于通道间的间距大小。通过一个2D场程序,我们可以找到设计方案来建立robust设计准则,保证近端串扰低于最大允许值。

综合各种情况,为了设计100Ohm的差分阻抗,线宽固定为7mil,铺铜为1/2盎司,介质的介电常数为4.三种耦合方式:紧耦合,疏耦合,不耦合,对应的线宽分别为1倍,2倍,3倍线宽。

如果根据并联线线宽来设计合理的线间距,我们可以设计不同的线宽值,只要能满足差分阻抗为100Ohm即可。

随着差分对的间距加大,近端串扰将随着减小。图3模拟了三种不同差分耦合方式的情况下,差分对之间近端串扰的情况。

上面一幅图帮助我们明确了robust设计准则,来保证满足-30dB和-45dB的串扰要求。

在一个没有均衡技术的路径中,信号可以(衰减)到-10dB。我们要求不超过-30dB或者3%的通道间串扰。当然,如果通道两端都受到其他通道的干扰,通道间的串扰应该会低于1.5%或者-36dB.这样他们的总功率会低于3%。

为了使近端差分串扰不超过1.5%,通道间的空间要求,对于一个紧密耦合差分对来说应该大于1.5倍线宽,对于松散耦合来说,应该大于1倍线宽。

在一个高损耗通道中,信号(衰减)可以低至-25dB,最大可接受的通道间串扰必须小于-45dB或0.5%。在最坏的情况下,当传输线路两端都有干扰源存在时,可接受的最大通道间串扰为-0.25%,或约-50dB。

从以上的设计曲线来看,针对小于-50dB近端串扰的合理设计准则,对紧密耦合差分对是保持通道间间距》4倍线宽,而对于松散耦合,是保持的通道间间距》3倍线宽。

遵守以上的设计准则,可以保证你的产品质量高枕无忧。但如果通道间的空间比以上数值更小,并不意味着你的产品不能工作,只是你最好通过自己的分析来减小失败的风险。

-

在PCB设计中,如何避免串扰?2024-02-02 2914

-

什么是串扰?PCB走线串扰详解2023-09-11 2341

-

小间距QFN封装PCB设计串扰抑制分析2022-11-04 688

-

高速电路信号完整性分析与设计—串扰2022-02-10 899

-

如何解决PCB串扰问题2020-07-19 2827

-

高速PCB设计中如何消除串扰?2019-07-25 4001

-

PCB Layout抑制串扰的3W线距原则2019-06-22 3298

-

串扰在高速PCB设计中的影响分析2019-05-29 1275

-

PCB印制线间串扰的MATLAB分析2015-12-08 553

-

PCB设计与串扰-真实世界的串扰(下)2014-10-21 3786

-

高速PCB中微带线的串扰分析2011-11-21 1270

-

高速PCB设计中的串扰分析与控制2009-06-14 753

-

高速PCB串扰分析及其最小化2009-03-20 891

全部0条评论

快来发表一下你的评论吧 !