PCB原理图的常见错误分析

EDA/IC设计

描述

1.PCB原理图常见错误:

(1)ERC报告管脚没有接入信号:

a. 创建封装时给管脚定义了I/O属性;

b.创建元件或放置元件时修改了不一致的grid属性,管脚与线没有连上;

c. 创建元件时pin方向反向,必须非pin name端连线。

(2)元件跑到图纸界外:没有在元件库图表纸中心创建元件。

(3)创建的工程文件网络表只能部分调入pcb:生成netlist时没有选择为global。

(4)当使用自己创建的多部分组成的元件时,千万不要使用annotate.

2.PCB中常见错误:

(1)网络载入时报告NODE没有找到:

a. 原理图中的元件使用了pcb库中没有的封装;

b. 原理图中的元件使用了pcb库中名称不一致的封装;

c. 原理图中的元件使用了pcb库中pin number不一致的封装。如三极管:sch中pinnumber 为e,b,c, 而pcb中为1,2,3。

(2)打印时总是不能打印到一页纸上:

a. 创建pcb库时没有在原点;

b. 多次移动和旋转了元件,pcb板界外有隐藏的字符。选择显示所有隐藏的字符, 缩小pcb, 然后移动字符到边界内。

(3)DRC报告网络被分成几个部分:

表示这个网络没有连通,看报告文件,使用选择CONNECTEDCOPPER查找。

另外提醒朋友尽量使用WIN2000, 减少蓝屏的机会;多几次导出文件,做成新的DDB文件,减少文件尺寸和PROTEL僵死的机会。如果作较复杂得设计,尽量不要使用自动布线。

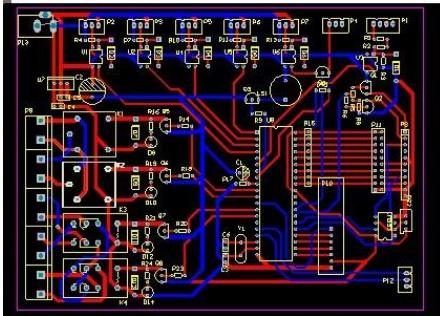

在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。PCB布线有单面布线、 双面布线及多层布线。

布线的方式也有两种:自动布线及交互式布线,在自动布线之前, 可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行, 以免产生反射干扰。

必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。

-

盘点PCB设计中的常见错误2024-01-12 2222

-

浅谈原理图和PCB图的常见错误2012-08-12 12855

-

原理图和PCB常见错误2013-12-25 8051

-

PADS 原理图PCB常见错误及DRC报告网络问题2016-01-11 8678

-

电路原理图及PCB布线常见错误有哪些?2021-03-18 2322

-

PCB原理图常见的错误有哪些2021-09-09 1454

-

PCB设计原理图常见错误2021-11-11 3625

-

PROTEL原理图常见错误2010-03-15 1738

-

简要分析PCB中常见错误2018-11-18 4346

-

PCB作业中常见14大错误2019-03-12 4567

-

PCB原理图设计时的常见错误有哪些2019-09-11 3403

-

电路原理图及PCB布线常见错误资料下载2021-04-05 1380

-

PCB设计工作中常见的错误有哪些?2024-02-21 1221

-

pcb板设计中的常见错误2024-11-04 1463

-

原理图和PCB设计中的常见错误2025-05-15 989

全部0条评论

快来发表一下你的评论吧 !