一种高速ADC接口电路设计方案

电子说

描述

摘要: 针对E2V公司的高速ADC 芯片EV10AQ190,提出了一种高速ADC 接口电路设计方案。首先简要介绍了高速ADC芯片EV10AQ190 技术特点,然后重点叙述了影响高速ADC接口电路性能的两大关键技术: FPGA 片同步技术和多路ADC 校正技术,最后给出了硬件调试及实验结果。实验结果表明,该高速ADC 接口电路采样率可稳定工作在4GHz 以上。这种方案已成功应用到某宽带雷达回波模拟系统的设计中。

随着电子通信行业的高速发展,越来越多的应用都要求更高的速率和更大的带宽,高速模数转换( ADC) 芯片的采样率已经从以前的MHz 级发展到当前的GHz 级。伴随着信号采样率的不断提高,信号偏斜( SKEW) 、抖动和噪声都在吞噬着时序余量,如何在高速系统中进行稳定、可靠的采样和数据变换将面临极大的挑战。

高速ADC电路设计一直是电子通信领域的研究热点。

文献[1]给出了一种基于FPGA 片同步技术的高速ADC 接口电路设计方法。

文献[5]利用E2V 公司ADC 芯片EV8AQ160 实现了双通道2.5Gsample /s 信号的采集。

文献[6]介绍了利用FPGA通过SPI 协议对ADC 芯片ADC083000 进行配置的方法,实现了3 Gsample /s 数据采样。

文献[7 - 8]讲述了如何利用FPGA 来设计多通道高速ADC 采样控制器。

文献[9 - 10]分别介绍了高速ADC 电路的设计方法和PCB 设计要点。

公司ADC 芯片EV10AQ190 实现了一种高速ADC接口电路,信号采样率高达4 Gsample /s。EV10AQ190 是E2V 公司的一款高速ADC 芯片,具有10bit 分辨率,最高采样率可达5GHz。在如此高速的ADC 接口设计中,时钟和数据稳定的相位关系、同步性能的好坏将直接影响信号采集的质量,必须采用源同步技术,保证采样时钟和数据严格同步、时序关系稳定。此外,对于高速ADC 芯片EV10AQ190,内部集成了多路ADC,通过采用多通道ADC交错采样拼接技术来获得更高采集变换速率。因此,多个通道ADC 输出幅度、相位、直流偏置是否一致将直接影响采样拼接后的高速ADC 输出信号质量,高速ADC 接口电路设计时必须对EV10AQ190 芯片内部4 路ADC进行幅相一致性校正。

本文提出了一种基于片同步( CHIPSYNC) 技术的高速ADC 接口电路设计方案,利用XILINX 公司Virtex - 6 系列FPGA 完成了高速ADC 接口设计,实现了采样时钟和数据的动态相位调整,确保了高速ADC 的稳定、可靠工作。同时,采用了多路校正技

术对芯片EV10AQ190 内部4 路ADC 的偏置( Offset)、增益( Gain) 、相位( Phase) 进行校正,保证多通道ADC 输出的幅相一致性,确保高速ADC 的动态性能指标满足设计要求。

1 高速ADC 器件EV10AQ190EV10AQ190 是E2V 公司的一款低功耗、高性能模数转换芯片,片内集成了4 路1. 25 GHz 采样率、10bit 分辨率ADC,输出为LVDS 标准电平,可以工作在单通道、双通道、四通道3 种模式,最高采样率可达5GHz。EV10AQ190 内部集成了1∶ 1 和1∶ 2 的数据多路分离器( DMUX) 和LVDS 输出缓冲器,可以降低输出数据率,方便与多种类型的高速FPGA 直接相连,实现高速率的数据存储和处理。为了补偿由于器件参数离散和传输路径差异所造成的采样数据误差,该ADC 具有针对每路ADC 数据的增益、偏置、相位的控制和校正。EV10AQ190 提供测试和自检功能,方便用户根据自己的习惯对ADC 是否正常工作进行测试和对时序是否对齐进行调试。

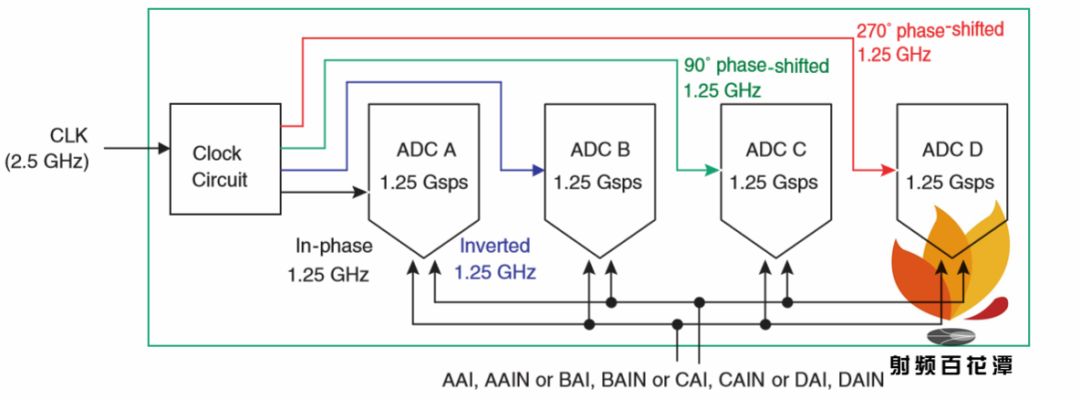

EV10AQ190 可以工作在3 种模式下,分别是采样率为1.25 GHz 的四通道模式,采样率为2. 5 GHz的双通道模式以及采样率为5 GHz 的单通道模式。EV10AQ190 的所有控制参数,包括通道选择、旁路模式、编码格式、输出多路分离器、积分非线性校正、偏置校正、增益校正、相位校正等,均可通过SPI 串行控制端口对相应的控制寄存器进行设置。本文中,EV10AQ190 配置工作在单通道模式,如图1 所示。

图1 单通道模式时钟驱动( 模拟信号由AAI /AAIN 输入)

外部模拟信号通过一个射频转换器将单端信号转换成差分信号,可选择A、B、C、D 任一通道输入,输入信号在内部同其他3 路ADC 连通,且4 路ADC时钟均由同一外部时钟驱动,即4 路ADC 共用时钟电路。在单通道模式下,外部输入2. 5 GHz 时钟,该时钟会被2 分频为1. 25 GHz,以驱动内部采样时钟。同相的1. 25 GHz 时钟驱动A 路ADC,同时反相的1. 25 GHz 时钟驱动B 路ADC,同相的1. 25GHz 时钟经过90°延时后驱动C 路ADC,反相的1.25 GHz 时钟经过90°延时后驱动D 路ADC,在此交错拼接模式下将得到最高5GHz 的等效采样率。

2 高速ADC 接口设计中的关键技术2. 1 基于片同步技术的高速ADC 接口片同步( CHIPSYNC) 是XILINX 公司命名的一种同步技术,其本质是一种源同步技术,目的是为FPGA 提供一个高速的源同步数据总线接口。它是XILINX 公司在Virtex - 4 及之后系列FPGA 上采用的一种技术,XILINX FPGA 内部具有若干全局时钟缓冲器( BUFG) 和区域时钟缓冲器( BUFR) ,特别适合做源同步接口。FPGA 片内每个I /O 管脚中集成了一个64 阶的可编程调节信号延迟的延时模块( IODELAY) ,可精确控制信号延时实现采样时钟和数据相位的动态调整,从而确定信号采集的最佳采样点,实现高速ADC 接口的可靠、稳定工作。

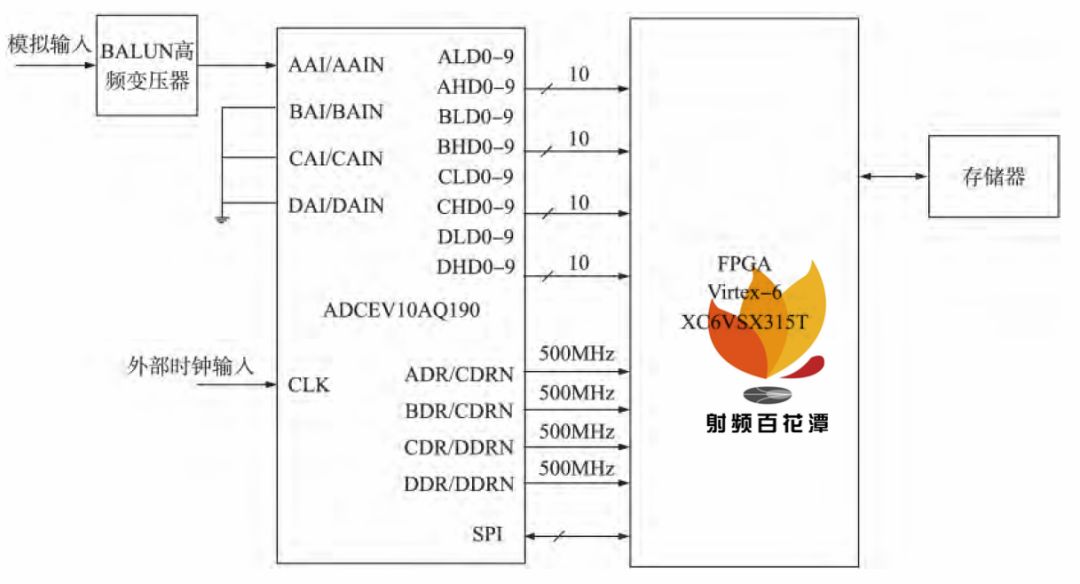

图2 4. 0GHz 采样高速ADC 接口电路原理框图

图2 为基于片同步技术的4GHz 采样高速ADC接口电路原理框图,主要包括高速ADC 和高性能FPGA 接口处理2 部分。

模拟输入信号经过巴伦( BALUN) 变压器完成单端信号到差分信号的转换,然后输入到高速ADC芯片EV10AQ190 的模拟输入端。利用XILINX 公司高性能Virtex - 6 系列FPGA 芯片XC6VSX315T中的40 对LVDS 管脚接收来自EV10AQ190 的4 路10 bit 1 000 Mbit /s 的输出数据,并用4 个LVDS 专用时钟输入通道接收4 路ADC 输出的500MHz 同步采样时钟( DDR 输出,采样时钟为数据速率的一半) 。FPGA 接收到的4 路1 000 Mbit /s 高速数据后,经过内部1: 4 串并转换模块( ISERDES) 后,变成16 路并行10 bit 数据,速度降为250 Mbit /s,便于FPGA 内部处理并和低速的外部存储器相连。

2. 1. 1 高速ADC

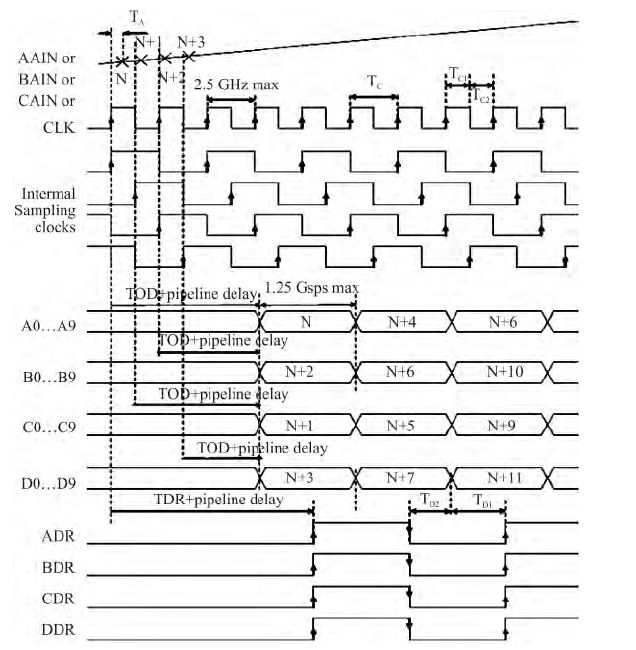

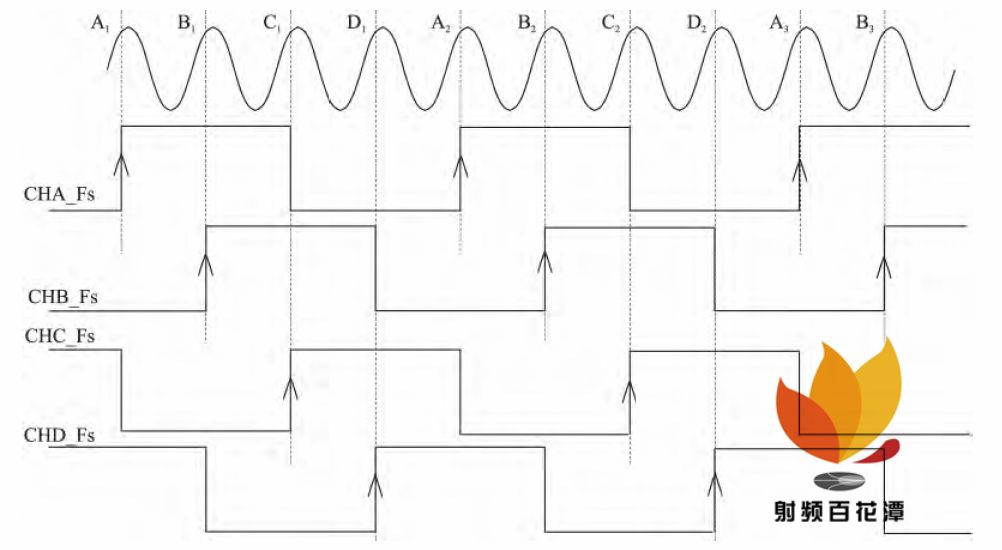

EV10AQ190 工作在单通道模式下,模拟信号从ADC 的A 通道输入,且DMUX = 1: 1 输出模式,此时ADC 工作时序如图3 所示。

图3 EV10AQ190 单通道模式1: 1 DMUX 模式的工作时序

图3 中,芯片A 端口上的模拟输入将会在AHD0~ AHD9、BHD0 ~ BHD9、CHD0 ~ CHD9 和DHD0 ~DHD9 上以交错方式输出。本文中,信号采样率为4GHz,输入芯片时钟频率为2 GHz,内部4 路ADC 采样时钟为输入时钟频率的一半,即内部4 路ADC 以1GHz 进行采样。ADC 变换数据以DDR 方式输出,输出1 000 Mbit /s 速率数据的同时输出500 MHz 同步采样时钟,输出数据位宽为4 ×10 =40 对LVDS 信号。

2. 1. 2 ADC 与FPGA 数据接口本文采用了XILINX 公司Virtex - 6 系列FPGA( XC6VSX315T) 来实现高速ADC 接口。ADC 芯片EV10AQ190 输出的数据和同步时钟送到FPGA 芯片XC6VSX315T 中,Virtex -6 系列FPGA 具有多个专用LVDS 差分逻辑接收通道,发送数据速率高达1. 25Gbit /s,接收数据速率也高达1 Gbit /s,能够满足EV10AQ190 输出数据和控制逻辑的要求。Virtex - 6系列FPGA 的每个I /O 管脚都采用了CHIPSYNC 技术[3],在其I /O 管脚中嵌入了一个64 阶的可编程调节信号延迟的延时模块IODELAY,对于200 MHz 延时时钟( 周期为5 ns) 输入,可调节的最小延时为5 ns/64 =78. 15 ps。这样,可以精确地独立调整每根数据线的延迟,甚至可以通过设置一些控制信号在程序运行过程中改变信号的延迟,使锁存时钟可以精确地对准每根数据线数据有效窗口的中心,保证高速数据采集时整个数据总线的所有数据能够可靠地锁存。

FPGA 内部数据和时钟接收处理框图如图4 所示,ADC 数据和ADC 时钟信号通过专用差分数据接口IBUFDS 和IBUFGDS 进入FPGA 内部,经精确延时模块IODELAY 进行相位动态调整,再经过输入串并变换模块ISERDES 作1: 4 串并转换,完成高速ADC 数据的接收。

图4 FPGA 内部数据和时钟接收框图

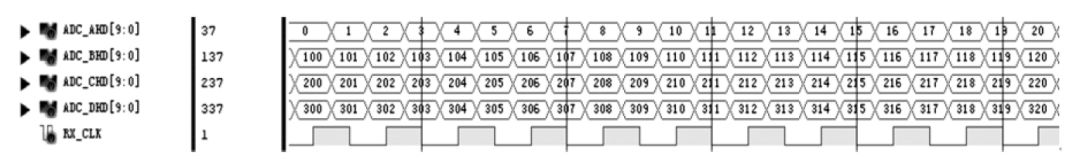

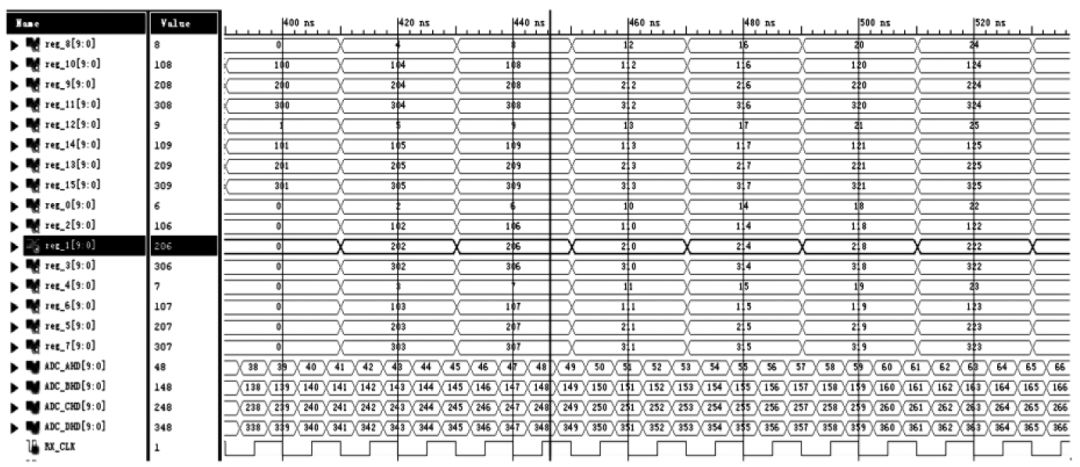

FPGA 内部数据和时钟接收功能采用VERILOG语言编程,设计中利用XILINX 仿真软件ISim 对该程序进行了功能仿真。定义输入的仿真激励信号为4 路10 bit 数据和时钟,分别命名为ADC_AHD[9:0]、ADC_BHD[9: 0]、ADC_CHD[9: 0]、ADC_DHD[9: 0]和RX_CLK,用来模拟ADC 芯片EV10AQ190输出的4 路DDR 方式的采样数据和时钟。其中,ADC_AHD 为0 ~ 99 循环计数,ADC_BHD 为100 ~199 循环计数,ADC_CHD 为200 ~ 299 循环计数,ADC_DHD 为300 ~ 399 循环计数,如图5 所示。

图5 FPGA 内部时序仿真激励信号

FPGA 内部时序仿真结果如图6 所示。图6 中, reg0 ~ 15[9: 0]为FPGA 输出的经过1: 4串并转换( ISERDES) 后的16 路10 bit 数据。从图中可以看出,来自ADC 芯片的4 路高速串行数据变为16 路较低速的并行数据,信号速率降为原来的1 /4,并且输出数据相对输入数据具有十多个时钟周期的延时,时序严格同步,验证FPGA 内部数据和时钟接收处理程序的正确性。

图6 FPGA 内部时序仿真结果

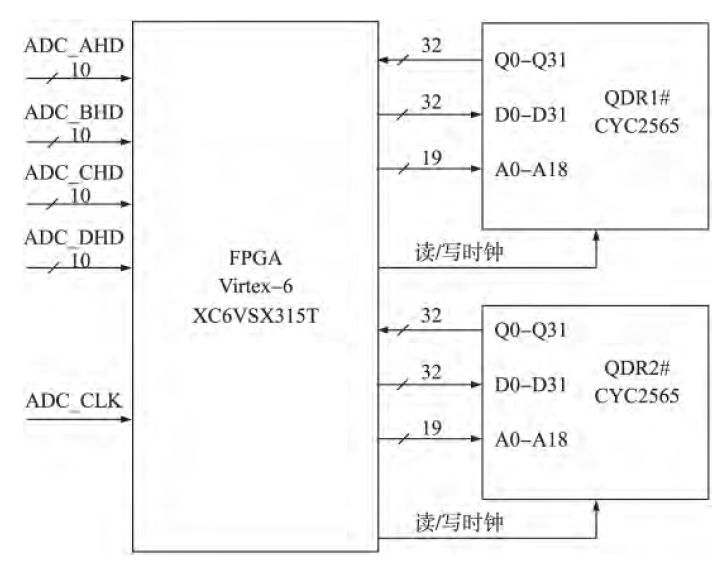

2. 2 QDR 存储电路设计高速ADC 采集变换输出数据经过FPGA 进行串并转换降速处理、存储器接口控制后可外接DDR( 双倍数据速率) 或QDR( 四倍数据速率) 存储器中进行缓存,本文高速ADC 接口电路用于宽带雷达回波模拟系统,FPGA 外接存储器为QDR SRAM 存储器,用来实现对雷达发射信号的存储转发。

本文使用了CYPRESS 公司的2 片QDR SRAM存储器CY7C2565KV18,FPGA 和QDR 存储器之间的接口电路如图7 所示。

图7 QDR 存储器接口电路原理框图

ADC 芯片EV10AQ190 输出的4 路10 bit 高速数据经过FPGA 进行1: 4 串并变换后变为16 路10bit 数据,速率降为原来的1 /4,便于和低速的QDR存储器接口。再经过FPGA 内部QDR 读写控制器( XILINX FPGA 内部专用的IP Core) 后送到2 片QDR 存储器CY7C2565KV18 中进行暂存。

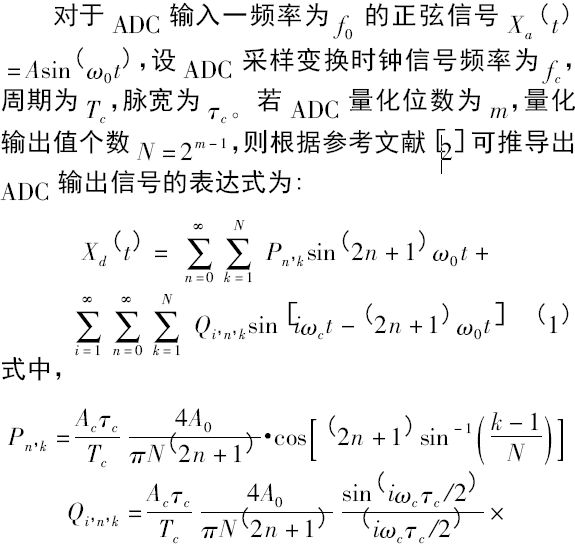

2. 3 多路ADC 校正技术2. 3. 1 ADC 输出信号的杂散电平[2, 11]

从式( 1) 可以看出,ADC 输出信号频率成分包括2 部分: 有用信号ω0和ω0的各次谐波分量( 式( 1) 中的第一项) 以及有用信号与采样时钟信号间的各次交调分量( 式( 1) 中的第2 项) 。有用信号( ω0) 的谐波分量可通过ADC 之后的低通滤波器滤除,而有用信号和采样时钟间的某些交调分量,如ωc - ω0、ω0 - ωc、2ωc - ω0频率成分,会落在低通滤波器通带内,无法滤除,影响ADC 输出信号无杂散动态范围( SFDR) 。因此,要提高ADC 动态性能,必须尽量减小有用信号和采样时钟间的交调分量。

2. 3. 2 EV10AQ190 中多路ADC 校正方法

EV10AQ190 芯片内部包含4 个1. 25 GHz 采样率的ADC,通过交错采样拼接技术实现单通道最高5 GHz 采样率。因此,要保证单通道模式下ADC 输出信号质量,减小ADC 输出信号杂散电平,必须确保内部4 路ADC 的幅度相同,相位上严格相差90°,即需要对EV10AQ190 芯片内部4 路ADC 的直流偏置、增益、相位参数值进行校正,可通过内部SPI 串行控制端口对相应的控制寄存器进行设置来完成。

EV10AQ190 芯片工作在单通道模式下,若输入芯片时钟为fc,则内部4 路ADC 采样率为fc /2,等效采样率为2fc。输入信号频率为fin。根据2. 3. 1 分析结果,影响ADC 输出信号SFDR 性能的是有用信号和采样时钟间的某些交调分量,如fc - fin、fc /2 -fin和fin - fc /2 等均有可能落在低通滤波器通带内,必须尽量抑制。通过幅相一致性校正技术可有效减小这些交调分量的大小。

EV10AQ190 芯片内部多路ADC 校正应注意两点:一是校正顺序是先校偏置,再校增益,最后校相位; 二是校正时选择输入模拟信号频率应选ADC 最大频率点。对于5 GHz 采样,每路ADC 采样率为1. 25 GHz,故可选择输入校正信号频率点为600. 59 MHz。

( 1) 偏置校正( Offset Calibration)多通道ADC 直流偏置不同将会影响输出信号杂散分量中fc /2 频率信号电平大小,从而影响高速ADC 的动态性能。由于ADC 的偏置对增益和相位都有影响,因此首先应对偏置进行校正。EV10AQ190 输出为10 bit无符号数,最大输出值是1 023,故直流偏置理论上应该为511。偏置的校正方法如下: ADC 无信号输入的情况下,记录ADC 输出数据,计算4 个通道ADC 输出数据的平均值,看平均值是否是511,如果是511 说明偏置已经校好,如果不是,则通过SPI 串口控制EV10AQ190 的偏置控制寄存器来调整ADC偏置,调整完成,记录并设置好4 个通道偏置控制寄存器的值。

( 2) 增益校正( Gain Calibration)多通道ADC 增益不同将会影响输出信号杂散分量中fc - fin,fc /2 - fin和fin - fc /2 频率信号电平大小,即影响输入信号的镜像频率成分,从而影响ADC 的动态性能。对增益的校正需要保证偏置已经校正完成。增益的校正方法如下: ADC 输入一个正弦信号,推荐频率为600. 59 MHz,幅度为500 mV,记录下4 个通道的采集数据并做FFT 变换,比较4 个通道采集数据频谱的幅度是否相同。如果不同,以一个通道为标准,通过控制EV10AQ190 的增益控制寄存器调整其他3 个通道的增益,调整完成,记录并设置好增益控制寄存器的值。增益校正过程要求输入正弦信号和采样时钟信号要严格同源。( 3) 相位校正( Phase Calibration)多通道ADC 相位不校准会影响输出信号杂散分量中fc - fin,fc /2 - fin和fin - fc /2 频率信号电平大小,即影响输入信号的镜像频率成分,从而影响ADC 的动态性能。

相位校正前应保证偏置和增益校正已完成。相位校正过程要求EV10AQ190 输入模拟信号频率是输入时钟的2 倍,是内部4 通道ADC 采样率的4倍。对于EV10AQ190 工作在单通道5 GHz 采样模式下,输入时钟频率为2. 5 GHz,内部每路ADC 采样率为1. 25 GHz,则将ADC 的输入模拟信号频率设置为5 GHz。如果EV10AQ190 内部4 路ADC 相位严格相差90°,由于输入信号频率是内部ADC采样时钟频率的4 倍,则4 个通道采集变换输出信号幅度相等,4 路ADC 输出将在一条直线上,如图8所示。因此,相位校正时可以通过设置EV10AQ190的相位控制寄存器来调整A、B、C、D 4 个通道采样时钟的相位,使得4 路输出信号值( Ai、Bi、Ci、Di,i= 1,2

,3,…) 尽量相等。

图8 ADC 相位校正原理

相位校正方法如下: ADC 输入一正弦信号,频率是输入采样时钟的2 倍。记录4 个通道ADC 输出数据,如果4 路ADC 输出数据相同,说明相位校正完成。如果不同,则以一个通道为基准,通过控制EV10AQ190 的相位控制寄存器调整其他3 个通道的相位,使得4 个通道ADC 输出值相同。相位校正过程要求输入正弦信号和采样时钟信号要严格同源。

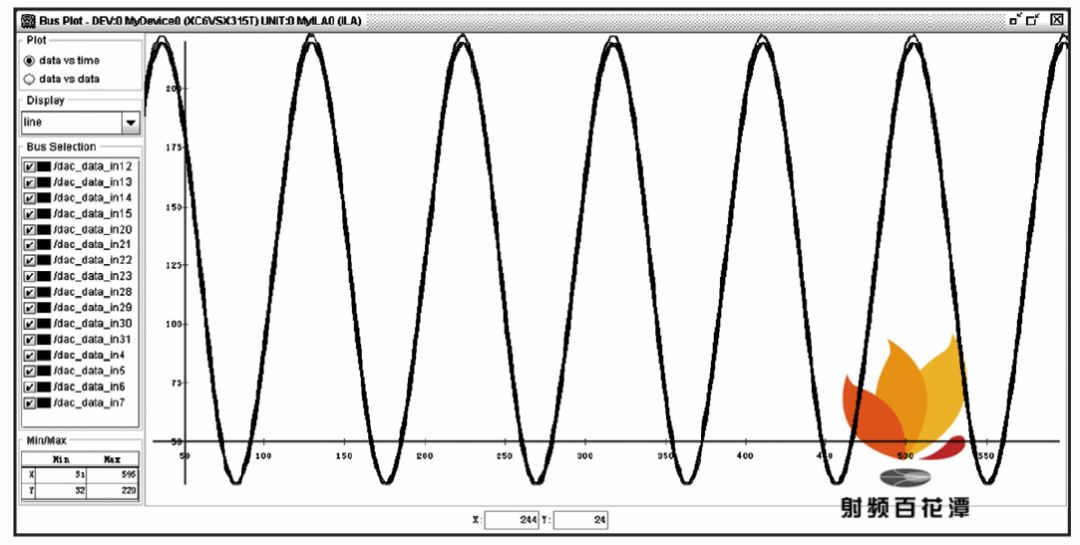

3 实验与结果高速ADC 接口程序在XILINX 公司的ISE 软件中经过逻辑综合、布局布线、目标代码生成等过程,最终用高性能FPGA 芯片XC6VSX315T 实现,并下载到高速ADC 接口电路板上的FPGA 进行了实验验证。实验过程设计如下: 首先由信号源产生一点频信号,频率为500 MHz,输入采样时钟为2 GHz,高速ADC 采样率为4 GHz。500 MHz 点频信号经过高速ADC 芯片后变为4 路并行的数字信号,数据速率为1 000 Mbit /s,进入FPGA 芯片。然后在XILINX 公司ChipScope Analyzer 软件中采集观测高速ADC 信号经过1: 4 串并变换后的数据,得到了16 路10bit 稳定的数据,并用总线( bus) 波形图方式显示,如图9 所示:

图9 FPGA 内部采集的ADC 输出信号

图9 表明,用频率为4 GHz 的采样时钟对频率为500 MHz 的正弦信号进行采样所得到的高速数据经过本文设计的高速ADC接口电路处理后得到了完美的正弦信号数据,从而证明了高速ADC 接口电路的正确性和有效性。

另外,为测试多路校正技术对高速ADC 接口电路性能影响效果,本文对校正前和校正后ADC 输出信号的无杂散动态范围( SFDR) 进行了测试。测试结果为: 幅相一致性校正前输出信号SFDR 为35dBc,校正后输出信号SFDR 能够达到42 dBc,提高

了约7 dBc。可见,多路校正技术对于改善高速ADC 动态性能是十分明显的。

4 结论

本文针对E2V 公司的高速ADC 芯片EV10AQ190,介绍了一种高速ADC 接口电路设计方案。通过采用FPGA 片同步技术和多路ADC 校正技术,解决了高速电路中数据与时钟的时序同步以及多通道ADC 幅相一致性校正问题,确保了高速ADC 的动态性能和可靠性。文章最后给出了硬件调试结果。

实验结果表明,通过校正EV10AQ190 芯片内部4 路ADC 的偏置、增益、相位并采用FPGA 片同步技术,该高速ADC 接口电路采样率可达4 GHz 以上,杂散优于42 dBc,高速ADC 输出数据能够稳定、可靠的锁存到FPGA 内部。该接口电路方案已成功应用到某宽带雷达回波模拟系统高速信号采集的设计中。

-

基于PC机USB接口充电电路设计方案2023-11-15 515

-

一种推挽逆变车载开关电源电路设计方案2023-11-14 377

-

高速ADC电源设计方案2023-11-10 352

-

分享一种基于IR2llO芯片的高频感应加热电源驱动电路设计方案2021-07-26 2121

-

CAN总线接口EMC标准电路设计方案2021-07-12 3548

-

分享一种智能卡接口的设计方案2021-05-27 1942

-

介绍一种包含千兆采样率ADC的系统设计方案2021-05-14 1291

-

求一种低成本高速USB接口的设计方案2021-05-10 1937

-

求一种采用数字控制的三相移相触发电路设计方案?2021-04-08 1747

-

485接口EMC电路设计方案2020-02-05 7266

-

基于FPGA技术的RS232接口时序电路设计方案2017-01-26 1248

-

一种低功耗以太网接口电路的设计方案2014-01-14 14480

-

一种新的低功耗CMOS三值电路设计2010-04-27 526

全部0条评论

快来发表一下你的评论吧 !