三维图像处理系统组成及实现方案

可编程逻辑

描述

三维图像信息处理一直是图像视频处理领域的热点和难点,目前国内外成熟的三维信息处理系统不多,已有的系统主要依赖高性能通用PC完成图像采集、预处理、重建、构型等囊括底层和高层的处理工作。三维图像处理数据量特别大、运算复杂,单纯依靠通用PC很难达到实时性要求,不能满足现行高速三维图像处理应用。

本系统中,采用FPGA实现底层的信号预处理算法,其处理数据量很大,处理速度高,但算法结构相对比较简单,可同时兼顾速度和灵活性。高层处理算法数据量较少、算法结构复杂,可采用运算速度快、寻址方式灵活、通信机制强大的DSP实现[1,4]。

1 三维图像处理系统组成

1.1 硬件系统构成

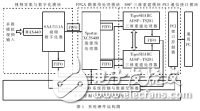

该系统由五个模块组成,如图1所示。

系统信息处理流程见图2所示。CCD摄像机采集的多路模拟视频信号经MAX440按需要选定后,送入模数视频转换器SAA7111A将摄像机输出的模拟全电视信号CVBS转换成数字视频信号;之后视频信号流入图像预处理器Spartan XC3S400,经过提取中心颜色线、提取激光标志线和物体轮廓线的预处理后,配送到两片TS201进行定标参数计算、坐标计算、三维重建、数据融合以及三维构型的核心运算;最后将DXF文件数据经由PCI接口传送到PC,完成三维图像变换和显示等最终处理;整个系统的逻辑连接和控制以及部分数据交换由另一片FPGA来完成[1]。

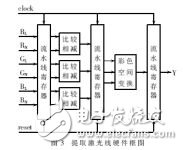

在体系结构设计上,FPGA处理器采用SIMD结构,在一个控制单元产生的控制信号下,数据通路中的三个算法并行运行。由于该系统要求处理速度较高,因而在数据通路中采用了流水线技术以提高速度。此外,本系统中为图像存储采用了许多大容量高速FIFO,以达到减少地址线,简化控制的目的。

1.2 处理器芯片

为满足系统大数据量快速处理的要求,三款核心芯片均为最新高性能产品,其硬件方面的特点给系统设计带来极大的方便,其优异的运算性能可确保系统的快速实时性。

FPGA芯片采用Xilinx公司近期推出的采用90nm工艺的Spartan3系列的XC3S400,该系列芯片是目前为止工艺最先进、价格较低、单位成本内I/O管脚最多的平台级可编程逻辑器件。XC3S400芯片内部时钟频率可达326MHz,信号摆幅1.14V和3.45V,I/O口支持622Mbps的数据传输率,具有高性能SelectRAM内部存储器,多达4个数字时钟管理器模块和8个全局时钟多路复用缓冲器。

DSP采用ADI公司的最新款基于并行处理设计、具有海量片内RAM的TigerSHARC ADSP TS201。其内部集成的RAM容量高达24Mbit,核心速度最高达600MHz。内设双运算模块,每个包含一个ALU、MUL、64bit移位寄存器、32个32bit寄存器组和一个128bit通信逻辑单元,相关的数据对齐缓冲器;双整数ALU,各有独立的寄存器组,提供数据寻址和指针操作;4个128bit宽度内部总线,每个都连接到6个4Mbit的内部存储器块;提供与主机处理器、多处理器空间、片外存储器映射外设、外部SRAM和SDRAM相连的外部端口;14通道DMA控制器;4个全双工低电压差分信号输入的Link Port;具有片内仲裁总线,用于多DSP无缝的连接。

数字化器采用了Philips公司的增强视频输入处理器(EVIP)——SAA7111A模数转换器。该产品广泛应用于个人视频、多媒体、数字电视、可视电话、图像处理、实时监控等领域,纯3.3V CMOS工艺的模拟视频前端和数字视频编码器,能够将PAL/TSC/ECAM视频信号解码为与CCIR-601相兼容的多种数字视频格式,支持TV或VTR信号源的CVBS或S-Video视频信号,最高图像分辨率可达720×576,支持24位真彩色,可以通过串行总线动态配置SAA7111A模数转换器的工作方式和各种参数。

2 模块设计

2.1 视频采集与数字化模块

由于模拟摄像机采集的是PAL制的复合视频信号(CVBS),所以必须先将其数字化才能开始后继数字视频处理。视频采集与数字化模块主要包括一片视频多路复用器MAX440、一片SAA7111A、一片I2C接口控制器PCF8584和一些连接逻辑。MAX440用来快速切换来自不同模拟输入端的模拟视频流,SAA7111A模数转换器是该模块的核心,它采集模拟视频,将其数字化为720×576的RGB(8,8,8)真彩色信号格式的数字视频,其输出的RGB真彩色信号为16位,其中高字节和低字节数据周期分别为74ns和37ns,即低字节的频率是高字节的1倍。这样就要利用触发器和两个分别为13.5MHz和27MHz的时钟信号,将输入数据格式转换为24位、周期均为74ns的RGB真彩色信号,此外,它还为整个硬件系统提供必要的时钟和同步信号;PCI接口控制器通过PCF8584来配置和控制SAA7111A,连接逻辑由FPGA实现。

2.2 FPGA图像预处理模块

预处理从巨大的视频信息中提取极少量的对三维重建有用的信息传送至DSP后处理。该模块包括主处理FPGA芯片和高速FIFO,负责实时采集视频信号并对采集到的无压缩的视频信息进行预处理,包括提取激光中心线、提取轮廓线、提取中心颜色线三个部分。

为了提高视频采集的整体性能,更重要的是为预处理提供相邻的有激光帧和无激光帧,必须通过视频帧缓存首先暂存无激光帧。缓存由3片AverLogic公司的AL422B及一些由FPGA实现的连接逻辑组成;当前端模块输出无激光帧时,SA7111A控制3片AL422B写操作,将其存入FIFO;当前端输出有激光帧时,后端的视频处理模块控制3片AL422B进行读操作,读出暂存在其中的无激光帧数据。预处理FPGA将读取的无激光帧和有激光帧进行相减运算。输出同样采用3组缓存分别用来暂存激光样条数据、目标轮廓线数据和图像中心线数据;所有模块均采用同步时钟控制,同步时钟采用由SAA7111A模数转换器产生的LLC2信号。为了提高系统速度,算法复杂、耗时较长的计算过程进行了流水线处理。

2.3 DSP三维重建模块

为了应对三维图像大数据量复杂高速运算的需要,这里采用了两片TigerSHARC 201芯片并行三维重建运算。由控制FPGA对两片DSP所要处理的图像进行任务分配,DSP结合预处理FPGA存入FIFO的数据和PCI总线所给处理参数进行定标参数计算、坐标计算、三维重建和构型。由于TS201内部集成的总线仲裁机制,双DSP可以实现无缝连接,大大减小了多DSP协调工作的设计难度。DSP间的连接是依靠其拥有的全双工LinkPort,它采用LVDS(低电平差分信号)输入数据。链路口能独立或同时工作,在时钟的上升沿和下降沿锁存数据。链路时钟频率最高可以与处理器核相同,高达500MHz,每个链路能完成500Mbps的单向数据传输。每个DSP的4个LinkPort合起来最大的通透率为4.0Gbps。连线短且简单,不需要额外的辅助电路,且可有效防止连线长引起的信号畸变。LinkPort传输协议由控制FPGA完成。

2.4 PCI通信接口模块

根据三维信息获取系统的速度传输要求,采用PCI接口完成该系统与通用PC的信息交互。PCI接口控制器是硬件部分的控制中心和数据交换中心,它接收设备驱动程序的命令和数据,配置和控制系统的各个模块使其协调工作,完成系统任务;它还负责将采集到和处理后的数据通过PCI总线转送给通用PC。本系统采用PLX公司的32bit/33MHz PCI9030作为接口芯片,串行EEPROM-FM93CS56L电可擦除只读存储器保存PCI9030的配置信息。

2.5 系统控制与数据交换模块

控制单元对处理器的数据处理单元和输入数据格式转换单元以及所有FIFO存储器产生控制,与预处理FPGA配合完成DSP的LinkPort协议。由于数据处理单元中为流水处理,在控制单元的设计中要特别注意由流水线产生的固定周期的延时,延时的周期数等于相应流水线的级数。控制单元还与PCI接口连接,接收来自主计算机的控制信号和背景阈值等信息。控制FPGA还是SAA7111A、PCI接口和DSP之间的图像和信息交换的桥梁,为其提供所需要的参数和数据信息。

3 软件设计与实现

3.1 图像预处理算法

如图3,激光带预处理算法的实现[2]为:由于有激光帧和无激光帧是依次交替产生的,因此首先要保存一帧有激光帧,在其下一帧,即无激光帧到来时,将保存的有激光帧和当前无激光帧的相同行、列的点相减,再对结果进行亮度提取,处理完成后的数据存入目标缓存。

如图4,实现提取轮廓线算法分为三个部分[3],首先由计算比较模块对输入像素点的值与预先计算好的阈值进行比较,判断其是否为目标像素;然后利用一个序列检测模块进行一维尺度滤波以去除某些噪声点;再经过一个边缘检测模块,提取出每行的第一个目标像素作为目标的左边缘点;完成后将此点所对应的列地址数据存入目标缓存。在某些情况下,可能整行都检测不到边缘点,这时将0存入目标缓存作为无边缘点的标识。

提取中心线算法实现比较简单,只需对目标缓存的写允许信号加以控制,使RGB数据只能在每行的中心点处写入目标缓存即可。

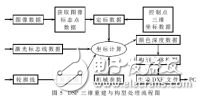

3.2 三维重建和构型

如图5所示,高速DSP将根据预处理信息得到的激光标志线、轮廓线和中心颜色线数据与源数字化图像结合起来进行三维重建。首先根据获取的图像标志点数据结合控制点三维坐标数据计算出系统定标数据;其次根据轮廓线计算物体外表面展开图,再依据定标数据结合展开图和机械参数对图像中的坐标点进行计算,给出数据集,输出深度数据文件;最后对多次扫描的数据进行融合,将离散点构型成立体模型(或立体彩色模型),将模型生成DXF、STL等数据文件传入PC机,使用后端处理软件进行显示[3]。

图像预处理算法设计使用Verilog HDL在Xilinx公司的ISE8.1集成编译环境下成功实现;FPGA开发流程不再赘述。

DSP三维重建算法已使用C语言在ADI公司Visual DSP++环境下成功实现[4]。算法实现步骤如下:①用C语言编程实现算法。②使用Visual DSP++编译器将源程序编译成目标文件。③根据产生的目标文件,分析结果及源程序结构并优化源代码。④应用TigerSHARC 201评估板进行运算时间评估。⑤重复上述步骤直至达到系统实时性要求,最后下载到目标板。

整个系统联机运行稳定,满足设计要求,实时性好。

实时三维图像信息处理以其数据量大、速度要求高、处理过程复杂的特点使其难以使用集成电路实现。本文研究的以目前最新高性能处理器的FPGA+DSP为核心架构的三维图像处理系统精心设计了算法的硬件实现,充分利用了两种处理器的长处。实验表明,该系统有着良好的性能,对实现基于网络的实时三维扫描应用,如三维传真、机械远程加工、快速成型和虚拟现实,有着重要的意义。

参考文献

[1] LEI HAIJUN,LI DEHUA.High-Speed aerial image processing system based on DSP,In neural nerwork and distributed processing,Proceedings of SPIE Vol.4555,2001:131-136

[2] 雷海军,李德华,王建永等.一种结构光条纹中心快速检测方法[J].华中科技大学学报,2003,31(1):74-76.

[3] 金 刚.三维扫描仪中三维信息获取理论与技术研究[D].华中科技大学博士学位论文,2002,(3)

[4] 陆海东,吴明赞.基于FPGA+DSP结构的小波图像处理系统设计[J],电子技术应用,2006,(3)93-95.

-

比较好的三维图像绘制的函数有哪些啊2011-09-30 7214

-

labview 三维图像显示不出来,求助~2014-04-08 4285

-

基于FPGA+DSP的三维图像信息处理系统设计2019-06-24 2255

-

如何设计三维图形加速系统?2019-10-18 2431

-

光线追踪如何实现实时三维图形?2021-02-26 2021

-

基于激光差频扫描的水下三维图像2009-12-14 1146

-

三维图像信息处理FPGA+DSP核心架构的设计与实现2009-01-09 1139

-

三维图像详解2009-08-03 3253

-

以FPGA+DSP为核心架构的实时三维图像信息处理系统设计2018-07-19 1993

-

三维图形引擎综述2017-12-11 1211

-

使用NI LabVIEW设计了三维图像设计2018-06-22 8307

-

点云的概念以及与三维图像的关系2021-08-17 8762

-

使用深度学习进行三维图像处理2021-11-05 4214

-

一文详解点云及三维图像处理技术2023-03-31 4656

-

20个MATLAB三维图像绘制的示例演示2023-07-07 4317

全部0条评论

快来发表一下你的评论吧 !