如何解决usb接口的电磁兼容问题

接口/总线/驱动

描述

usb接口具有传输速度快,支持热插拔以及连接多个设备的特点,目前已经在各类计算机、消费类产品中广泛应用。

一、 usb接口面临电磁兼容问题

由于usb接口其运行速率较高,容易通过usb连接线缆对外高频辐射超标,同时由于带电热插拔,容易受到瞬间电压冲击和静电干扰。因此我们在产品接口设计时,需要着重从接口滤波设计,防护设计,PCB设计、结构电缆多个方面考虑电磁兼容设计。

本文电磁兼容解决方案主要结合usb2.0接口电路特点,从产品原理图的接口电路出发,提供符合产品实际设计要求的具体的emc设计方案,从而使产品能够满足电磁兼容标准与规格要求,获得良好的emc品质,提升产品的可靠性。

二、 usb接口标准要求

带有usb接口的典型消费类产品,需要满足相关电磁兼容要求,与usb相关的电磁兼容项目要求如下,其他如应用在军品、汽车电子、铁路电子要求则有所不一样,具体请参考相关电磁兼容标准要求。

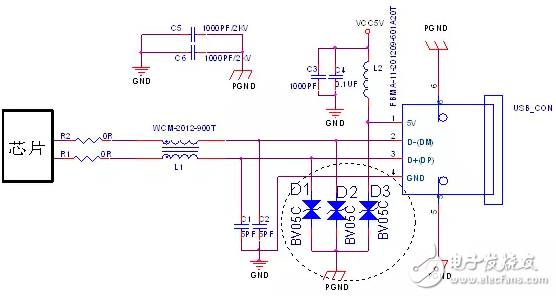

三、原理图emc设计:

四、原理图设计要点说明:

4.1滤波设计要点:

L1为共模滤波电感,用于滤除差分信号上的共模干扰;

L2为滤波磁珠,用于滤除为电源上的干扰;

C3、C4为电源滤波电容,滤除电源上的干扰;

C1、C2 为预留设计,注意电容尽量小,如实际影响信号传输,可以不焊接。

4.2防护设计要点:

D1、D2、D3组成usb接口防护电路,能快速泄放静电干扰,避免内部电路遭受静电的干扰。

C5、C6为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV以上。

4.3 特殊要求:

4.3 R1、R2为限流电阻,差分线之间耦合会影响信号线的外在阻抗,可以用此电阻实现终端最佳匹配,使用时根据实际情况进行调整。

4.4 器件选型要求:

L1为共模电感,共模电感阻抗选择范围为60Ω/100MHz~120Ω/100MHz,典型值选取90Ω/100MHz

L2选用磁珠,磁珠阻抗范围为100Ω/100MHz~1000Ω/100MHz,典型值选取600Ω/100MHz ;磁珠在选取时通流量应符合电路电流的要求,磁珠推荐使用电源用磁珠

C3、C4两个电容在取值时要相差100倍,典型值为1000pF、0.1uF;小电容用滤除电源上的高频干扰,大电容用于滤除电源线上的纹波干扰;

D1、D2、D3选用TVS,TVS反向关断电压为5V。TVS管的结电容对信号传输频率有一定的影响,usb2.0的TVS结电容小于5pF;

C5、C6为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV以上。

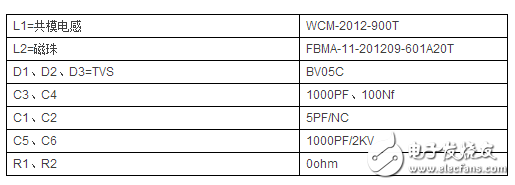

4.5 相关电磁兼容器件选型建议清单

五、PCB设计说明

5.1布局设计要点

元器件布局要按照信号流向进行布局;

防护器件要尽可能的靠近接口放置,确保引线电感最小,以保证防护器件能正常的进行防护动作。

应将芯片放置在离地层最近的信号层,并尽量靠近usb插座,缩短差分线走线距离。

5.2布线设计要点

共模电感下方不能走其它信号线。

如果usb接口芯片需串联端电阻或者D线接上拉电阻时.务必将这些电阻尽可能的靠近芯片放置。

将usb差分信号线布在离地层最近的信号层。

保持usb差分线下端地层完整性,如果分割差分线下端的地层,会造成差分线阻抗的不连续性,并会增加外部噪声对差分线的影响。

在usb差分线的布线过程中,应避免在差分线上放置过孔(via),过孔会造成差分线阻抗失配。

保证差分线的线间距在走线过程中的一致性,如果在走线过程中差分线的间距发生改变,会造成差分线阻抗的不连续性。

在绘制差分线的过程中,使用45°弯角或圆弧弯角来代替90°弯角,并尽量在差分线周围的150 mil范围内不要走其他的信号线,特别是边沿比较陡峭的数字信号线更加要注意其走线不能影响usb差分线。

-

【电磁兼容技术案例分享】伺服控制器产品电机抖动EMC自兼容问题案例2025-02-11 889

-

【电磁兼容技术案例分享】私服控制器产品电机抖动EMC自兼容问题案例2024-12-25 794

-

【电磁兼容技术案例分享】某氢燃料电池系统自兼容问题解决案例2024-10-19 713

-

USB接口电磁兼容(EMC)解决方案2022-02-11 1132

-

CAN总线通讯的电磁兼容问题有哪些?2021-06-03 2036

-

如何解决马达的电磁兼容问题2019-08-01 3178

-

根治电磁兼容问题 地偏移测试与整车系统接地设计2019-03-04 2727

-

马达的电磁兼容问题应如何解决?2018-07-19 3999

-

印制电路板的电磁兼容问题研究2016-07-29 896

-

物联网中的电磁兼容问题2016-03-21 573

-

电磁兼容问题解决方案 电磁屏蔽技术2010-08-03 1957

-

网络环境涉及的电磁兼容问题浅析pdf2009-10-13 3145

-

印制电路板的电磁兼容问题详解2009-03-26 4844

-

印制电路板的电磁兼容问题2009-03-24 665

全部0条评论

快来发表一下你的评论吧 !