关于设计FPGA系统中有源电容放电电路的方法和需要注意的问题

FPGA/ASIC技术

描述

电信设备,服务器和数据中心的最新FPGA具有多个电源轨,需要正确排序才能安全地为这些系统上下供电。高可靠性DC-DC稳压器和FPGA电源管理的设计人员需要一种简单的方法来安全地放电大容量电容器,以避免损坏系统。

FPGA电源排序

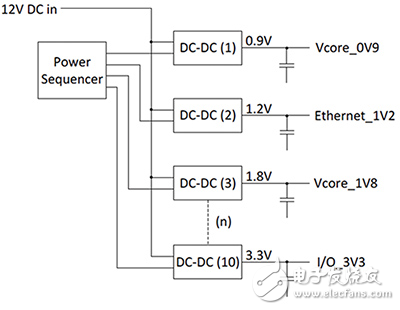

最新在生成片上系统FPGA的过程中,它们可以提供十个独立的电源轨,为Vcore,存储器总线电源,I/O控制器,以太网等提供电源。如图1所示,每个电源轨由DC供电。直流转换器可调节3.3 V,2.5 V,1.8 V,0.9 V等所需的电压。为了给系统加电,遵循特定的顺序以确保安全操作并避免损坏系统。同样在系统关闭期间,电源序列的顺序相反,确保在下一个电源轨关闭之前禁用每个电源轨。该指令通过电源序列发生器芯片控制,该芯片可启用每个DC-DC稳压器,如图1所示。

图1:典型FPGA系统电源轨每个服务的供电。

考虑存储在各种电源轨上的去耦电容中的电荷时会出现问题。例如,在0.9 V Vcore电源轨上,总去耦电容可以在10到20mF的数量级,并且存储在电容器组中的剩余电荷需要在断电期间主动放电,在下一次电源关闭之前序列被禁用。这样可以避免违反掉电序列并保护FPGA系统。因此,建议在每个DC-DC稳压器输出端使用有源放电电路。

有源电容放电开关

通过了解电容器组的大小,可以采用开放式方法对RC时间常数进行放电。一旦电压小于充电状态的95%(在3×RC时间常数下发生),则假设电容器放电。

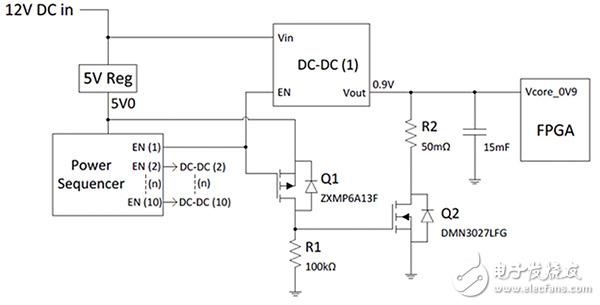

这样做的一个简单方法是通过一个具有已知接地电阻的开关,当需要放电时可以接通该开关。参考图1,电源序列发生器启用每个DC-DC稳压器的输出。然后可以使用该相同的使能(EN)信号来馈送并联连接到电容器组的开关。通过反转使能信号来驱动开关,当DC-DC稳压器的输出被禁止时,它将使电容器放电。对于开关,首选N沟道功率MOSFET,因为它很容易从以地为参考的逻辑信号驱动。所选电路如图2所示,Q2为N沟道功率MOSFET,Q1为P沟道MOSFET,反转电源序列发生器的EN逻辑信号。

图2:有源放电电路。

有源电容放电电路操作

参见图2 - 电源序列发生器的EN输出为DC-DC稳压器上的使能引脚供电以及电容器放电电路。当逻辑“0”发出关闭信号时,P沟道MOSFET(Q1)将信号反相,然后接通N沟道MOSFET(Q2)以对电容器组放电。

放电电路假设一旦关闭信号施加,DC-DC稳压器就无法继续产生输出。如果在关闭命令激活后,DC-DC稳压器的输出有电,则必须在放电电路激活之前引入延迟。这是为了确保放电MOSFET不会试图吸收DC-DC稳压器的全部输出电流能力。

为了从逻辑“0”信号增强N沟道功率MOSFET(Q2),P沟道MOSFET(Q1)将信号反相为5 V,以施加在Q2栅极源上。选择P沟道MOSFET(Q1)不具有低栅极阈值电压(VGS(th))。这是因为VGS(th)相对于温度下降并且Q1在逻辑“1”状态期间需要处于OFF状态以避免Q2的错误接通。需要选择适合5 V操作的最佳值以及Power Sequencer。

当电源序列发生器输出逻辑“1”时,DC-DC稳压器在ON状态下使能,Q2必须处于OFF状态。采用逻辑“1”输出,最小高电平输出电压为4.19 V(电源序列发生器的EN引脚输出规格),则在环境工作温度为60°C时,Q1 VGS(th)需要大于0.9 V 。此外,Q2的栅极需要通过100kΩ的R1电阻下拉至源极电位,以避免误导通。

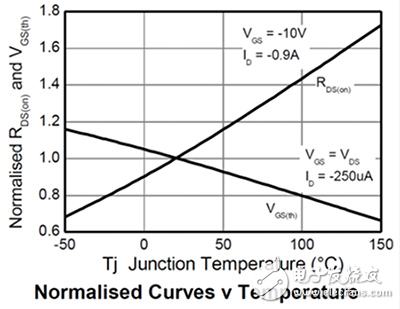

温度的VGS(th)变化在典型的电气曲线中找到。 MOSFET数据表。例如,图3中给出了来自Diodes Incorporated的ZXMP6A13F的归一化VGS(th)与温度的关系.ZXMP6A13F是首选器件,因为保证最小VGS(th)在室温下为1 V,在60℃时降至约0.9 V °C。

图3:ZXMP6A13F的温度标准化RDS(on)和VGS(th)曲线。

当电源序列发生器使能输出变为逻辑“0”时,则存在0.270 V的最大低电平输出,Q1需要保证通过该5 V - 0.270 V信号增强通道,以确保Q2导通并放电电容器组。因此,Q1需要在VGS = -4.5 V时具有导通状态。

为了对电容器组放电,选择N沟道功率MOSFET(Q2)具有导通电阻(RDS(开) ))适合于在10 ms内对最大电容组放电,以确保在不到100 ms的时间内完成10个通道的完全关闭顺序。必须提供辅助电源,以在关闭电源后至少100 ms驱动关闭电路(电源序列发生器)。

-

有源晶振需要加负载电容吗?2024-05-18 2543

-

使用电容降压时都需要注意哪些?2024-02-02 1676

-

FPGA的有源电容器放电电路注意事项2023-07-25 681

-

电容选型需要注意参数2023-01-03 4726

-

有源放电电路的原理和注意事项2022-04-21 7567

-

使用TDA2030音频功放电路有哪些事项需要注意?2021-07-28 6147

-

FPGA系统中有源电容放电电路设计需注意哪些问题资料下载2021-04-08 988

-

请问FPGA在电路设计上需要注意什么?2020-08-27 2100

-

FPGA系统有源电容放电电路怎么避免损坏系统?2019-10-23 1757

-

掌握这些有源电容放电电路设计要领,和“损坏系统”说拜拜!2019-06-09 8010

-

FPGA系统中有源电容放电电路设计需注意哪些问题2019-03-29 3318

-

FPGA的有源电容放电电路考虑2017-05-16 717

-

集成运放电路中有源负载放大电路的分析与计算方法2010-04-13 12006

全部0条评论

快来发表一下你的评论吧 !