高速设计的基本概念详细资料说明

电子说

描述

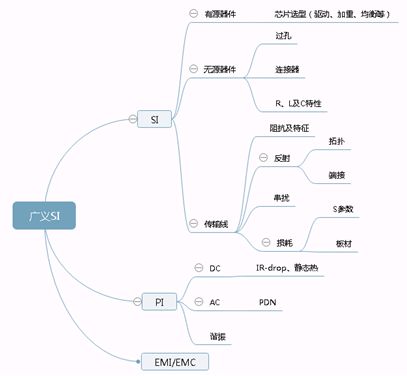

高速设计研究的范畴也是广义SI的研究对象,具体可以分为三个部分:信号完整性(Signal Integrity, SI)、电源完整性(Power Integrity, PI)以及电磁兼容性(Electro Magnetic Compatibility, EMC),如果应对不当,最终会导致的问题大致可以分为:单网络的噪声、多网络间的串扰、电源分配系统的压降、电磁干扰(Electro Magnetic Interference, EMI)以及时序问题。

01

对于初学者而言,高速设计的基本概念纷繁复杂,阻抗、反射、振铃、串扰、PDN……,千头万绪,令人无从下手。这个时候,条理清晰的思维导图对于我们梳理知识大有裨益,刚好,在《学习笔记开篇》里,就有这么一幅。

理清了知识脉络,接下来的就需要各个击破了。刚好,高速先生对这些基本理论或多或少都有研究,所以,各位有福了。

02

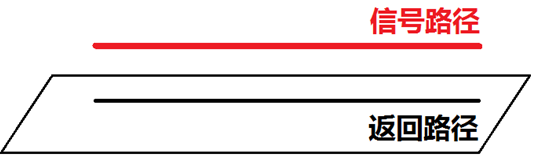

既然研究信号,首先需要了解信号的传输路径和返回路径,有人认为传输线中信号的传播速度取决于导体中电子的速度,事实真是这样吗?你需要戳这里:《学习笔记之传输线基础》

03

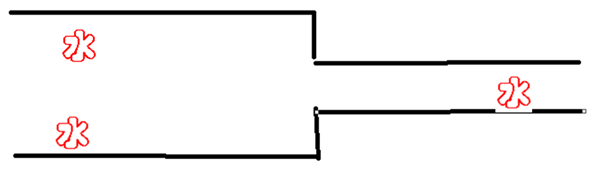

阻抗是信号完整性理论的一个重要概念,阻抗不连续,信号反射就会接踵而至,具体表现为过冲、振铃、回沟等,新手上路,该如何理解阻抗和反射呢?:《最简单的方式来理解阻抗、反射和端接》

04

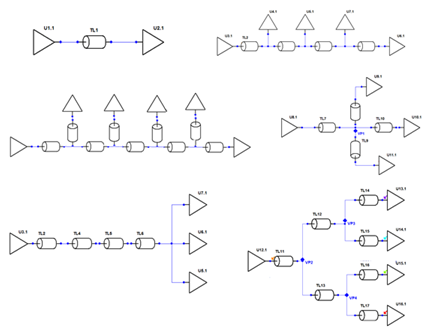

阻抗突变是产生反射的根本原因,端接的方法是通过在传输线的任何一端进行阻抗匹配来减小反射,此外,合理的拓扑也可以减少信号反射。这里有你想了解的端接和拓扑分类:《“围殴”拓扑和端接之开篇》

05

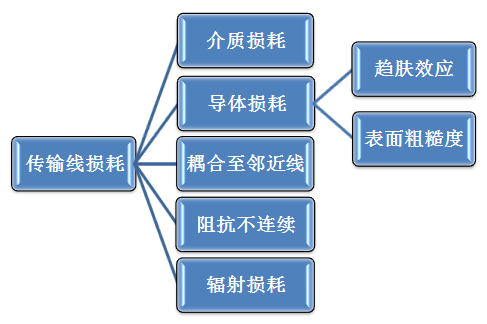

除了反射,损耗也是导致单一网络信号质量恶化的主要原因,什么是导体损耗?和介质损耗有什么区别?DkDf又分别代表什么?这二者跟高速板材又有什么关系?这篇文章可以解答你的困惑:《学习笔记之传输线损耗》

06

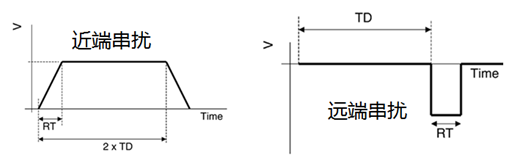

聊完单一网络的信号噪声问题,再说说多网络间信号的串扰,串扰本质上是能量的耦合,耦合形式分为容性耦合和感性耦合,途径是电磁场,具体表现形式分为近端串扰和远端串扰。如果你不知道我在说什么,猛戳这里:《学习笔记之串扰溯源》

07

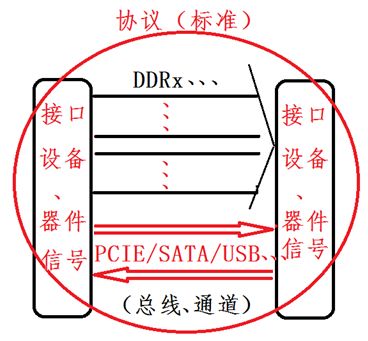

对于刚刚接触高速串行信号的菜鸟攻城狮,常常搞不清楚接口、总线、协议及信号等概念之间的关系,这篇文章为你拨开迷雾:《高速串行简史(一):信号、接口、协议及总线》

08

而作为研究高速串行信号的利器,S参数最初应用于射频领域,后来逐渐在信号完整性研究尤其是高速串行链路的分析中得到广泛使用,主要用于描述线性、无源互连通道如何与入射波相互作用,包含了互连通道的损耗、阻抗连续性、反射、延时、串扰等丰富信息。详见:《S参数入门及实战案例汇总》

09

电源是整个系统的动力源泉,与信号网络同等重要,同时,电源/地平面还构成了所有信号的返回路径。对于电源分配网络(Power Delivery Network,PDN)而言,研究重点在于电源分配系统的压降,可以从直流(DC)和交流(AC)两个方面进行分析,具体来说,就是直流压降(IR-drop)以及交流阻抗产生的纹波噪声。直流压降的基本原理比较简单,而对于交流阻抗的理解略显复杂,不过不用担心,可以参考:《原来你是这样的PDN》

10

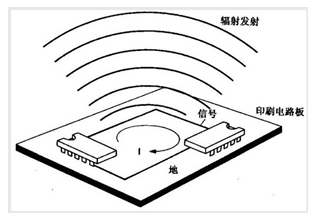

最后说说EMI噪声,PCB上的两类主要干扰源是电源分配网络的高频噪声以及高速信号回路产生的共模信号,所以对于PDN网络和高速信号回路的优化设计同时也可以减少EMI:《EMC学习之电磁辐射》

一口气看完这么多文章是对体力和耐力的巨大考验,不过,想想2019转眼过去了近三分之一,各位年初立下的Flag是否都已Gone with wind?如果你羞愧的低下了头,希望本系列的学习能让你重拾信心。

———— 你可能错过的往期干货 ————

-

集成机器视觉与运动控制的高速工业自动化应用的详细资料说明2021-03-12 1180

-

电磁兼容性的基本概念详细说明2021-03-03 1644

-

Bluetooth蓝牙的详细资料说明2021-02-26 3702

-

LabVIEW的程序实例详细资料说明2021-02-05 2328

-

数字信号处理的基本概念详细说明2020-09-29 1856

-

51单片机的指令系统的基本概念和详细资料说明2020-01-15 1545

-

5G视频通信及应用的详细资料说明2019-12-30 1713

-

电工口诀的详细资料说明2019-12-12 2102

-

GIS数字图像处理之遥感图像的基本概念和存储结构详细说明2019-09-29 1732

-

DSP教程之DSP数值运算基础总结的详细资料说明2019-03-12 1440

-

移动通信蜂窝概念系统设计基础的详细资料说明2019-02-27 1405

-

C语言教程之文件函数的详细资料说明2019-02-21 1068

-

数据库教程之数据库的基本概念详细资料说明2018-12-18 1290

-

高速运放详细资料2017-05-17 1650

全部0条评论

快来发表一下你的评论吧 !