如何采用51单片机和CPLD芯片构建出电路系统

控制/MCU

描述

一、引言

单片机市场可以用巨无霸来形容,其中51 单片机使用者就更多了,针对51 单片机无需更多的介绍,这里必须强调一点,只要你精通了51 单片机,以后在实际工作中选用其它单片机也很容易了,这就是初学者学习51 单片机的价值。选择51 单片机学习入门容易,倒不是说51 系列单片机比别的型号简单,其实在8 位单片机家族中,51 系列单片机算是复杂的,但51 单片机在中国推广最彻底,教程也是最丰富,基本不用看英文资料就能学好,所以特别适合初学者学习用。

下面说说CPLD,从近来跟学生和爱好者交往中发现,初学者都很“讨厌”它,问我为什么要把单片机和CPLD 放一块儿,那样不是增加了学习的难度吗?其实深入学习单片机后,你就会发现,单独一片单片机芯片,实在是不够用,稍微复杂的系统都会缺少接口资源,IO 口不够用。我们学单片机不能仅仅局限于LED(发光二极管,数码管等)驱动,输入还需要键盘、ADC,输出需要LCD、DAC等,当把这些对象同时放在一个系统当中时,就需要用到很多其它分离的接口IC(芯片),各种逻辑IC。

学完单片机后大家都会知道这些芯片:如74373,7432,74138……随着数字电子技术的发展,一种新的器件正在被广泛应用,那就是CPLD(ComplexProgrammable Logic Device) 复杂可编程逻辑器件,通俗的说就是可以把以上那些分离器件都放进去的一种可以二次开发的IC.关于CPLD 的详细介绍大家可以自己在网上浏览,很多很多。

二、单片机系统中几个典型电路介绍

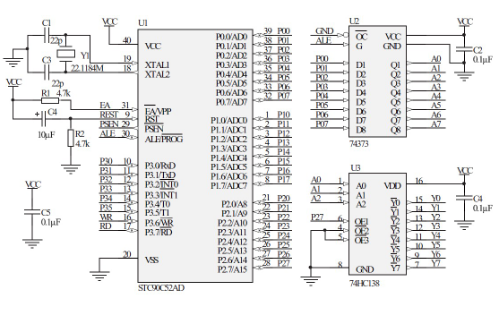

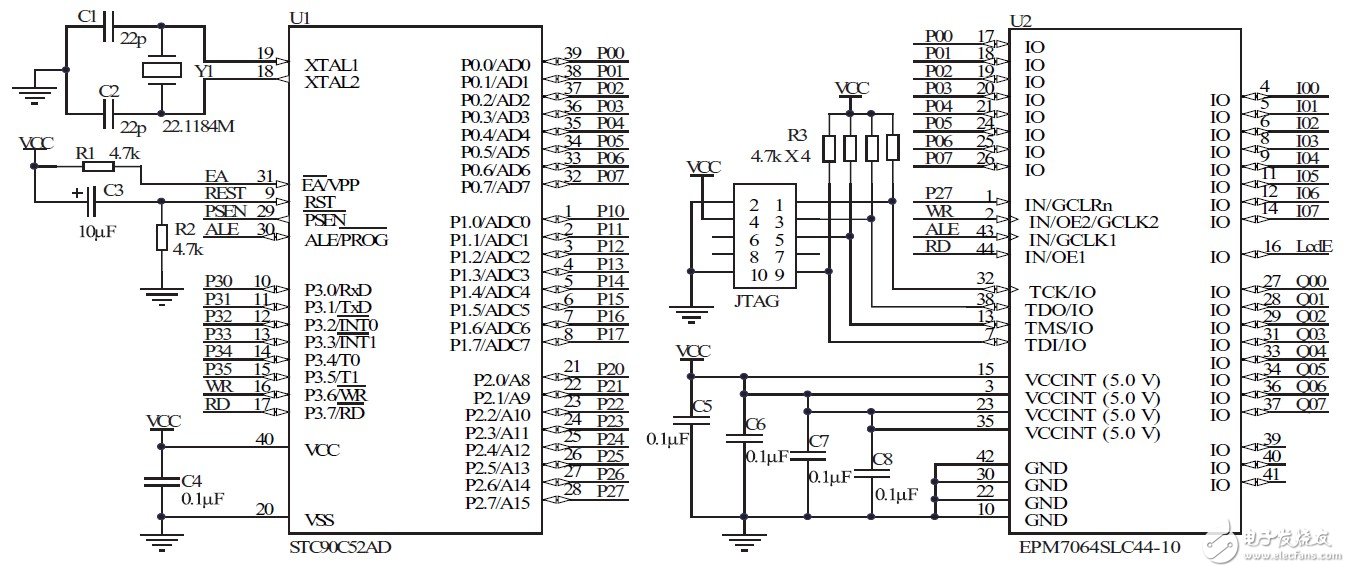

首先从熟悉的最小系统电路电路说起,如图1所示,图中用网络标号实现电路连接,这样绘制的电路图清晰整洁,U1 是经典的51 单片机 IC,复位电路和晶振电路是传统电路,这里C5电容是靠近单片机VCC引脚的,用来对电源滤波,图中其它芯片VCC 附近都有相同功能的滤波电容。U2 是经典的低八位地址锁存电路,这里的74373 也可以用74573 代替,U3 是地址译码电路,74138 实现连续8 个地址(1### #### #### #000 ~ 1####### #### #111,# 是无关位,可以是0 也可以是1,取决于电路其它部分的需要)对象扩展。

图1 MCU最小系统原理图

51 单片机给大家推荐STC 的89 或90 系列,其中90 系列已经有片内ADC 了,需要特别强调的是, 随着FLASH 技术的成熟,片内FLASH ROM从8K 到64K 任选,已经足够用了,所以现在很少有单片机系统外扩ROM 了,这样使得EA/VPP 和PSEN 引脚失去了原先的功能了,STC 的51 单片机已经将这两个引脚发展成P4 口了。

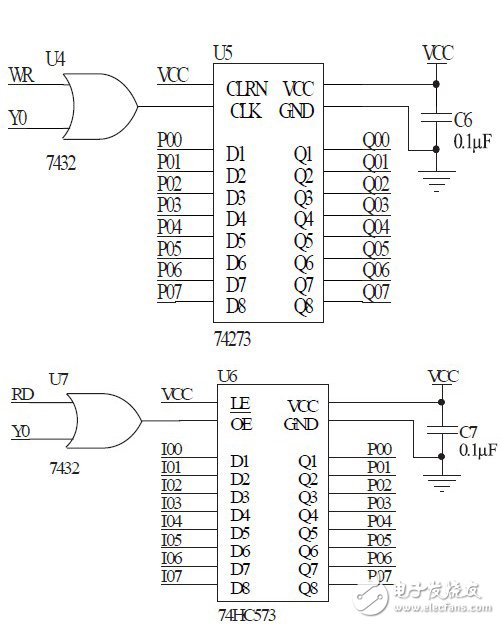

复杂的系统必然有很多输入输出接口,如图2所示,U5 是数据锁存器74273,扩展一个8bits 数据输出端口,U6 是三态数据缓冲器74573,扩展一个8bits 数据输入端口,分别用7432 实现读写时序接口匹配。

图2 MCU端口口扩展原理图

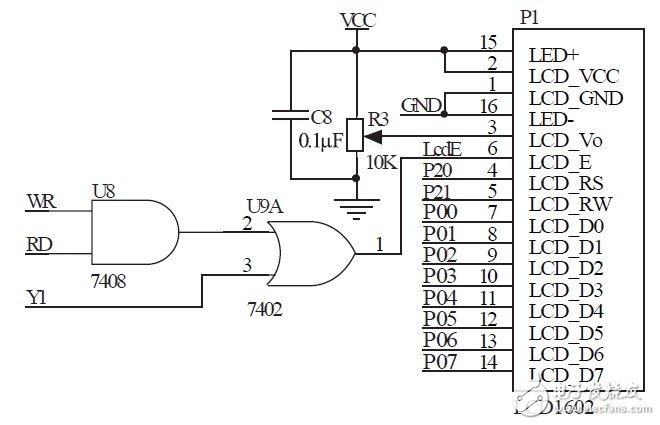

经典LCD1602 接口如图3 所示,这里7408、7402 逻辑门用来实现6800 时序(读写信号有独立接口的是8080 时序,这里只有使能信号E,需要外逻辑电路将读写信号相与合并使用)。

图3 LCD1602接口电路原理图

以上给出的系统还算不上是复杂系统,总共采用了8 块IC,一个实现特定功能的系统往往更复杂,需要采用的IC 会更多。能不能把这些分离的器件用CPLD 来实现呢?答案是肯定的。

三、单片机与CPLD接口设计

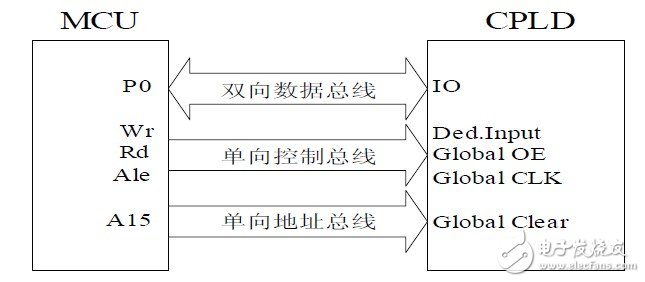

以上经典电路中,系统扩展使用了单片机总线模式,各个对象采用的三总线连接,根据这种电路结构,这里给出一种单片机同CPLD 的总线接口模式,如图4 所示。

图4 单片机与CPLD总线接口示意图

这里选择A l t e r a 公司早期的EPM7064SLC44-10 为例,这是很老的一款CPLD器件,是5V 供电。其实选择什么CPLD 型号并不是关键,关键是学习用CPLD 代替分立器件的思想和方法。数据总线P0 口同CPLD 一般IO 口相连,完成数据和低8 位地址传送;控制总线包括单片机读写控制信号Rd(P3.7) 和Wr(P3.6),以及地址锁存信号ALE(AddressLOCk Enable)和高位地址线A15(P2.7) 通过CPLD 的全局信号引脚输入,包括全局时钟输入:INPUT/GCLK1, 全局清零输入INPUT/GCLRn, 全局使能输入INPUT/OE1,INPUT/OE2, 这几个信号有专用连线与CPLD 中每个宏单元相连,保证信号到每个宏单元的延时相同并且延时最短。实际电路原理图如图5所示。

图5 MCU与CPLD接口电路原理图

这样一块CPLD 器件就代替以上除单片机外的7 块芯片了,在电路板上将节约大片的PCB面积,好处还远不止这些,因为CPLD 是二次开发的,其内部电路可以根据需要再次设计,反复修改,极大的增加了电路设计的灵活性。

读者看到这里,肯定对自己动手设计CPLD 电路充满了期待,下面介绍如何借助工具软件开发CPLD 内部电路。

四、CPLD开发介绍

一般来说,CPLD 生产商都有配套的开发工具, 这里介绍ALTERA 公司的一款易学易用的CPLD 开发软件MaxPlusII,虽然该公司最新版的软件是QUARTusII,但针对某些具体的器件,选择MaxPlusII 还是很方便的。该软件入门教程请到百度搜索《MaxplusII 设计CPLD 入门》,很多手把手的资料。

最容易的电路设计方法不外乎是直接绘制电路原理图。采用原理图输入,初学者甚至不需要额外学习就可以从事CPLD 设计。我们只需要在软件平台上从集成器件库调出对应的器件,绘制相同的电路原理图即可,实现以上功能电路原理图绘制完成后如图6 所示。

图6 原理图输入设计CPLD

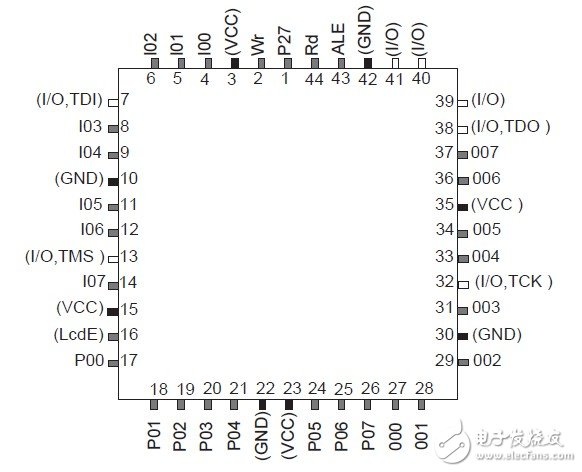

该原理图编译成功后,我们还需要根据实际电路连接图分配绑定引脚,引脚绑定如图7 所示,再编译就可以得到可供下载的文件*.pof 了,最后只需要将下载电缆连接到电路板上,仍然通过该软件即可完成下载。

正因为CPLD 的IO 脚是可以随意分配的,通常我们会结合实际的PCB 板设计布线的便利来调整引脚分配,引脚分配更改后,只需要重新分配引脚再编译下载即可。

图7 CPLD引脚绑定

除了原理图输入外,复杂的CPLD 器件开发,一般用硬件描述语言设计,常用的硬件描述语言有VHDL,VerilogHDL,这些硬件描述语言的掌握是需要系统学习的,基于硬件描述语言的片上系统设计,FPGA开发目前已经成为高薪职业,社会需求巨大。用硬件描述语言开发CPLD 的方法与前面的原理图输入法类似,也需要编译纠错,时序仿真,引脚绑定,最后编译下载即可。

给CPLD 下载完程序,这块芯片就是你所设计的逻辑时序电路了,通常比分离元器件功耗更低,性能更优。

真正是基于上述思想, 笔者将51 单片机同CPLD 相结合,开发了一款适合初学者使用的学习板--Mini51 板。

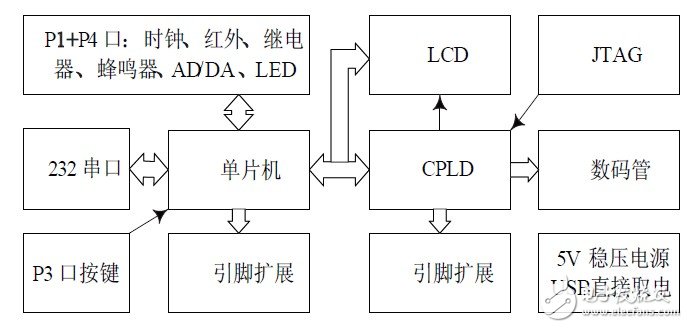

五、Mini51板概述

Mini51 板体积小巧(11×8 厘米),适合用户随身携带,只要PC 机加一根USB 线就可以做硬件实验了,特别适合大专院校学生和爱好者自主学习用。实物图如图8 所示。

图8 Mini51板实物图

Mini51 板系统结构如图9 所示,该板采用单片机+CPLD 结构,单片机为主,CPLD 为辅。与单片机相连的模块有:P1 口接发光二极管、蜂鸣器、继电器、AD/DA,P4 口(STC 单片机PLCC-44封装特有)接实时时钟DS1302、红外接收器,P3口接232电平转换电路和4 个按键,单片机P0 口和P2 口以及P3.6、P3.7 作为总线使用,CPLD 直接驱动4 位数码管,并给LCD 提供使能信号,单片机和CPLD 引脚分别有扩展接口,板上集成5V稳压电源,可以外接DC9V 电源,也可以从计算机USB 口直接取5V 电源。

图9 Mini51板结构图

单片机首选STC89C5X, 该系列单片机内部集成MAX810/STC810 专用复位电路, 内置看门狗, 超强抗干扰, 轻松过2KV/4KV 快速脉冲干扰(EFT), 加密性强,STC89C52RC ~STC89C58RD+ 系列与Intel8051 管脚兼容,宽电压,5.5V ~ 3.4V 给复位信号后能正常工作,PQFP-44,PLCC-44 封装有P4 口。

STC89C51RC 有3 个定时器/ 计数器,1280 字节大容量内部数据 RAM ,特别是该系列单片机支持ISP 编程,开发无需高价的编程器,可实现远程升级,在ISP 下载编程时可设置6 或12 时钟/ 机器周期模式,在6 时钟模式,比普通51 速度快一倍。

CPLD 有两种型号可选,ALTERA 的EPM7064和ATMEL 的ATF1504。

-

51单片机加CPLD让系统更高效2012-02-29 9258

-

纯单片机和纯CPLD设计的优缺点分析2018-10-17 15703

-

51单片机+CPLD让系统更高效2011-11-25 7775

-

CPLD加51单片机让系统更高效2012-01-17 6828

-

51单片机为主的电路系统求助2019-10-29 1153

-

单片机复位电路系统是如何实现的2022-01-17 1317

-

基于单片机的蓝牙控制窗帘电路系统的设计资料分享2022-03-02 977

-

单片机应用系统的CPLD 应用设计2009-05-14 1090

-

CPLD扩展51单片机寻址范围2009-09-14 566

-

单片机应用系统的CPLD应用设计2010-07-14 708

-

CPLD/FPGAS/51单片机通用的下载电路接法2009-07-16 2720

-

51单片机最小系统是什么?51单片机最小系统的电路介绍2019-08-12 10321

-

理解51单片机最小系统的工作原理2021-11-10 1886

-

51单片机最小系统电路设计2021-11-17 1024

-

51单片机最小系统的构成2023-07-15 13584

全部0条评论

快来发表一下你的评论吧 !