Micron可管理NAND 适用于移动设备的嵌入式大容量存储

嵌入式技术

描述

与多年前相比,现在的移动消费电子装置结构复杂,功能丰富,能够存储大量音乐、照片和视频内容。让人欣慰的是,存储系统的体系结构能够适应这些新的数据密集型应用。例如,适用于大容量存储的高性价比紧凑型 NAND 闪存就替代了手机、MP3 播放器和数码相机中使用的 NOR 闪存和其它非易失性存储装置。

随着工艺技术的进步,存储器密度大约每 12 至 18 个月即提高一倍。对于 NAND 闪存而言,这意味着对多层单元 (MLC) 技术的重视程度日益提高。传统的单层单元 (SLC) NAND 闪存每个存储单位能够存储一个数据位。MLC 技术能够实现在单个存储单元中存放多个数据位,数据的存储容量达到相同大小 NAND 闪存设备的两倍。MLC NAND进一步加快了 NAND 闪存的每字节成本,并为新的应用提供了发展空间。市场趋势显示MLC 闪存的出货量在 2007 年初超过了 SLC 闪存。

MLC NAND 的采用,NAND 产品周期的缩短让系统设计人员的工作越来越复杂。传统的SLC NAND 闪存,每 512 字节只需要一位错误校验码,大多数新型嵌入式处理器都可以直接为其提供支持。而现在的 MLC 闪存设备却不同,需要每 512 字节扇区 4 位校验码,将来的 MLC NAND 对 ECC 的要求将超过每 512 字节扇区 8 位校验。高级 ECC 算法的实现和硬件加速电路对嵌入式处理器和主机系统在设计方面构成了很大的挑战。

系统设计人员还必须能够应对 NAND 闪存的快速更新换代,以及不同供应商之间产品功能差别带来的挑战。系统设计人员和处理器制造商为跟上 NAND 闪存制造商的步伐必须在硬件和软件开发方面进行更多资源投入。更为重要的是,额外的开发工作可能会对上市时间产生较大影响。

Micron 可管理 NAND

正确的解决办法是:采用 Micron 的创新式可管理 NAND 产品。可管理 NAND 闪存将Micron 的高质量低成本 NAND 闪烁存储器与半高型高速MultiMediaCard. (MMC) 控制器结合在一起,并采用了符合 JEDEC 标准的 BGA 封装和高级 10 信号接口。

MMC 是一种特征突出的高性能接口,无线消费电子应用中的几乎所有嵌入式处理器均支持该接口。如果使用 8 位数据总线和标准 BGA,可管理 NAND 支持 52 MB/秒(峰值)的接口速率。因为处理器的接口没有变化,所以 BGA 中的 NAND 底层技术可以在不影响应用的情况下更改。这种方法能够延长更高密度解决方案的使用寿命,从而能够通过一种系统主板设计支持多种元件密度。

可管理 NAND 的另一个主要优势是消除了对主机处理器上特定供应商闪存固件及驱动程序的依赖(这种依赖性使得主机处理器需要协调程序/擦除/读取功能并管理坏块和坏位)从而将标准的 NAND 成为简单的读写设备。主机处理器不必考虑诸如 NAND 块大小、页面大小、新增功能、进程产生、MLC 与 SLC、平均读写算法以及 ECC 要求等不必要的NAND 功能细节。只要具有工业标准的通用 MMC 设备驱动程序即可让处理器与 Micron可管理 NAND 以及其它供应商生产的符合相同标准的产品实现无缝配合。

可管理 NAND 设备概念已被提议作为一种行业标准被大家接受。The

MultiMediaCard Association 和 JEDEC 于 2006 年 12 月联合宣布将 eMMC. 作为此类别闪烁存储设备的名称和商标。

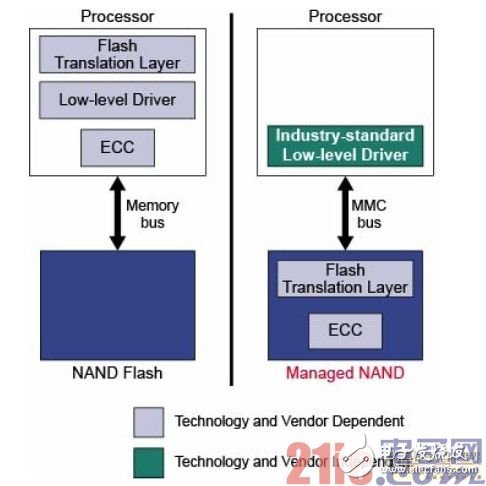

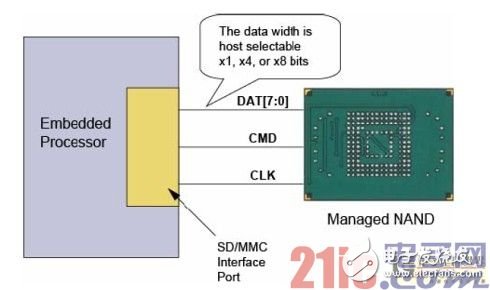

图 1:NAND 闪存配置可管理 NAND 功能

可管理 NAND 是一种具有 MMC 接口的多合一存储器和控制器设备。它符合MMC 系统规范版本 4.2,并且与 MMCplus.、MMCmobile.、MMCmicro. 以及过去的MMC 完全兼容。

主要功能:

。 。 可同时支持 MMC 和 SPI 模式操作

。 。 主机可选择 x1、x4 和 x8 I/O

。 。 52 MHz 时钟速度(最高)

。 。 416 Mb/s (52 MB/s) 数据速率(最高)

。 。 3.3V 和 1.8V 工作电压

。 。 密码保护

。 。 永久和临时写保护

。 。 内部 ECC、平均读写算法和数据块管理。

可管理 NAND 的 JEDEC 标准 BGA 封装具有集成诸如 DRAM 等其它存储器组件的潜在能力,可以帮助系统设计人员实现高度集成的系统存储解决方案。

表 1:可管理 NAND 属性

图 2:可管理 NAND 封装细节

注释:尺寸单位为毫米。

系统实现方式

如果主机处理器可以与标准 NAND 闪存直接接口,则可实现最低的物料清单 (BOM) 成本。除非处理器具有用于 NAND 所需的内置支持,否则 NAND 闪存的操作复杂性可能会令系统设计人员头痛。

可通过软件实现相对简单的 SLC NAND 闪存 ECC 算法,但是更高性能的应用需要硬件支持。将来的 MLC 设备将需要更复杂的 ECC 和数据块管理功能,并且会不断地将需求附加到处理器支持硬件上。

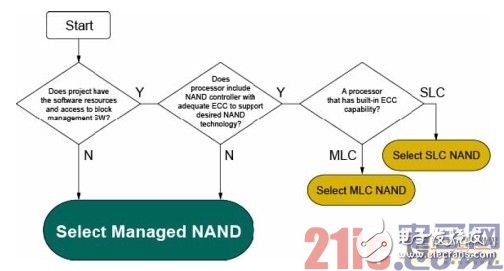

在选择 NAND 解决方案时,系统设计人员应考虑开发资源以及系统性能与应用需求之间是否匹配。开发团队是否具有软件开发资源,并且具有 NAND 存储器数据块管理软件代码?选择用于项目的嵌入式处理器是否具有适用于 NAND 设备的 ECC 功能?如果具有,ECC 是否支持 MLC NAND 闪存所需的更大位校验要求,以及是否具有应用所需的足够性能。

图 3:NAND 存储器选择树形图

另一个要考虑的问题是不同供应商原始提供的 NAND 设备之间的兼容性,以及如何将系统设计扩展到后几代 NAND 闪存。

在许多情况下,开发资源的缺乏、处理器的限制,以及对性能的要求使得可管理 NAND 成为适用于项目要求的最理想的解决方案,它同时还具有成本最低,上市时间最短的特点。

可管理 NAND 消除了 SLC/MLC 和不同页面尺寸等 NAND 闪存依赖性。其中包括了

一个标准数据块级接口以及一个错误管理和平均读写控制器,从而让处理器不必处理这些任务。根据处理器提供的 NAND 闪存的不同,这一特性能够节省宝贵的处理时间和代码存储空间。该功能即可消除对更高性能处理器或额外硬件/软件设计资源的依赖。

可管理 NAND 可以连接到无线和消费电器设备中使用的众多嵌入式处理器上的

SD/MMC 端口。除电源外,这一简单的接口还具有 3、6 或 10 个信号 I/O,对应于时钟总线、命令总线以及 x1、x4 或 x8 数据总线。

可管理 NAND 控制器被优化为能够利用程序缓存和读取缓存等特定 NAND 闪存性能

特征。这些特性能够在原始 NAND 实现中提供明显的性能提升。还可以直接从 NAND 启动系统。

图 4:系统结构示意图

总结

对于需要大容量数据存储的移动消费电子设备而言,NAND 闪存从技术角度而言是您最合适的选择。NAND 闪存已经从传统的 SLC 发展到 MLC NAND,MLC 需要更高级别 的 ECC。设计人员面临的挑战是一方面要符合今后 MLC NAND 闪存设备日益提高的 ECC 要求,另一方面仍要支持所有 NAND 设备所需的数据块管理和平均读写例程。

Micron 的可管理 NAND 让系统设计过程中 NAND 闪存实现方式的复杂程度有所降

低。它将内部控制器和 NAND 闪存部件结合在 JEDEC 标准 BGA 封装中。它具有一

个可以被大多数移动和消费电子设备中多种处理器支持的 MMC 接口。

如果嵌入式主机处理器能够与 NAND 闪存直接实现接口,则系统设计人员可以获得很低的 BOM 成本。但是,如果资源有限,并且处理器无法直接与 NAND 闪存实现接口,则可管理 NAND 能够提供更吸引人的解决方案。

Micron 的可管理 NAND 能够以便于使用的 BGA 封装方式提供所有必需的 NAND 闪

存管理功能,节省了大量以前需要进行硬件和软件开发的资源。除了提供所有主要功能外,可管理 NAND 还可以通过分担处理器承担的多项底层任务负荷,提供更高的性能。

-

SD NAND和SPI NAND的区别2024-06-04 4079

-

嵌入式Linux存储设备包含什么2021-12-21 911

-

适用于自主机器的嵌入式系统是什么2021-12-20 1192

-

嵌入式系统中的数据存储和管理的相关资料分享2021-12-17 770

-

适用于嵌入式管理器的SmartMesh IP简易入门指南2021-05-10 893

-

什么是适用于移动设备的嵌入式大容量存储?2019-09-03 2258

-

什么是可管理NAND?2019-08-29 1521

-

可用于各种广泛的数字消费产品的全球最小嵌入式NAND闪存产品2018-09-13 2581

-

如何设计适用于嵌入式系统的加密IP核?2018-07-24 4433

-

利用Micron可管理NAND 适用嵌入式大容量存储2018-04-11 1225

-

NAND Flash在嵌入式Linux平台下的驱动实现2018-02-12 1048

-

适用于移动设备的嵌入式大容量存储2017-10-17 651

-

东芝发布最大容量嵌入式NAND闪存2008-08-14 3863

全部0条评论

快来发表一下你的评论吧 !