pcb覆铜规则设置

电子说

描述

pcb覆铜规则设置

1、pcb覆铜安全间距设置:

覆铜的安全间距(clearance)一般是布线的安全间距的二倍。但是在没有覆铜之前,为布线而设置好了布线的安全间距,那么在随后的覆铜过程中,覆铜的安全间距也会默认是布线的安全距离。这样与预期的结果不一样。

一种笨方法就是在布好线之后,把安全距离扩大到原来的二倍,然后覆铜,覆铜完毕之后再把安全距离改回布线的安全距离,这样DRC检查就不会报错了。这种办法可以,但是如果要重新更改覆铜的话就要重复上面的步骤,略显麻烦,最好的办法是单独为覆铜的安全距离设置规则。

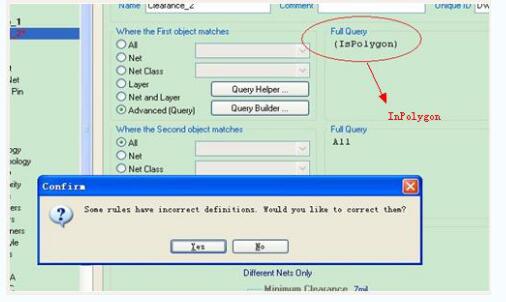

另一种办法就是添加规则了。在Rule的Clearance里面,新建一个规则Clearance1(名称可以自定义),然后再WheretheFirstObjectmatches选项框里面选择Advanced(Query),单击QueryBuilder,然后出现BuildingQueryfromBoard对话框,在此对话框中第一行下拉菜单中选择默认项ShowAllLevels,在ConditionType/Operator下面的下拉菜单中选择ObjectKindis,在右边的ConditionValue下面的下拉菜单中选择Ploy,这样QueryPreview中就会显示IsPolygon,单击OK确定,接下来还没有完,完全保存时会提示错误:

接下来只要在FullQuery显示框中将IsPolygon改为InPolygon就可以,最后在Constraints里面修改你自己需要的覆铜安全间距。有人说布线的规则优先级高于覆铜的优先级,覆铜的话也肯定是遵守布线安全间距的规则,需要在布线的安全间距规则里面把覆铜这个例外给加上,具体做法是在FullQuery里面注释上notInPolygon。其实这么做完全没有必要,因为优先级是可以更改的,设置规则的主页面左下角有个选项priorities,把覆铜的安全间距规则的优先级提高到高于布线的安全间距规则,这样就互不干扰了,完毕。

2、pcb覆铜线宽设置:

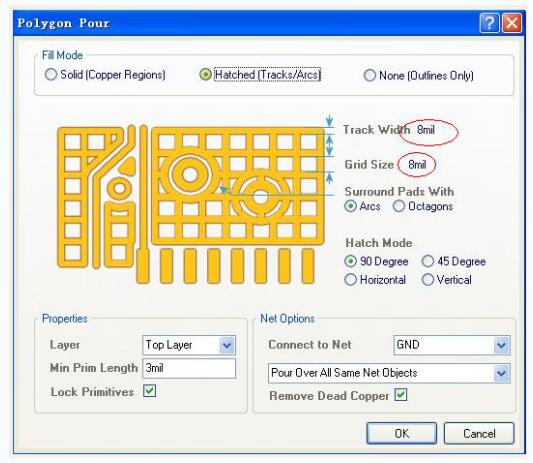

覆铜在选择Hatched还有None两种模式的时候,会注意到有个设置TrackWidth的地方。如果你选择默认的8mil,并且你覆铜所连接的网络在设置线宽范围的时候,最小的线宽大于8mil,那么在DRC的时候就会报错,在刚开始的时候也没有注意到这一细节,每次覆铜之后DRC都有很多的错误。

是在Rule的Clearance里面,新建一个规则Clearance1(名称可以自定义),然后再WheretheFirstObjectmatches选项框里面选择ADVANCED(Query),单击QueryBuilder,然后出现BuildingQueryfromBoard对话框,在此对话框中第一行下拉菜单中选择ShowAllLevels(默认为此项),然后在ConditionType/Operator下面的下拉菜单中选择ObjectKindis,然后再右边的ConditionVALUE下面的下拉菜单中选择Ploy,这样在右边QueryPreview中就会显示IsPolygon,单击OK确定保存退出,接下来还没有完,在FullQuery显示框中将IsPolygon改为InPolygon(DXP中的bug必须这样改,2004版本好像不用改),最后一步了,下面就可以在Constraints里面修改你自己需要的间距了(根据你们的制版工艺水平)。这样就只影响铺铜的间距,不影响各层布线的间距了。

-

【PCB小知识 10 】覆铜技巧及设置2015-12-29 62158

-

pcb覆铜技巧2016-03-01 6116

-

PCB覆铜知识必知2018-04-25 5431

-

PCB覆铜规则2019-05-29 2047

-

覆铜不当会得不偿失!PCB覆铜技巧分享2019-09-17 5169

-

PCB板覆铜规则2010-08-28 1139

-

PCB设计技巧_覆铜技巧2016-02-26 1841

-

AltiumDesigner高级覆铜布线规则2016-04-11 1121

-

PCB设计教程之PCB覆铜技巧的详细资料说明2018-11-22 3818

-

PCB的覆铜技巧和方法有哪些2019-11-19 6002

-

什么是PCB 覆铜?PCB覆铜的作用及方法2023-07-03 3533

-

PCB覆铜的作用、正确方法、设计2023-07-14 12248

-

什么是PCB覆铜?pcb覆铜有什么作用2023-08-28 3673

-

ad覆铜规则怎么设置距离2023-12-20 7485

-

Altium designer PCB高级规则—覆铜高级连接方式2023-12-22 1242

全部0条评论

快来发表一下你的评论吧 !