如何在高速设计过程中的保证信号完整性

EDA/IC设计

描述

在电路设计中,一般我们很关心信号的质量问题。一般的设计理念会基于理论和理想的模拟,理解信号从发射器传输到接收器,但实际应用往往不如预期,因为从理论到实际应用都往往会导致不可预知的结果。

什么是信号完整性?

当电流通过铜迹线时,根据源组件(发射极)的驱动器传递的能量,可能会出现不同的行为。 信号完整性仿真是验证通过铜迹线的信号质量的理想方式,确保整个系统安全可靠。信号完整性分析是一种后期布局模拟过程,可准确反映现实中发生的情况,以及在日常使用产品中会发生哪些行为,从而使设计更加可靠。

需要注意的问题

高速部件的使用在市场上一直在增加,而低速部件的使用继续下降。 这种趋势甚至在今天仍然持续,高速组件的不断增长使我们在复杂系统中保持信号质量的挑战。

可以以各种方式扰乱信号,包括损耗,串扰效应,反射,皮肤效应和许多其他干扰。这些信号干扰问题在诸如DDR 2/3/4的技术中进一步复杂化,其中每个信号需要同时到达以便在保持相同时钟速度的同时从存储器读取。

通常使用快速引脚驱动器来实现良好的信号时序,同时还沿着铜迹线提供足够的能量。 尽管这些引脚驱动器可以帮助最小化信号完整性损失,但是长的传输线将受到干扰。

要理解的一些理论应用:

过渡电长度(TEL)被定义为信号变化期间电磁波的移动(上升时间(RT)/下降时间(FT))):

•TEL = RT / FT *信号速度

使用FR-4的PCB构建上的轨迹的大致速度为:

•15厘米/秒(6英寸/秒)

具有例如上升/下降时间。 300 ps这意味着:

•TEL = 0.3ns * 15cm / ns = 4.5cm(1.77英寸)

如果Trace长于TEL的20%,我们将得到一条传输线和Re:

•反向开始为= 0.3 ns * 15cm / ns * 0.2 = 9 mm(350 mil)

这几乎是什么? 长度超过9mm(350mils)的铜迹线像传输线一样,在设计过程中需要特别注意。

风险分析

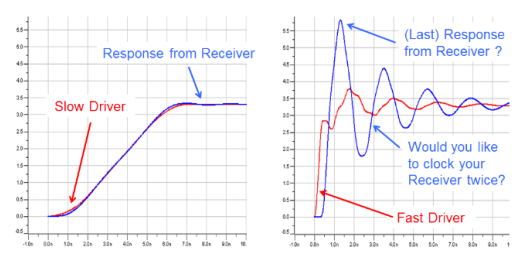

因为有不同种类的扰动可以产生铜迹,如果不检查系统中的信号质量,还会有几个不同的风险和后果。 例如,我们来看看一个反应问题。 信号从发射器发送到接收器,但是在接收器的引脚处观察到一些流过的能量,如下面的图1所示。

图1 - 从发射器到接收器的信号反射问题

观察此效果时,我们可以看到信号的各种失真,如可能会烧毁芯片的过冲或可能会切换设备两次的下冲。 在第二种情况下,我们还应该注意回铃,也可能会再次切换设备。 在这两种情况下,这些风险都很高,而信号质量问题可能会为原型和再转动带来额外的成本。 当产品在市场上时,甚至可能会导致一些非功能性系统。 除了技术风险之外,还会影响公司的预算来考虑,因为成本开始逐渐失控,每一轮的原型都是这样。

在最糟糕的情况下,在原型阶段没有发现的问题将进入市场,还有一些错误和问题仍在等待被发现。 在这样的情况下,当客户退货时,我们可能会花费大量资源来修复或更换产品。 而公司最后要处理的是被召回的产品有害品牌在这个过程中的声望和预算。

解决方案

如何避免信号完整性问题,并避免所有这些潜在问题? 第一步是彻底研究从一开始就遇到的问题,并在整个设计过程中做出良好的设计决策。 换句话说,不要在没有具体的成功计划的情况下潜水。

计划应该是什么? 最常见的方法是调整传输线的阻抗。 这需要阻抗控制路由。 如果您需要更大的适配,则可以在信号中添加一个终止。 这也将调整阻抗,从而避免PCB上太宽的痕迹。 通过这样做,终端组件可以吸收传输线上流过的能量,从而保护接收器。

避免扰动的另一个关键因素是计划您当前的返回路径。 避免在下面(或以上)关键信号区域内分裂电源平面。 还可以对这些关键信号使用盲孔和埋孔,因为通孔过孔的短截线可能会充当天线,并会对信号产生不必要的干扰。

图2 - Altium Designer制造的Via拼接,提供优化的电流返回路径

Altium Designer的用处

Altium Designer包括一个完整的信号完整性分析工具,可以帮助我们检测扰动和扭曲板上的信号。 首先,它包含一个预先布局分析,以便对可能发生的问题进行估计对你的项目 这对于在设计过程中早期发现信号问题而做得更好,这是有帮助的做出布局时的决定。 当然,在设计的这个阶段,分析没有信息关于真实层堆栈,只能对结果进行估计。 当板完成后,路由和所有铜区域,则可以利用后布局分析来查看信号的真实扰动。

像往常一样,为了运行模拟,需要模拟模型。 在信号完整性仿真的情况下,所有IC连接到我们想要模拟的信号都需要IBIS模型。 Altium Designer可以管理基本的IBIS模型,组件,如电阻器,电容器,电感器,连接器,晶体管,二极管等等...我们需要关心的唯一的事情是IC的仿真模型。 这些通常可以从制造商的网站下载。

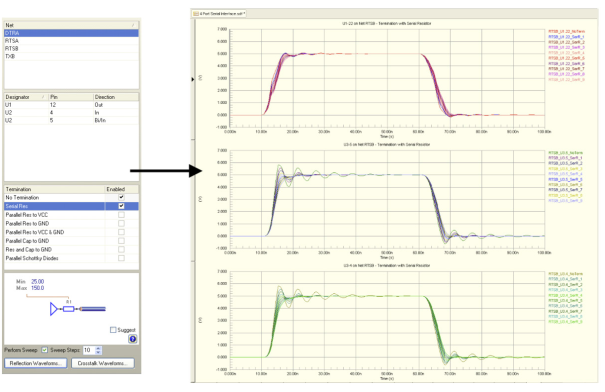

通过板上的路由和连接到组件的IBIS模型,现在可以启动信号完整性模拟。 运行分析并调查您的信号的质量。 如果您看到意外的扰动,那么您将需要再次运行模拟。 这一次,使用可以添加到信号中的可能终端的变体。 Altium Designer将在同一图表上生成具有这些端接的信号,以便您可以了解调整关键信号需要什么样的终端。

现在知道需要哪个终止,还可以运行一个额外的分析,以确定你的组件需要什么价值,这样可以对信号做出最好的适应。 这是一个参数化仿真,可以改变终端组件的值,看到哪个值最有帮助。

图3 - 下拉电阻终端的参数仿真

结论

借助Altium Designer中的信号完整性仿真,我们可以轻松地在路由过程之前和之后成功浏览高速板的复杂性。 不然将需要花费大量的时间来规划当前的返回路径,信号时间和层叠层,然后才能开始路由跟踪。通过后期和预布局模拟和仔细规划的组合,每次都能够产生清晰的信号。

- 相关推荐

- 热点推荐

- 电路设计

- 信号完整性

- Altium Designer

-

高速信号的电源完整性分析2012-08-02 3613

-

如何保证脉冲信号传输的完整性?2021-04-07 1925

-

高速电路信号完整性分析与设计—高速信号完整性的基本理论2012-05-25 2112

-

高速PCB电路板的信号完整性设计2017-11-08 1678

-

PCB高速设计信号完整性怎样保持2019-12-10 3061

-

基于信号完整性的高速PCB设计流程解析2019-10-11 2648

-

PCB高速设计信号完整性5个经验2022-02-09 1017

-

高速电路信号完整性分析与设计—信号完整性仿真2022-02-10 2249

-

信号完整性分析科普2023-08-17 9236

-

pcb信号完整性详解2023-09-08 2553

-

在高速设计中,如何解决信号的完整性问题?2023-11-24 1944

-

什么是信号完整性2024-05-28 3917

-

高速电路中的信号完整性和电源完整性研究2024-09-25 488

-

听懂什么是信号完整性2024-12-15 1385

-

IDT信号完整性产品:解决高速信号传输难题2026-03-04 620

全部0条评论

快来发表一下你的评论吧 !