SRRC传导辐射过不了?AD软件怎么搞?看大咖们怎么说

电子说

描述

SRRC传导辐射过不了,有人遇到过这种问题吗,怎么解决的?

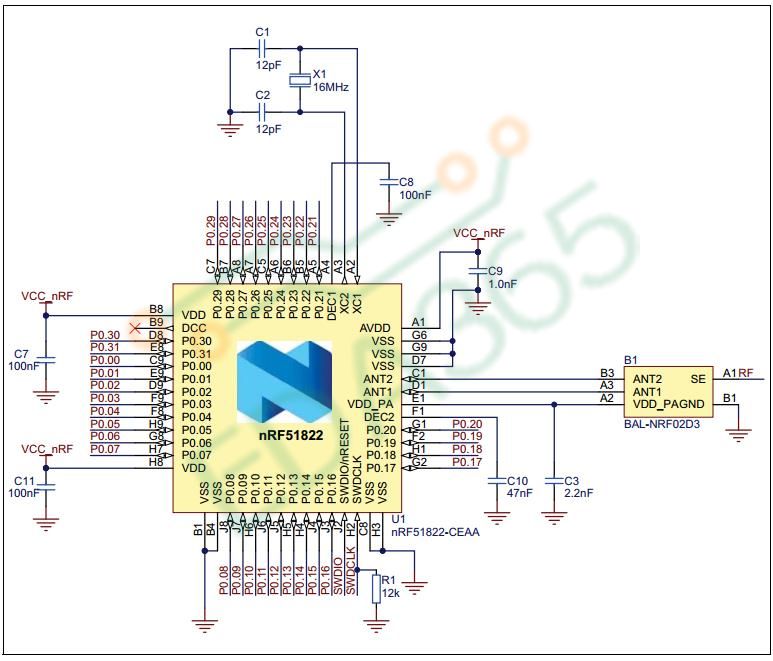

EDA365-WH:问一下,原理图是谁提供的,芯片到B1之间为何射频通道无匹配?你测试的是什么信号,现在的信号像是单音信号,而不是射频调制信号?

提问者:原理图是巴伦的规格书中参考设计。

提问者:蓝牙认证常用的三种调制,怎么会不是调制信号?11110000、10101010、还有个PRBS9,这里说的是发出来的数据包格式,调制方式是:GFSK。

网友1:是传导杂散还是辐射杂散?传导 ?不像是其它地方的干扰,传导能扫到,辐射根本就没有,感觉是芯片或者巴伦出来的。

EDA365-WH:蓝牙设置变化频点的话,这个干扰点是否变化?

提问者:有变化

网友2:检查下电源,看是不是电源带入的。

EDA365-WH:给个channel39,即输出是中间频点的,

目的是看这个信号和主信号之间的关系。从上面两张图的表现看和主信号间隔32MHz。但奇怪的是现在只能看到一边,或者上边,或者下边很不合理。所以需要你主信号为chan39的测试结果,看看是否两边都有?

参考的PCB 走线,我个人认为这张图上的AVdd和VDD 连在一起,不是好设计。调试时,你试试A1脚的电源单独用外部电源供电。

提问者:之前都是在实验室测试的,刚才弄了一个小时,在公司测,竟然测不到那个干扰。有自己测试过传导杂散吗,看看我是不是哪里没有设置到?

EDA365-WH:测试杂散的过程:1、设置测试信号范围,通过start和stop;2、设置RBW;3、峰值检波设定。

有个前提,设备要正常工作,输出满足要求的调制信号和对应的输出功率。

提问者:SPAN BW sweep 都是跟实验室一样的设置,检波方式尝试了峰值检波、RMS检波等都一样的看不到那个干扰,我现在也不知道这个设备正不正常了?

EDA365-WH:从现在的视频上看射频信号,它都不占带宽了,粗看上去更像一个单音信号了。

02

各位大神,请教一下,像这种SSMP连接器焊锡位置跟产品射频性能(驻波)有关系吗?

何老师:如果频段很高,就有关系。有多大关系?可用HFSS仿真。厂家要求是对的。建议在EDA365网站问这个问题。

提问者:好的,谢谢何老师,但我跟厂家沟通过,说没关系,只跟可靠性有关系。我们是Ku波段以下,请问影响大吗?

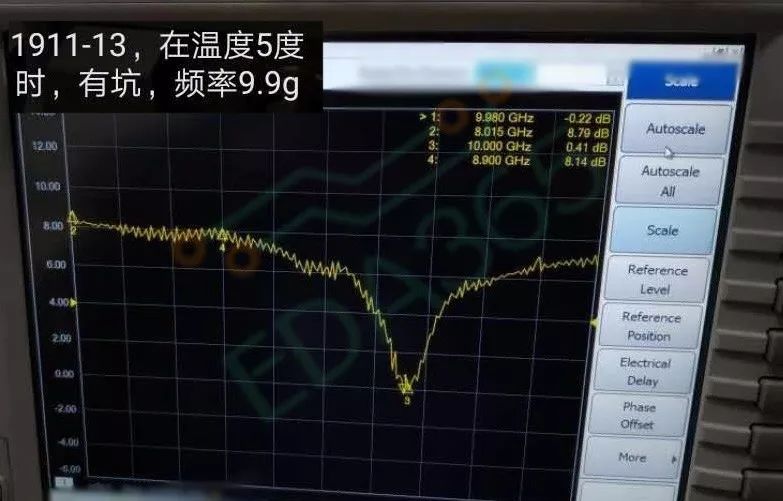

出现了这个谐振峰问题,请问是连接器焊接的问题吗?

网友1:你测下驻波?

提问者:驻波没问题,连接器的接地位置应该不会导致谐振产生吧?

EDA365-WH:肯定有影响呀。

提问者:为什么是在一定温度下产生呢?也不是最低温度?

EDA365-WH:Eda365 网站上有片帖子,说明一个SMA插座的接地孔设计不当,直接导致了一个谐振点。产生的根本原因是出现了一个谐振体,比如空隙等。

提问者:您的意思是焊缝有问题,而不是接地距离的问题?

EDA365-WH: 你的高低温度范围是多少?

提问者:-55到+85

EDA365-WH:其它什么都不变,只有温度变化,在5摄氏度下发现10G谐波?完整描述是这样吗?

提问者:是的,您认为是什么原因导致的?

EDA365-WH:因为看你仪表输出,本身带有增益,说明,你现在的测试不仅仅是接插头。所以建议,1、先探明一下这个谐振点发生的位置到底在哪儿?方法:1、有源电路扰动,2、接插头挤压扰动。

提问者:挤压扰动的意思是?

网友1:驻波没问题的话,你可以弄点吸附材料,看能不能改变一下谐振点。

提问者:好的,我做工艺的,也不太懂,我让他们试试

EDA365-WH:用手用力压,力量造成的SMA接触位置形变一般会比你说的几十度温度变化造成的形变大。

提问者:好的,我让设计师试试哈,谢谢。

03

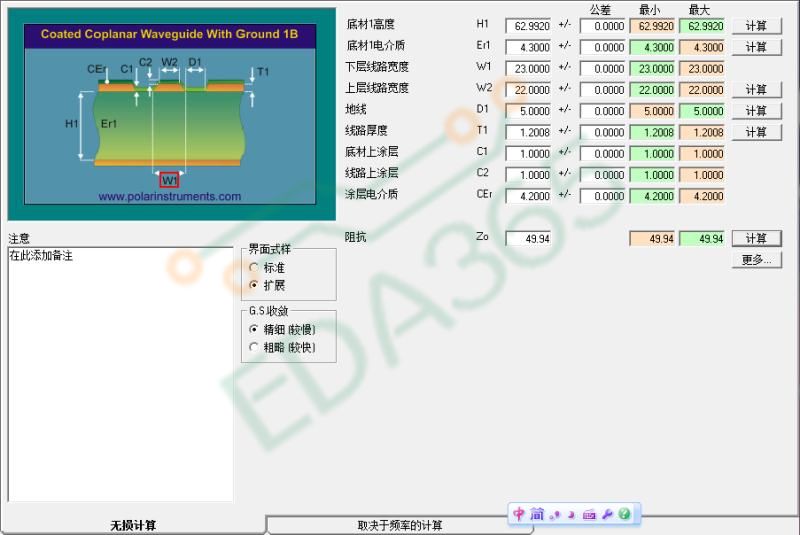

请教下,si9000算阻抗的时候,表层铜厚的选择,是要加电镀厚的铜厚吗?如果1oz的基铜厚,计算的时候是应该按1.4mil计算还按加镀铜后的总厚度2.9mil计算?

很多厂家给我是按1.4mil计算,然后调整的,是不是不对啊?请各位老师给个意见和看法,谢谢!

网友1:你让他给你出阻抗报告就行了,让他们控制好。

网友2:很多工厂不愿意给阻抗报告的。

网友1:那他们怎么保证他们控制的阻抗在范围内,这个说法不合理吖!

网友2:很多工厂都做不好阻抗的。

网友3:双面板怎么做50欧阻抗啊,1.6mm板厚。

网友4:共面地。

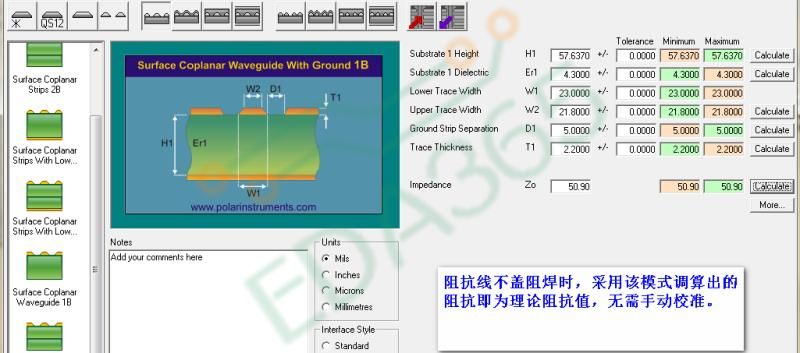

网友5:用这种模型就可以了。

网友3:线宽要23吗?W1怎么设置?

网友5:这个根据实际情况设置。

网友3:不是底面铺地吗?

网友4:标准线宽减0.6mil。

网友5:底面的地实际计算的时候影响不大,我是这么用的,要问问群里的大神老师们,不知道对不对。

提问者:线路厚度你取的1.2是不加镀铜的厚度,加了镀铜会厚一些,有些说法说要加镀铜厚度,不知道是不是?

网友5:根据实际需要可以设置,POLAR右边那些参数要找线路板厂要。距离厚度线宽等等,调整到50欧姆,调到合适你的要求。

网友4:

网友5:最终还是要仪器测试一下保证一致性。

网友4:是的!设计端给出理论设计参数,生产制程通过加工工艺实现阻抗要求,最终出货前进行仪器检测、提供检验报告。

何老师:群里也潜伏高手啊!提供的带地平面的共面波导模型,就是解决双面板厚介质的阻抗控制。我在EDA365公开课(4月13日)上也讲过。

04

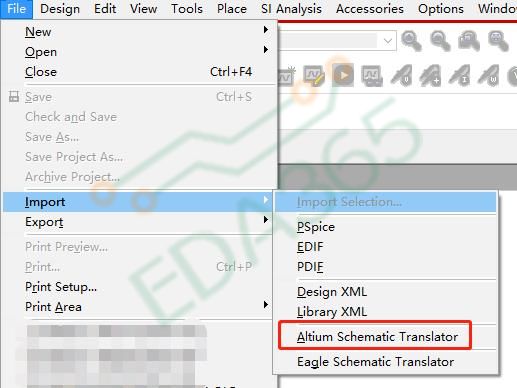

各位大师,请教个问题:AD软件的原理图怎么到cadence 的capture里面编辑?

网友1:在AD里直接编辑就是了,最后倒出来网表就行了。我记得还有版本限制,只能导成低版本的orcad,所以直接导网表最省事,没版本限制。

提问者:想要用AD里面的封装去设计新的图纸,导网表不够用。

网友2:capture里面有AD转换器,需要AD的prj文件,只要在AD里面将SchDoc文件,.PcbDoc文件另存为ASCII码文件,然后保存编译文件*.rjPCBStructure,和工程文件*.PrjPCB,最后在capture里面导入工程文件就好了。

你用的哪个版本capture?

提问者:16.6的cadence。

网友2:16.6是可以的,好像再低版本就不行了。

网友3:orcad和pads能直接映射吗?

网友2:PADS Logic原理图可以通过EDIF格式的原理图数据,直接导入Cadence Design Entry CIS原理图环境中16.6和以上版本是可以的,低版本不知道。

提问者:我试试看,非常感谢。

网友4:具体怎么操作,可否指教下?

网友5:两条差分线的间距在哪里设置啊?

网友4:是不是说这样PADS LOGIC就可以转成orcad。

贾老师:这份资料给到大家,可以读读看,很多问题便可以迎难而解。(公众号首页回复“贾老师”即可获取!)

网友4:我以前在ti官网下到原理图就是这样操作的,成功过,但是AD或PADS的原理可以这样转成orcad吗?有没有试过。

网友2:AD是肯定可以的,我转过,原理图pcb都可以,PADS只是看了教程,因为还没有pads软件最近也用不到,所以没试过。

-

keil5为什么下载不了程序?2024-07-11 1100

-

EMC测试过不了,怎么办? 有没有什么办法?2014-01-06 15300

-

变频空调EMC传导过不了,初步确定是开关电源的干扰2015-02-02 13873

-

单片机串口怎么搞?2015-03-27 2321

-

QuartusII里面NEW没有tcl script file怎么搞?2015-10-31 5885

-

这个OPC怎么搞 有没有资源和教程2018-06-04 2620

-

车灯传导在30-108M的过不了,哪位高手指点一下2018-11-17 3081

-

辐射过不了,请问哪里出问题了?2019-09-27 1838

-

这个双机全双工串口通信怎么搞2020-11-27 7418

-

开关电源EMC过不了的主要原因解析2018-05-25 24698

-

我国5G电磁辐射在安全范围内不要担心基站辐射过大的问题2019-08-16 3525

-

智能制造怎么搞?智能制造有4个关键环节2019-09-10 8958

-

硬件电路设计有这么多坑,如何少走弯路?看大牛怎么说2023-11-27 1427

-

emc辐射发射和传导发射测试区别 emc传导测试过不了的原因2024-10-06 8336

全部0条评论

快来发表一下你的评论吧 !