研发投入越来越高 什么样的工具才能保障变现?

描述

就嵌入式系统和SOC而言,汽车、大规模计算、IoT和5G通信等应用使得多核异构、多处理架构的设计成为主流。在无人驾驶、AI和ML这些领域,多核异构芯片正变得越来越普遍,而在数据中心这类应用场景中,有数千个处理器——随着功能迭代,这个数量将达到百万兆级——在同时运行,这些不同的处理器之间的交互对系统级行为产生的影响需要有效的跟踪和调试。

此外,RSIC-V这样的新型处理器架构的兴起也给SOC设计增加了一个前所未有的选项,芯片系统复杂度的增加使得芯片设计的投入越来越高——一颗7nm芯片从设计到流片需要2亿美金——因而保障它们被正确的设计和运行最终得以变现的工具就愈发重要。

大规模系统设计要解决的问题

SoC中多个硬件模块、固件和软件之间的复杂交互已经使实时的全生命周期监测成为SoC设计人员不可或缺的工具。设计方法的改变也正在使整个系统的监测比以往任何时候都更有必要。灵活的软件开发和特殊编程实践本质上都需要实际系统的高细节可见性。同样,系统硬件和软件的构建过程需要工程师清楚地了解其系统运行时的行为。

“芯片设计人员总是希望能够更快的进行系统级芯片开发和调试,系统设计则需要增强的连接能力,基于硬件的安全防护能力,功能安全性,现场性能和功耗优化,”UltraSoC首席执行官Rupert Baines说。“与Synopsys这类设计工具公司提供的产品不同,UltraSoC的产品是以IP的方式固化在用户芯片中,这对于用户而言,分析和调试不仅是研发期,而且延长到了整个产品生命周期。”UltraSoC是一家为SoC设计提供内部分析、追踪与监测IP的公司,这些IP将可扩展的分析技术和通信架构加入SoC中,包括开发、分析和数据可视化的算法及工具,以及用于信息安全的分析技术。

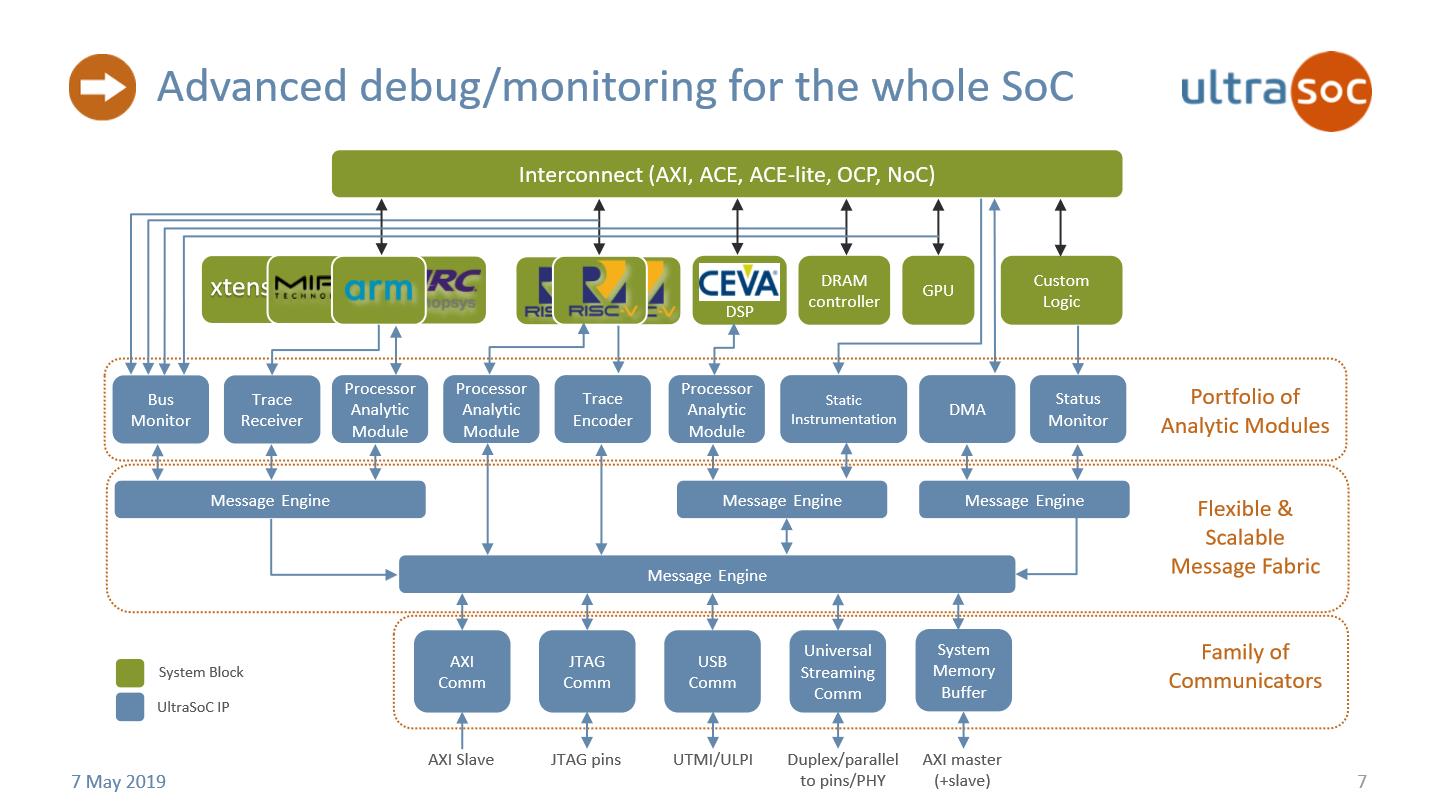

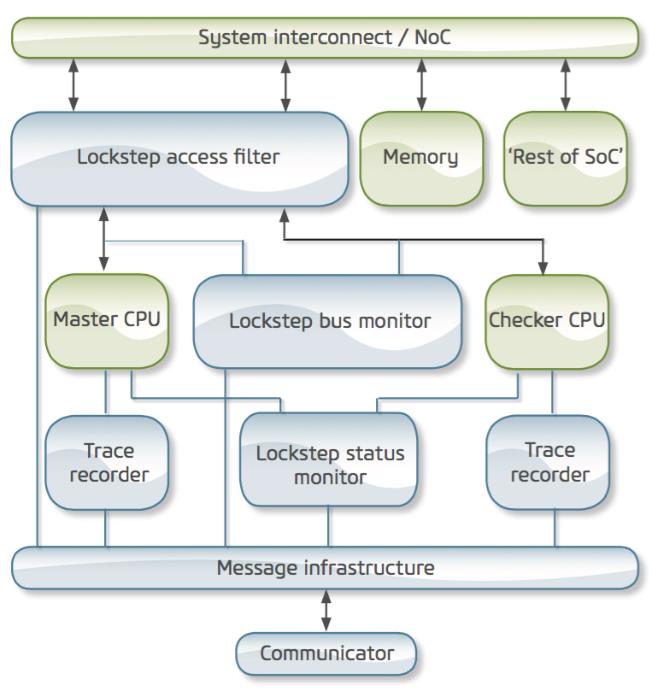

图:UltraSoC为SOC提供的调试和监测工具,支持ARM、MIPS、RISC-V等多种CPU架构

开发环境需要简化

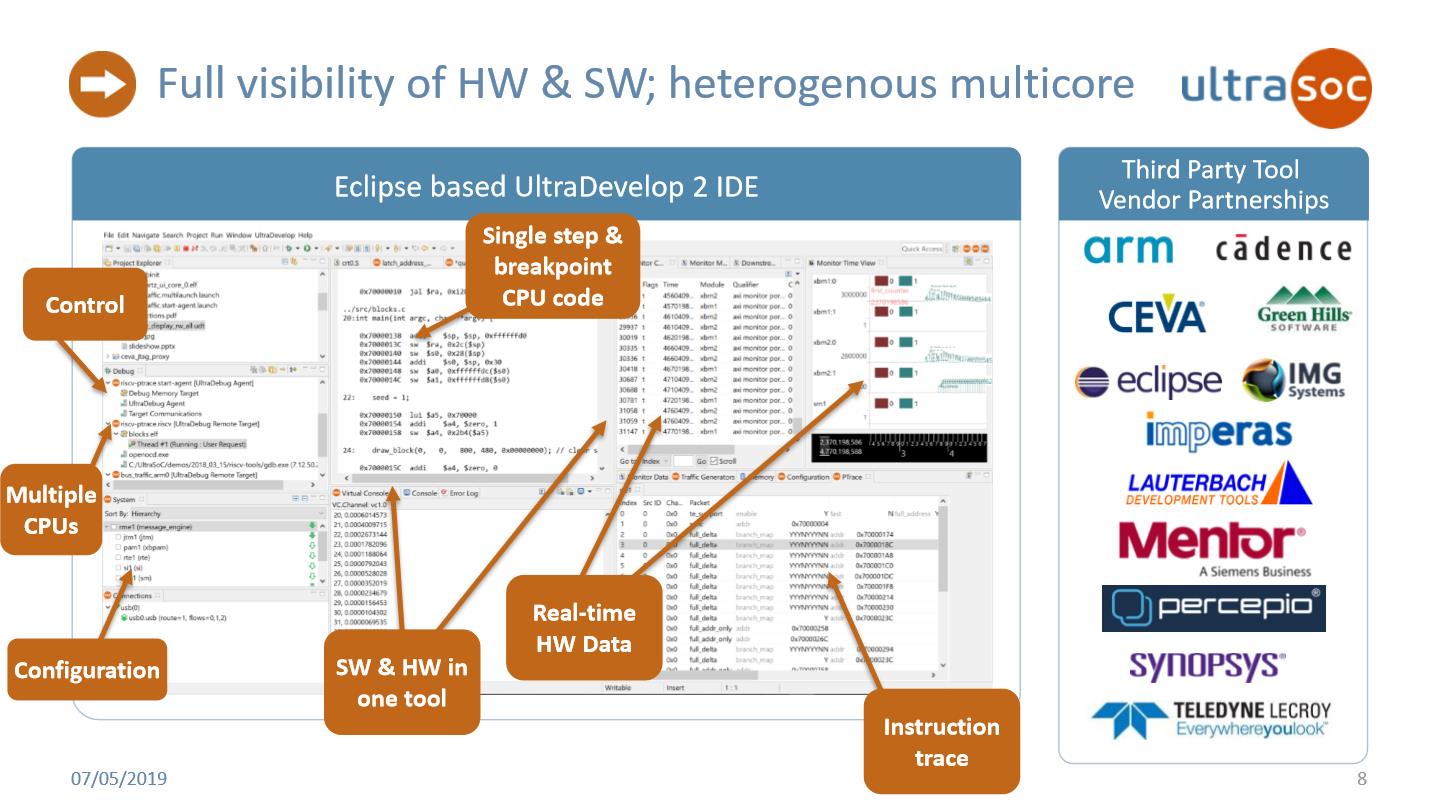

UltraSoC去年10月推出了一个集成开发环境工具——UltraDevelop 2 IDE。该工具集成了调试、运行控制和性能调优功能,可为硬件、固件和软件的运行提供集成化的视图,以及高级异常检测、可视化和数据科学等功能。

图:UltraDevelop 2 IDE可为硬件、固件和软件的运行提供集成化的视图界面

基于Percepio的Tracealyzer功能,UltraDevelop 2为工程师提供了硬件操作和高级软件执行的集成化可视性。对Imperas的多处理器调试器的集成,使UltraDevelop 2能够支持多核、多线程平台,包括利用不同处理器架构的内核组合,支持开发复杂的异构系统——如上所言,这些系统正变得越来越普遍。“打造UltraDevelop 2的目的,是为了给SoC设计人员在选择开发平台时提供功能和灵活性的最佳组合,并且有能力对20多种CPU架构进行实时运行控制。”Baines说,“开发人员可以从UltraSoC现有的合作伙伴处获得和部署第三方工具,并支持底层的UltraSoC硬件功能,或者他们可以选择UltraSoC提供的预集成配置。”

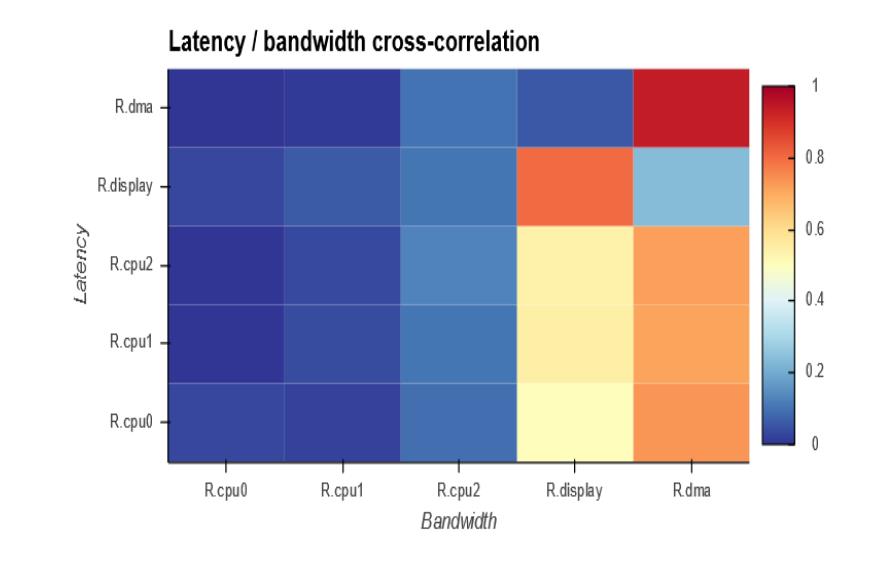

图:AI处理器的数据处理量达到3Gbit/S,要对延时和带宽进行分析,UltraDevelop 2通过自有数据库比对过滤掉无效的数据,提高分析效率

UltraDevelop 2的系统级整体开发方法意味着开发人员能够在任何抽象级别上查看和分析软件和硬件之间的交互。据悉,Microsemi不久前推出的PolarFire SoC架构所强调的“广泛的调试能力”正是受益于此,该架构属于其RISC-V Mi-V生态系统。

RISC-V的特殊需求

作为一个快速增长的开源处理器,RISC-V用户的增长迅速。据悉,目前UltraSoC的客户中,已有一半来自RISC-V,包括Andes, Esperanto, Lauterbach, Microchip和SiFive。“Esperanto的高性能计算系统在同一颗芯片上放置了一千个RISC-V处理器和AI/ML加速器,Western Digital则承诺将其存储处理器中的10亿个核心转换为RISC-V架构(SweRV Core处理器),”Baines说道。

和ARM等其他处理器已内置自有的ETM(嵌入式跟踪宏单元)不同,RISC-V没有ETM,所以,该公司在2018年初推出了业界第一款也是唯一一款专为RISC-V设计的商用追踪编码器IP,对指令执行和数据内存访问进行编码,并输出一种高度压缩的追踪格式,外部软件可以随后获取此数据并使用它来重建程序执行流程。其他通用功能则包括数据和指令追踪、一系列计数器和定时器以及快速分析描绘工具。

硬件防护的安全性会更高

从安全的角度讲,分析工具最好是独立于主系统,且是非侵入式的。“硬件防护分析速度更快,而且不会被恶意软件发现,”Baines说,“同时,也要满足结果实时可见并能够运行软件进行调整。UltraDevelop 2集成了诸如异常检测和防止恶意入侵等硬件支持的安全性与安全防护特性。”

这一硬件防护功能是基于UltraSoC的裸金属安全防护(Bare Metal Security,BMS)技术,该技术提供“比操作系统更底层”的、基于硬件的安全防护级别,对于攻击者,BMS极难被发现或被破坏。

除了越来越多的使用高级硬件和软件与物理世界交互使得系统对安保要求越来越高,行业标准的激增也需要对SOC的内部行为进行高粒度的监控,且不仅是开发期间,还要能够在部署后进行分析调试。以汽车网络安全标准SAE J3061为例,该标准要求在从开发到现场使用的整个产品生命周期中监测和控制安全保护功能,包括能够去监测事故和侵入系统的企图并报告此类事件。另外,类似画面冻结误导系统判断的情况也需要能够提出预警或辅助处理系统进行决策。这就要求分析工具可在已部署的产品里发现系统性和随机性错误,实现新级别的安全性和安全防护功能,并支持现场系统健康监测和高级取证。

“UltraDevelop 2的基础架构也包括专门针对提高汽车安全性与安全防护能力而优化的功能,”Baines说,“包括用于检查冗余模块之间一致性的锁步监测器。”虽然大多数处理器都有锁步功能,但在多处理架构系统中,第三方锁步功能会更客观。

据悉,UltraSoC去年11月和一家专精于设计和验证高完整性关键系统技术的公司ResilTech达成一项合作计划,旨在针对ISO26262标准进一步提高汽车系统的功能安全合规性。

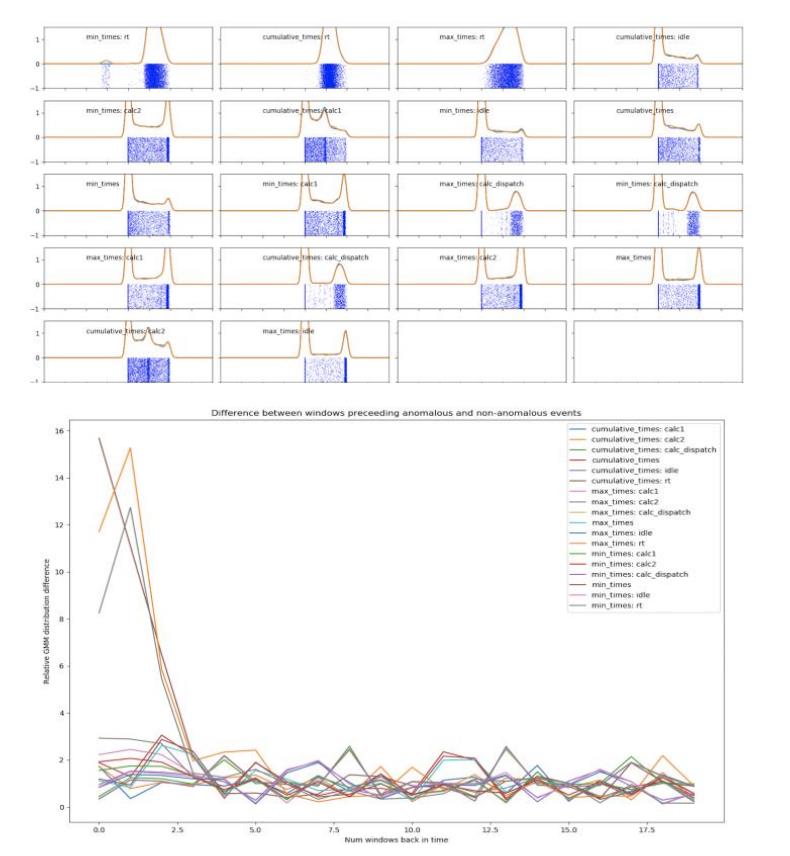

图:锁步功能监测可防止处理器出现异步频率的故障

周期精确追踪的重要性

在实时和性能关键型(performance-critical)应用中,周期精确追踪正变得越来越重要,工程师需要将其硬件和软件代码的运行优化到单时钟周期的水平,即被CPU、GPU、DSP或加速器所识别的最小时间单位。

UltraSoC不久前在其UltraDevelop 2 IDE中增加了周期精确的追踪功能——RISC-V Trace Encoder追踪编码器,支持32位和64位RISC-V设计。该技术最初将作为UltraSoC用于RISC-V处理器追踪解决方案的一部分提供。

Baines强调,当前处理器跟踪解决方案只跟踪程序流,如跳转、分支、中断等。但不能直接看到CPU在特定时刻所做的工作,周期精确跟踪解决了这个问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

原边反馈电源管理芯片是什么样的,它有什么优点?2017-06-12 4186

-

串联谐振的整体实用性越来越强2019-06-06 2015

-

为什么Web前端工程师薪资越来越高?2020-06-18 2085

-

单片机在以后会越来越趋向于低端化应用吗?2023-10-24 583

-

LED展望:光效越来越高 价格越来越低2010-01-07 903

-

ADAS比重越来越高 汽车电子或成半导体增长重要动能2016-10-25 665

-

什么样的编程方式才适合产品生产?2019-05-11 930

-

未来芯片的发展对FPGA的要求将会越来越高2019-09-11 1173

-

新能源汽车在市场的普及度越来越高2019-09-27 1272

-

传感器的地位为什么越来越高2019-11-11 2614

-

中国芯呼声越来越高,国内EDA龙头华大九天新突破2020-09-23 6883

-

越来越高的带宽需求要怎样的通信卫星来配合2020-11-26 895

-

为何车载连接器的阻燃性要求越来越高?2021-05-31 2557

-

AI技术成熟度越来越高,NPU大时代来临2023-01-30 1784

-

为何开关频率要大于30kHz,且有越来越高的趋势?2024-01-31 8696

全部0条评论

快来发表一下你的评论吧 !