根据要求设计MOS驱动电路

描述

现在的MOS驱动,有几个特别的需求

1低压应用

当使用5V电源,这时候如果使用传统的图腾柱结构,由于三极管的be有0.7V左右的压降,导致实际最终加在gate上的电压只有4.3V。这时候,我们选用标称gate电压4.5V的MOS管就存在一定的风险。

同样的问题也发生在使用3V或者其他低压电源的场合。

2宽电压应用输入电压并不是一个固定值,它会随着时间或者其他因素而变动。这个变动导致PWM电路提供给MOS管的驱动电压是不稳定的。

为了让MOS管在高gate电压下安全,很多MOS管内置了稳压管强行限制gate电压的幅值。在这种情况下,当提供的驱动电压超过稳压管的电压,就会引起较大的静态功耗。

同时,如果简单的用电阻分压的原理降低gate电压,就会出现输入电压比较高的时候,MOS管工作良好,而输入电压降低的时候gate电压不足,引起导通不够彻底,从而增加功耗。

3双电压应用在一些控制电路中,逻辑部分使用典型的5V或者3.3V数字电压,而功率部分使用12V甚至更高的电压。两个电压采用共地方式连接。

这就提出一个要求,需要使用一个电路,让低压侧能够有效的控制高压侧的MOS管,同时高压侧的MOS管也同样会面对1和2中提到的问题。

在这三种情况下,图腾柱结构无法满足输出要求,而很多现成的MOS驱动IC,似乎也没有包含gate电压限制的结构。

于是我设计了一个相对通用的电路来满足这三种需求。

针对NMOS驱动电路做一个简单分析:

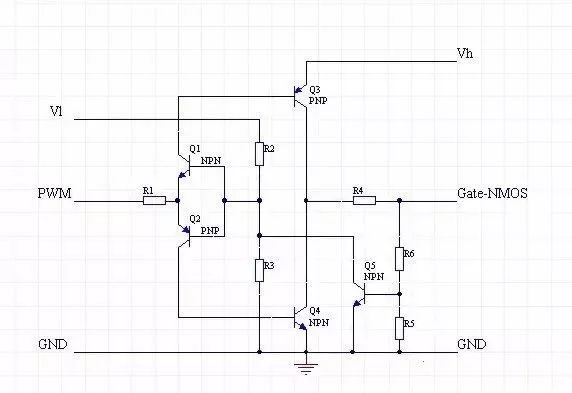

Vl和Vh分别是低端和高端的电源,两个电压可以是相同的,但是Vl不应该超过Vh。Q1和Q2组成了一个反置的图腾柱,用来实现隔离,同时确保两只驱动管Q3和Q4不会同时导通。

R2和R3提供了PWM电压基准,通过改变这个基准,可以让电路工作在PWM信号波形比较陡直的位置。

Q3和Q4用来提供驱动电流,由于导通的时候,Q3和Q4相对Vh和GND最低都只有一个Vce的压降,这个压降通常只有0.3V左右,大大低于0.7V的Vce。R5和R6是反馈电阻,用于对gate电压进行采样,采样后的电压通过Q5对Q1和Q2的基极产生一个强烈的负反馈,从而把gate电压限制在一个有限的数值。这个数值可以通过R5和R6来调节。

最后,R1提供了对Q3和Q4的基极电流限制,R4提供了对MOS管的gate电流限制,也就是Q3和Q4的Ice的限制。必要的时候可以在R4上面并联加速电容。

这个电路提供了如下的特性:

1用低端电压和PWM驱动高端MOS管。

2用小幅度的PWM信号驱动高gate电压需求的MOS管。

3gate电压的峰值限制

4输入和输出的电流限制

5通过使用合适的电阻,可以达到很低的功耗。

6PWM信号反相。NMOS并不需要这个特性,可以通过前置一个反相器来解决。

-

MOS管驱动电路原理与MOS管驱动电路布线设计2022-12-30 9112

-

MOS管驱动电路的基础总结2017-08-01 33043

-

单片机驱动mos管电路图2022-11-25 10095

-

设计开关电源时,mos管驱动电路参数、要求2022-12-12 11023

-

MOS管驱动电路原理图2023-06-08 39445

-

高压浮动MOS栅极驱动集成电路(应用手册)2010-01-04 1223

-

高速MOS驱动电路设计和应用指南2016-06-22 1294

-

MOS管驱动电路_单片机如何驱动MOS管2020-06-26 83553

-

mos管高端驱动电路 高手才可以搞定的mos管调压电路2020-12-30 27428

-

常用MOS管驱动电路分享2022-07-10 6094

-

MOS驱动的几种电路2022-09-06 4242

-

MOS管常用的驱动电路分享2023-01-26 3274

-

如何根据IGBT的驱动要求设计过流保护2023-11-14 451

-

如何根据电路需求选择合适的MOS管?2025-02-24 954

-

推挽电路驱动多个mos2025-06-18 2148

全部0条评论

快来发表一下你的评论吧 !