三星3nm工艺创新采用‘GAAFET结构’ 芯片面积减少45%

三星3nm工艺创新采用‘GAAFET结构’ 芯片面积减少45%

电子说

1.4w人已加入

描述

韩国三星电子于15日宣布在“Samsung Foundry Forum 2019 USA”上发布工艺设计套件(PDK)0.1版3nm Gate-All-Around(GAA)工艺“3GAE”。

与7 nm工艺相比,3GAE可将芯片面积减少高达45%,降低50%的功耗或实现35%的性能提升。基于GAA的过程节点有望用于下一代应用,如移动,网络,汽车,AI和物联网。

3GAE的特点是采用GAA的专利变体“MBCFET(多桥通道FET)”而不是传统的GAA,该公司已经完成了测试车辆设计,并将专注于提高其性能和功率效率。

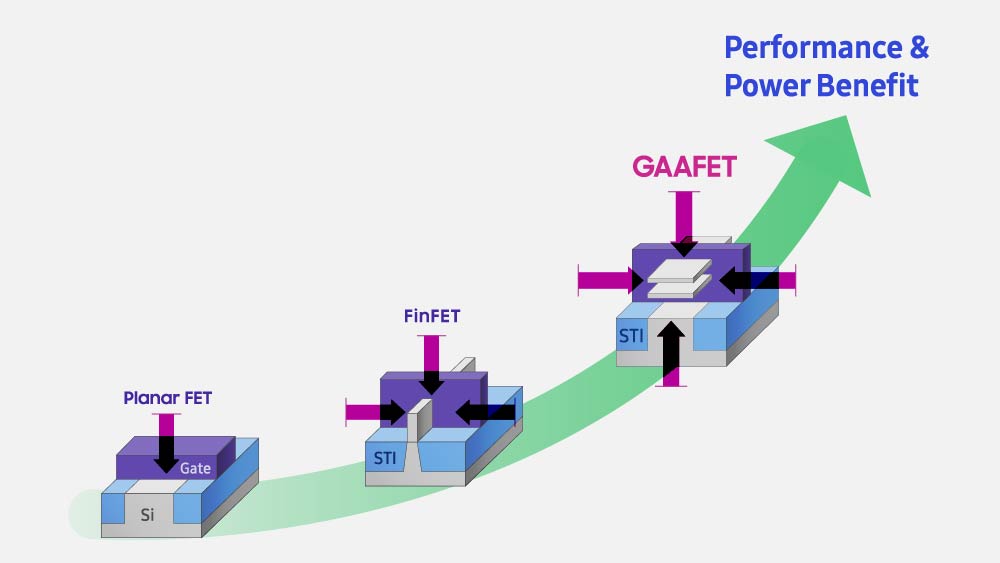

图:晶体管结构的转变

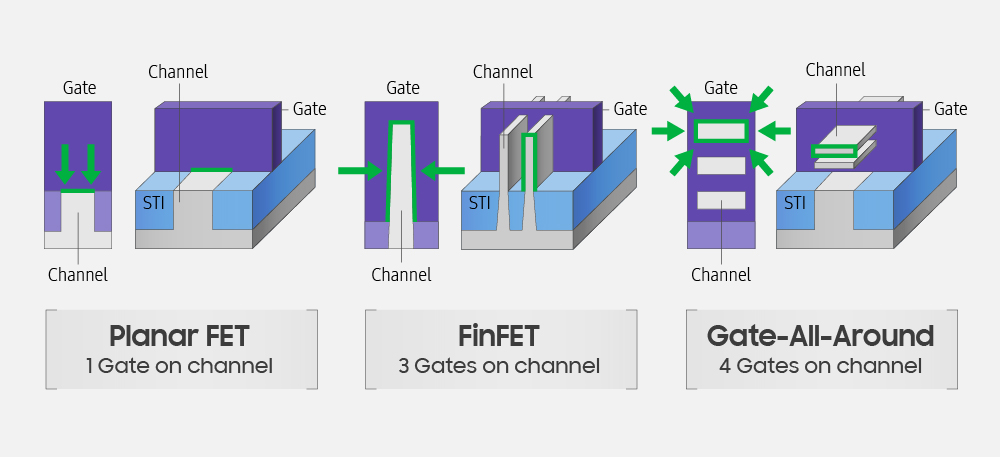

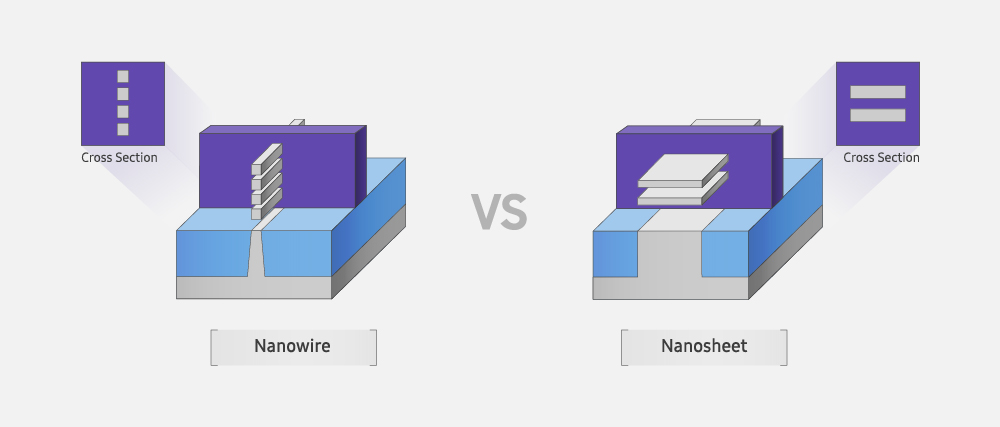

在传统的GAA中,由于沟道是nm线的形式,因为沟道薄且小,所以难以传递更多的电流,并且必须设计诸如增加堆叠数量的措施。它使用通道结构来排列nm片,增加了栅极和沟道之间的接触面积,并实现了电流的增加。

该公司声称它将彻底改变半导体行业,其中MBC FET已经小于4nm,并为第四次工业革命提供核心技术。

图:结构

根据该公司发布的工艺路线图,将使用极紫外(EUV)曝光技术制造4个7nm至4nm的FinFET工艺,然后使用EUV制造3nm GAA和MBCFET。而目前他们已经做到了!

该公司将在2019年下半年开始批量生产6nm工艺器件,同时完成4nm工艺的开发。5nm FinFET工艺的产品设计于2019年4月开发,也将于2019年下半年完成,并将于2020年上半年开始量产。开发28FDS,18FDS,1Gb容量的eMRAM也计划于2019年完成。

图:传统的GAA和MBCFET

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

三星3nm GAA正式商业量产2023-07-21 2619

-

陷入风波的先进工艺2022-09-26 1828

-

三星在3nm率先使用GAA 是否更具竞争力2022-08-18 2427

-

三星已找到第二家3nm芯片客户 产能开始供不应求2022-08-11 2120

-

三星即将公布首颗3nm芯片,或将扭转订单数量2022-07-25 2576

-

三星3nm芯片开始量产,采用GAA晶体管,提升巨大2022-06-30 3222

-

成功弯道超车!三星明天将开始量产3nm工艺,抢先台积电一步占领市场2022-06-29 2011

-

揭秘3nm GAE MBCFET 芯片的制造细节2021-03-15 5364

-

三星3nm工艺投产延迟,新技术让芯片功耗下降约50%2020-04-08 3418

-

三星3nm工艺明年量产不太可能实现2020-04-07 2808

-

台积电将会为3nm工艺技术选择什么线路2020-02-06 1871

-

三星发布新一代3nm闸极全环工艺 在GAA工艺上获得领先地位2019-05-30 4542

-

三星发布3nm节点工艺!GAAFET!2019-05-17 12449

-

三星宣布:DRAM工艺可达10nm2015-12-14 3196

全部0条评论

快来发表一下你的评论吧 !