PCI_MT64 IP核的原理和结构设计

描述

引言

随着CompactPCI在中国大范围的普及和使用,越来越多的企业开始研制基于CompactPCI接口的产品,市场上有一些专用PCI接口芯片。FPGA(现场可编程门阵列)技术的快速发展使得万门以上乃至几十万门逻辑阵列的使用越来越普遍。与专用PCI接口芯片相似,很多FPGA制造商都提供了PCI接口核逻辑。设计者可以将PCI用户逻辑与PCI Core集成在一片FPGA里,并且可以在顶层通过仿真来验证PCI接口以及用户逻辑设计的正确与否,这样可以大幅度提高调试速度、缩短开发周期、提高电路板的集成度和系统的性能。目前,开发者最常用的两种PCI IP核是ALTERA公司的PCI MEGACORE和XILINX公司的PCI Logicore。本文所介绍的PCI_MT64 IP核是ALTERA公司开发的一个功能强大的CPCI接口内核,最高能实现64位的数据宽度和66MHz的工作频率。文章介绍了PCI_MT64的工作原理以及此IP核在CPCI总线数据采集卡的应用设计,并通过本地逻辑设计测试了此IP核的功能。

PCI_MT64 IP核的原理和结构

根据用户性质的不同,CPCI接口类型分为两种:MASTER(主设备) 和TARGET(从设备)。ALTERA公司据此开发了多种 PCI IP核:PCI_MT64、PCI_MT32、PCI_T64和PCI_T32。由于设计需要完成66MHz、64位宽度数据传输,且在主模式下DMA控制器才能工作,因此选择了PCI_MT64。

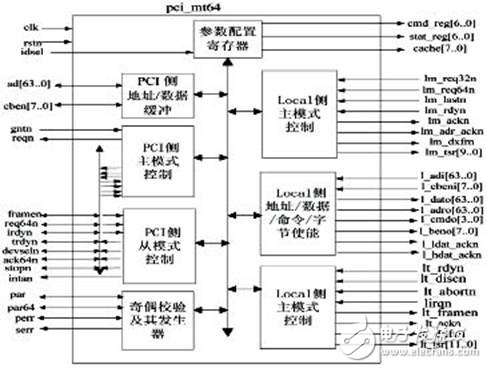

PCI_MT64是支持33/66MHz工作频率、64位PCI总线、支持主/从模式的PCI IP功能模块。当其宽度为64位、系统时钟为66 MHz时,峰值传输速率为528 MB/s。其主要由8个模块组成,如图1所示。

图1 PCI_MT64的模块结构

参数配置寄存器:提供参数确定的寄存器,包括设备识别、供应商识别、分类代码、修订版本、基址寄存器和子系统供应商等信息。在设计中,ALTERA公司提供了参数化的图形界面,用户只需按PCI协议输入或选择合理的值即可完成该寄存器的配置。

PCI侧地址/数据缓冲模块:用来缓存PCI总线侧的地址数据输入、输出信号。

PCI侧主/从模式控制模块:用于控制PCI总线的主设备和从设备的各种时序操作。

Local侧主/从模式控制模块:用于控制PCI_MT64与本地逻辑的各种操作。

Local侧地址/数据/命令/字节使能模块:接收和输出用户侧的所有地址、数据、命令、字节使能等信号。

奇偶校验模块:用于对数据、地址、命令进行奇偶校验。

PCI_MT64 IP核在CPCI数据采集卡中的应用设计

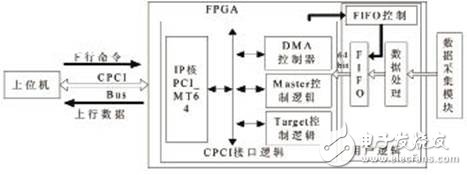

PCI_MT64 IP核在CPCI数据采集卡中的功能:与CPCI总线之间的通信和数据传输,并做奇偶校验以保证正确性,即将复杂的CPCI总线信号转换为相对简单易操作的CPCI本地总线信号,它从CPCI总线侧获得传输命令和读写数据的地址后,一方面对这个操作命令做出反应,将其传达给本地逻辑,另一方面将CPCI总线传送过来的数据地址映射为本地逻辑可识别的地址。当本地端总线准备好后,PCI IP核会收到本地逻辑做出的响应信号,然后根据主从模式,读/写命令的不同执行相应的时序。简单的说,它是CPCI总线和本地逻辑的桥梁,所以首先要设计CPCI本地侧逻辑实现PCI IP核功能验证,如图2所示。

图2 CPCI本地端逻辑设计

以上设计能快速评估PCI IP核的功能,当PCI_MT64作为一个主设备,主模式控制逻辑连接DMA控制器来完成一次PCI主模式读写传输。当PCI_MT64作为一个从设备,它触发从模式控制逻辑来执行一次从模式传输。CPCI数据采集卡使用DMA方式上传数据,即将数据采集模块的数据处理后,缓存到FIFO,从FIFO中传输数据到上位机;使用从模式写传输发送控制命令到板卡不同寄存器。当进行一次从模式传输时,PCI IP核不能启动总线操作,只能依赖于主设备从其中读取数据或向其传送数据,相关设计较为简单,而DMA模式是PCI_MT64配合自主设计的DMA控制器来实现的,所以DMA控制器是整个设计的关键。

DMA控制器由DMA寄存器和DMA状态机两个模块构成。DMA寄存器是主机控制DMA的窗口,包括控制状态寄存器、地址寄存器、字节寄存器、中断状态寄存器和本地地址寄存器。DMA寄存器的地址直接映射到PCI的地址空间,其基地址对应PCI IP核中的配置寄存器Bar0。主机通过设置在存储器地址空间的DMA寄存器来控制DMA传输。DMA状态机是控制主模式写传输的核心,产生主模式传输需求的各种信号。状态跳转条件来自DMA寄存器,IP核以及DMA FIFO。状态机流程图如图3所示。

图3 DMA状态机

以链式DMA传输为例介绍其流程:主机首先把多组字节寄存器和地址寄存器的值写入描述符FIFO,每一组字节寄存器和地址寄存器就是一个描述符;主机再写本地地址寄存器和控制状态寄存器即启动了DMA状态机,开始链式的数据传输。状态机跳入装载DMA状态,通过对DMA FIFO的读取将需要的值写入寄存器中,经寄存器有效状态进入等待请求状态。当外部FIFO数据准备好,DMA状态机向主机发送总线请求信号,并等待主机的总线允许信号,此时状态机进入等待允许状态;一旦接收到主机的总线允许信号,整个DMA传输开始,状态机也进入数据传输状态。在数据传输周期中,字节寄存器的值逐渐减少直到零时,一个描述符传输完成,每一个描述符传输完成的时候,状态机并不进入结束状态,而是直接进入空闲状态,开始下一次描述符的传输,所以不产生中断。等到DMA FIFO为空的时候,状态机认为本次链式DMA传输完成,进入到结束状态,此时产生中断,一次链式DMA传输结束。

实验调试及分析

PCI_MT64 IP核在CPCI数据采集卡中的应用主要是完成数据的高速传输,包括从模式写传输方式的数据下传(控制命令)和DMA方式的数据上传(采集卡数据)。在QuartusII9.0环境下,运用Megacore PCI Complier对PCI_MT64进行设置,并对CPCI本地端逻辑进行了综合编译,生成网表文件,运用Testbench工具对从模式写传输方式进行仿真,验证了PCI_MT64 IP核的稳定性。其时序仿真如图4所示。

图4 从模式单周期写仿真时序

图4中是一个对地址为8000H的MEM域空间的单周期写操作,在第3个时钟周期,FRAME#低电平有效,此时pci_ad的值是8000H,pci_cben的值是0111B,表示存储器写,在TRDY#和IRDY#同时有效的时候,数据由pci_ad传给l_dato,这里写入的数据是66666666H。由仿真图可以看到,pci_ad和l_dato的数据是一样的,所以从模式单周期写传输正确。单周期读写适合少量数据传输,不同寄存器控制命令的发送及DMA寄存器的设置都是通过从模式下单周期读写实现的。

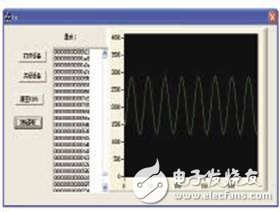

为测试PCI_MT64 IP核的本地端逻辑设计,调用基于Windriver编写的驱动程序和用户界面实现数据的传输。这样,既验证了CPCI数据采集卡硬件逻辑的正确性,又验证了软件的正确性。其测试结果如图5所示。

图5 应用软件测试界面

图5中数据采样率为500MHz,输入信号频率为16MHz,一个周期的采样点数N=500/16=31.25,故250个点内应有250/31.25=8个周期的数据。采样数据的幅值以十六进制格式在列表框中显示。波形显示了有限数据的连续传输,没有任何数据丢失,验证了基于PCI_MT64 IP核在数据采集卡中采用DMA方式传输数据的完整性及传输速度。

结束语

PCI_MT64 IP核能有效的满足CPCI数据采集卡对数据高速传输的要求,实现CPCI接口功能,并能与用户逻辑配合工作,实现数据的缓存和传输。相较于使用PCI专用芯片实现接口功能的方法,本设计具有电路板集成性能高、功耗低、成本低、方便移植等优点。

电子科技大学自动化工程学院 王俊丽 王志刚

-

娄贵鑫

2019-10-09

0 回复 举报正在学习这个,感谢分享 收起回复

娄贵鑫

2019-10-09

0 回复 举报正在学习这个,感谢分享 收起回复

-

变压器结构设计手册2008-12-13 5828

-

操作系统结构设计2011-09-13 2576

-

手机结构设计心得2012-11-07 5231

-

一种基于PCI IP核的码流接收卡的设计2012-11-28 1655

-

招聘--结构设计师2015-09-25 3010

-

浅谈产品结构设计特点2016-02-25 6039

-

软件结构设计2016-09-26 2610

-

基于PCI IP核的码流接收卡的设计2018-12-07 1869

-

蝶式五轨滑盖结构设计与磁动力滑盖结构设计的不同之处在哪?2021-07-28 1893

-

结构设计方面资料2010-08-09 1175

-

轴系结构设计实验2009-03-13 59344

-

PCI Express IP核应用参考设计2016-06-07 849

-

轮辐转子的结构设计2017-01-02 821

-

浅谈产品结构设计类别及产品结构设计的重要性2021-05-26 21408

-

FPC的结构设计.zip2023-03-01 958

全部0条评论

快来发表一下你的评论吧 !