Achronix推出Speedster7tFPGA系列产品 简化设计FPGA灵活性

电子说

描述

随着人工智能、机器学习等应用场景快速发展演进,对芯片的算力、安全性等性能也提出了更高的诉求。

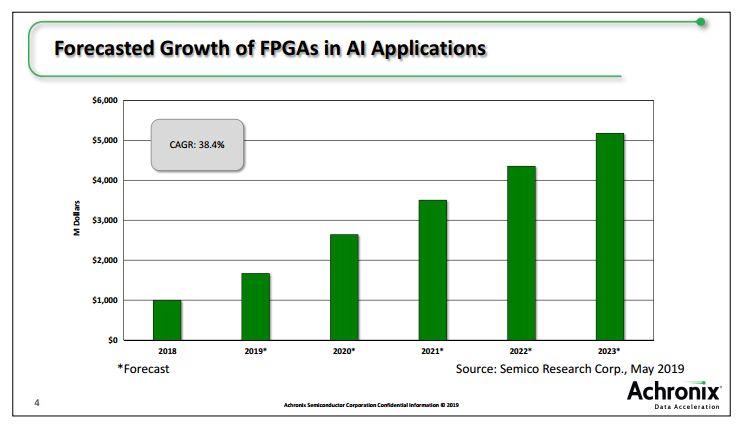

据市场调研公司Semico Research数据显示,2018年FPGA市值约为10亿美元,在未来4年内,人工智能应用中FPGA的市场规模将增长3倍,达到52亿美元。

要知道,这个增长是非常惊人的,毕竟过去多年,FPGA市场的年均增长率也才8%-9%。

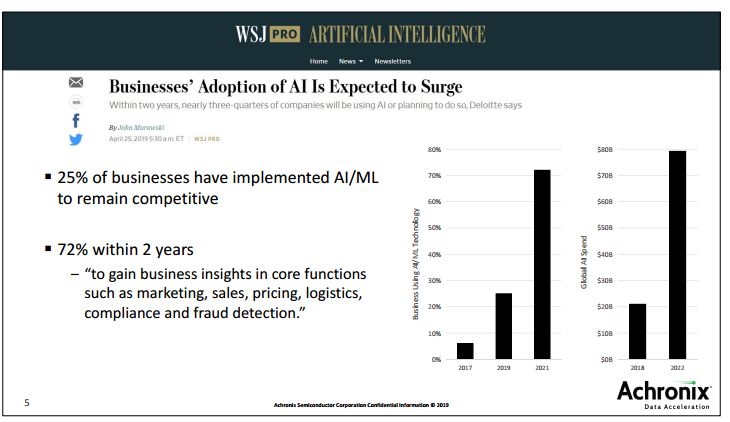

目前人工智能、机器学习等应用场景的FPGA市场约为25%,预计两年后将达到72%。如此庞大的市场空间,则需要性能更高、更加灵活的AI 算法解决方案。

近日,基于FPGA的硬件加速器件和高性能嵌入式FPGA(eFPGA)半导体知识产权(IP)领导性企业Achronix半导体公司推出了创新性的Speedster7t FPGA系列产品,以其具有ASIC一样的性能,还可简化设计的FPGA灵活性和增强功能,从而远远超越传统的FPGA解决方案。

为何要研发Speedster7t FPGA?

据了解,Speedster7t FPGA系列产品是专为高带宽应用进行设计,具有一个革命性的全新二维片上网络(2D NoC),以及一个高密度全新机器学习处理器(MLP)模块阵列。

该产品的诞生也极具有创新性和针对性,Achronix CEO 罗伯特·布莱克先生在接受芯师爷的采访时表示,在研发该芯片时,主要考虑三方面问题:

其一,如何拥有高效的计算力;

其二,如何将数据更快速、高效地传输到计算单元中;

其三,如何实现高效,丰富存储缓存能力。而这也是目前数据加速所需架构的三大要素。

Achronix CEO 罗伯特·布莱克

在演讲过程中,我们能完全感受到罗伯特·布莱克先生的兴奋。

他认为,Speedster7t是Achronix历史上最令人激动的发布,代表了建立在四个架构代系的硬件和软件开发基础上的创新和积淀,以及与我们领先客户之间的密切合作。

Speedster7t是灵活的FPGA技术与ASIC核心效率的融合,从而提供了一个全新的‘FPGA+’芯片品类,它们可以将高性能技术的极限大大提升。

“在开发Speedster7t系列FPGA的产品过程中,Achronix的工程团队完全重新构想了整个FPGA架构,以平衡片上处理、互连和外部输入输出接口(I/ O),以实现数据密集型应用吞吐量的最大化,这些应用场景可见于那些基于边缘和基于服务器的AI/ML应用、网络处理和存储。”罗伯特·布莱克先生补充道。

采用7nm制程工艺,集结五大优势

Speedster7t FPGA系列产品经历3年研发,将采用台积电7nm FinFET工艺,是专为接收来自多个高速来源的大量数据而设计。整体来看,该产品主要有五大优势:

1、较高的计算性能

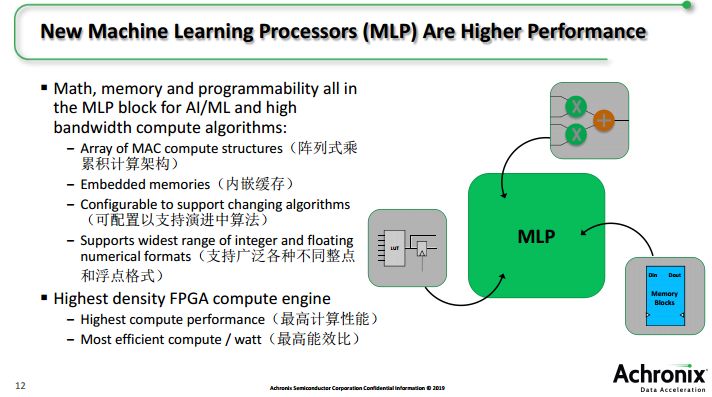

AI、ML需要矢量矩阵乘法,而传统的带DSP模块的FPGA性能有限,需要消耗额外逻辑和Memory资源,而新的MLP是高度可配置的、计算密集型的单元模块,可支持4到24位的整点格式和高效的浮点模式,包括对TensorFlow的16位格式的支持,以及可使每个MLP的计算引擎加倍的增压块浮点格式的直接支持。它可提供业界最高的、基于FPGA的计算密度。

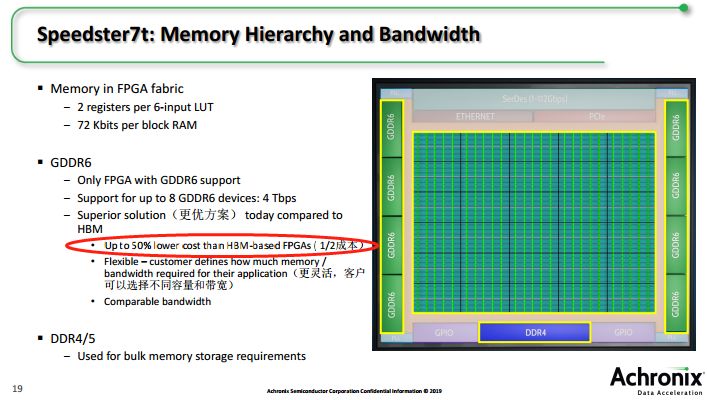

2、支持超高存储带宽

值得一提的是,Speedster7t器件是唯一支持GDDR6存储器的FPGA,该类存储器是具有最高带宽的外部存储器件。每个GDDR6存储控制器都能够支持512 Gbps的带宽,Speedster7t器件中有多达8个GDDR6控制器,可以支持4 Tbps的GDDR6累加带宽,并且以很小的成本就可提供与基于HBM的FPGA等效存储带宽。

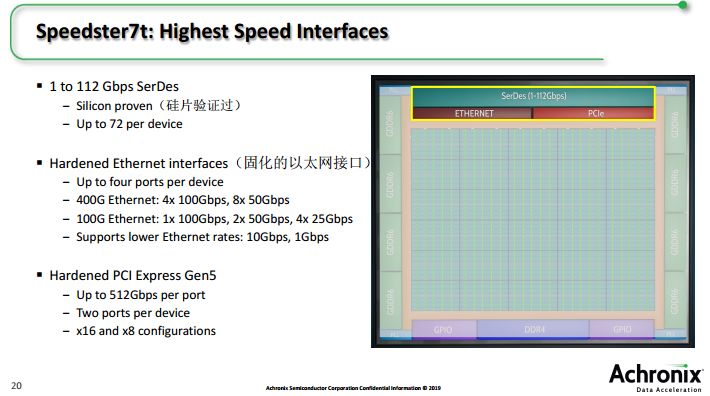

3、高速接口

除了这种超高的存储带宽,Speedster7t器件还包括业界最高性能的接口端口,以支持极高带宽的数据流。Speedster7t器件拥有多达72个业界最高性能的SerDes,可以达到1到112 Gbps的速度。还有带有前向纠错(FEC)的硬件400G以太网MAC,支持4x 100G和8x 50G的配置,以及每个控制器有8个或16个通道的硬件PCI Express Gen5控制器。

4、超高效率的数据移动

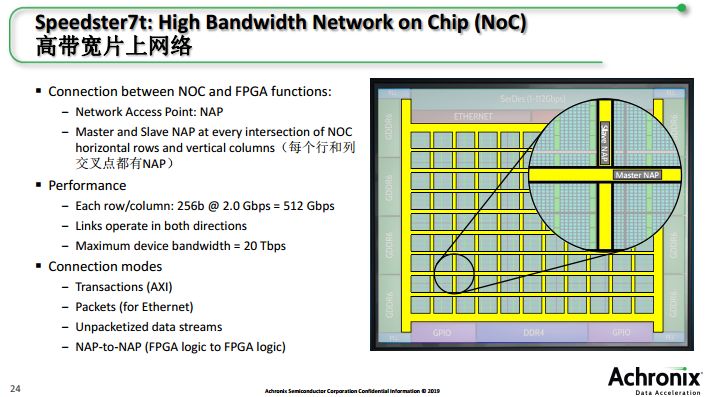

Speedster7t高速I/O和存储器端口的产生的数万兆比特数据很容易淹没传统FPGA面向比特位的可编程互连逻辑阵列的路由容量,而Speedster7t架构包含一个可横跨和垂直跨越FPGA逻辑阵列的创新性的、高带宽的二维片上网络(NOC),它们连接到所有FPGA的高速数据和存储器接口。

它们就像叠加在FPGA互连这个城市街道系统上的空中高速公路网络一样,Speedster7t的NoC支持片上处理引擎之间所需的高带宽通信。NoC中的每一行或每一列都可作为两个256位实现,单向的、行业标准的AXI通道,工作频率为2Ghz,同时可为每个方向提供512 Gbps的数据流量。

值得注意的是,NOC的外围(如下图的大黄框)是购买的IP,但是内部的构造是Achronix自己设计的。

通过在Speedster中实现专用二维NoC,极大地简化了高速数据移动,并确保数据流可以轻松地定向到整个FPGA结构中的任何自定义处理引擎。

最重要的是,NOC消除了传统FPGA使用可编程路由和逻辑查找表资源在整个FPGA中移动数据流中出现的拥塞和性能瓶颈。这种高性能网络不仅可以提高Speedster7t FPGA的总带宽容量,还可以在降低功耗的同时提高有效LUT容量。

5、高安全性

Speedster7t FPGA系列产品在面临第三方攻击的威胁时,可用最先进的比特流安全保护功能应对,它们具有的多层防御能力可保护比特流的保密性和完整性。

密钥是基于防篡改物理不可克隆技术(PUF)进行加密,比特流由256位的AES-GCM加密算法进行加密和验证。为了防止来自旁侧信道的攻击,比特流被分段,每个数据段使用单独导出的密钥,且解密硬件采用差分功率分析(DPA)计数器措施。

此外,2048位RSA公钥认证协议被用来激活解密和认证硬件。用户可以确信的是当他们加载其安全比特流时,它是预期的配置,这是因为它已通过RSA公钥、AES-GCM私钥和CRC校验进行了身份验证。

产品多样化,商业模式创新化

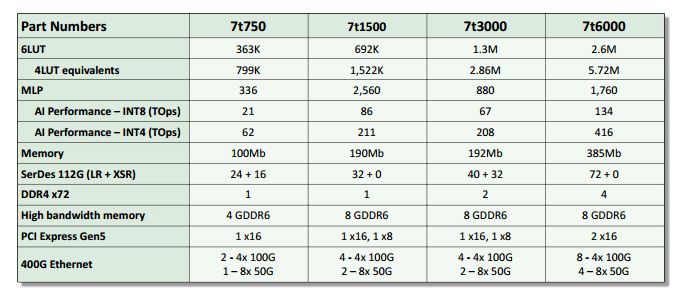

截至目前,针对不同的市场应用需求,Achronix 还推出了Speedster7t系列的“家族”化产品,如7t750、7t1500、7t3000、7t6000。

但该系列的产品还未正式上市,预计2019年第四季度会提供样片及加速卡,2020年正式量产。其中,Speedcore eFPGA基于台积电16FF +工艺产品已经实现量产。

为了更好的为公司硬件产品提供支持,Achronix专门推出了配套的ACE软件设计工具,该软件与业界标准的逻辑综合工具配合使用,支持FPGA设计人员便捷地将其设计映射到Speedster7t FPGA、Speedcore eFPGA和Speedchip FPGA chiplets产品中。值得一提的是,该ACE软件设计工具可直接获得。

据了解,Achronix是唯一一家既提供独立FPGA芯片又提供Speedcore嵌入式FPGA(eFPGA)半导体知识产权(IP)的公司。

Achronix在Speedcore eFPGA IP中采用了与Speedster7t FPGA中使用的同一种技术,可支持从Speedster7t FPGA到ASIC的无缝转换。

事实上,自2017年以来,Achronix便开始向客户提供Speedcore IP,它是唯一嵌入到大容量ASIC中的eFPGA技术。

在SoC中嵌入Speedcore IP技术将带来多项好处,与一款独立的FPGA芯片相比,Speedcore IP将提供高出10倍的带宽、低100倍的延迟、低10倍的成本、功耗降低50%等优点。

-

基于Achronix Speedster7t FPGA器件的AI基准测试2024-09-18 1773

-

FPGA为嵌入式设计带来了强大的功能与灵活性2023-12-07 1684

-

Achronix展示Speedster7t高性能接口 贸泽备货Molex电路板连接器2022-03-17 4528

-

开放式FPGA能否增加测试的灵活性?2021-05-11 1195

-

Achronix Speedster7t FPGA如何运用GDDR6满足网络产品的高带宽需求2020-02-17 2068

-

BittWare和Achronix合作推出采用7纳米的Speedster7t FPGA2019-11-19 1002

-

Achronix推全新7nm FPGA 首度支持GDDR6高带宽存储2019-06-10 1651

-

Achronix公司将推出专注AI机器学习和高带宽应用突破性FPGA的说明2019-06-09 1255

-

Achronix推出新7nm FPGA系列产品 无形给国内FPGA厂商施加了压力2019-05-23 1417

-

FPGA设计五大优势 凸显工业应用灵活性2015-10-28 18967

-

Altera设计坊第一期如何通过FPGA提高工业应用灵活性?2013-10-11 16354

-

功率和成本减半 Achronix交付先进22nm Speedster22i 系列FPGAs2013-03-04 4044

-

英特尔22nm 3D晶体管工艺,Achronix公布全新Speedster22i系列FPGA细节2012-04-25 1641

-

基于FPGA的网络处理技术的性能和灵活性分析2009-12-26 1145

全部0条评论

快来发表一下你的评论吧 !