基于FPGA的车电总线通信设计方案

接口/总线/驱动

描述

为提高集成架构中车电总线通信速率,结合综合化处理系统项目要求,采用双总线结合的方式,利用CAN总线和FlexRay总线实现功能及搭配上的互补,提出一种基于现场可编程门阵列(FPGA)的总线接口单元设计方案。通过FPGA完成CAN总线控制器、FlexRay总线控制器、RapidIO总线接口等模块功能,实现高速接口的控制和扩展,并使模块接口具备可配置能力。测试结果表明,CAN接口及FlexRay接口在指定的波特率下均工作正常,满足项目要求的各项性能指标。

1 概述

CAN总线是一种有效地支持分布式控制或者实时控制的串行通信网络,具有多主机、高性能以及高可靠性。然而随着汽车电子技术的发展,早期的CAN总线已经不能很好地解决众多电子设备之间的实时通信问题。由FlexRay联盟制定的FlexRay协议标准成为一种理想的解决方案。FlexRay通讯协议运用于可靠的车内网络中,是一种具备故障容错的高速汽车总线系统。作为一种灵活的车载网络系统,FlexRay具有高速、可靠及安全的特点,它不仅能简化车载通信系统的架构,而且有助于汽车电子单元获得更高的稳定性和可靠性。FlexRay在物理上通过2条分开的总线进行通信,每一条的数据速率是10 Mb/s。CAN网络最高性能极限为1Mb/s,而FlexRay总数据速率可达20Mb/s。FlexRay还能够提供很多网络所不具有的可靠性特点,尤其是FlexRay具备的冗余通信能力,通过硬件可实现完全复制网络配置,并进行进度监测。CAN总线和FlexRay总线两者在功能及搭配上可实现互补。FPGA在数字电路设计上非常灵活且性能强大,在不改变外围电路的情况下,可以编写不同的片内电路逻辑,以实现不同功能或进行功能扩展。

本文提出的车电总线接口单元综合考虑用户的具体需求,保留CAN总线作为卫星导航设备接口总线,其余接口总线采用高速的FlexRay总线,既兼容较低速接口的通信速率要求,又满足高速总线接口的需要,将CAN和FlexRay总线结合在一起,基于FPGA,使成本与效益最大化。

2 车电总线架构

本文综合化处理系统项目中处理系统采用多处理器结构,板间通信数据量较大。若采用PCI总线进行信号传输则由于PCI总线带宽有限,当数据量较大时容易形成通信瓶颈,且PCI总线不支持点对点传输。若选用以太网,则传输速率较低,软件开销较大,且高带宽带来的高成本使它在系统内互连时缺乏吸引力。结合项目采用高速实时总线的具体要求,最终选择基于VPX架构的RapidIO总线进行通信传输。VPX总线采用高速串行总线技术替代VME总线的并行总线技术,支持更高的背板带宽。其交换式结构使得系统整体性能不再受主控板的控制,提高了系统的整体性能。通过串行RapidIO(SRIO)转换,完成了RapidIO-CAN、RapidIO-FlexRay协议转换功能,实现了车电总线与任务总线(RapidIO)的无缝连接,进而满足了处理系统项目高速、多处理器、实时的通信传输要求。

2.1 CAN技术

控制器局部网(ControllerAreaNetwork,CAN)属于现场总线的范畴,它是一种有效支持分布式控制或实时控制的串行通信网络。CAN的应用范围遍及从高速网络到低成本的多线路网络。

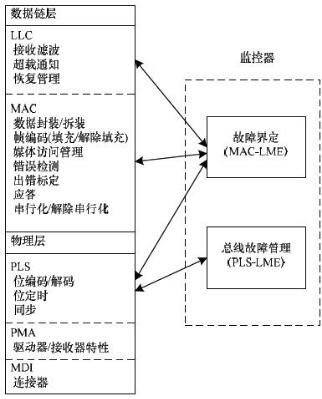

(1) CAN的分层结构

CAN遵从OSI模型,按照OSI基准模型,CAN结构划分为2层:数据链路层和物理层,如图1所示。

图1 CAN分层结构

按照IEEE802.2和802.3标准,数据链路层又划分为逻辑链路控制和媒体访问控制;物理层又划分为物理信令、物理媒体附属装置和媒体相关接口。其中,逻辑链路控制子层为数据传递和远程数据请求提供服务;访问媒体控制子层的功能主要是传送规则,即控制帧结构、执行仲裁、错误检验、出错标定和故障界定。

(2) CAN总线的主要特点

CAN为多主工作方式,网络上的任意节点在任意时刻都可以主动地向其他节点发送信息,不分主从,方式灵活。其采用非破坏性的总线仲裁技术,可以进行点对点、一点对多点和全域广播方式传递信息,多点同时发送信息时,按优先级顺序通信,节省总线冲突仲裁时间,避免网络瘫痪。报文传送采用短帧数据结构,传输时间短,抗干扰能力强,检错效果好。网络节点在错误严重的情况下可以自动关闭输出功能,脱离网络,实现了标准化、规范化。

2.2 FlexRay技术

(1) FlexRay分层结构

FlexRay的分层结构由物理层、传输层、表示层及应用层组成。物理层定义了信号的实际传输方式,包括在时域上检测通信控制器故障的功能;传输层是FlexRay协议的核心,它的功能是从表示层获得节点要发送的信息和把网络上接收的信息传送给表示层;表示层完成信息过滤、信息状态处理以及通道控制器与主机的接口;应用层由应用系统定义。

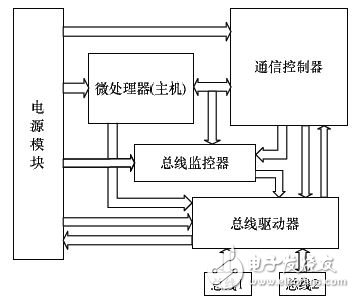

(2) FlexRay节点结构

FlexRay节点的核心是ECU(Electronic Control Unit),是接入车载网络中的独立完成相应功能的控制单元。主要由电源供给系统、主处理器、固化FlexRay通信控制器、可选的总线监控器和总线驱动器组成。主处理器提供和产生数据,并通过FlexRay通信控制器传送出去。其中驱动器和监控器的个数对应于通道数,与通信控制器和微处理器相连。总线驱动器连接着通信控制器和总线,或是连接总线监控器和总线。主处理器把FlexRay控制器分配的时间槽通知给总线监视器,然后总线监视器就允许FlexRay控制器在这些时间槽中传输数据。数据可以随时被接收。结构图如图2所示。

图2 FlexRay节点结构

(3) FlexRay网络拓扑结构

FlexRay的网络拓扑结构主要分为3种:总线式,星型,总线星型混合型。在星型结构中还存在级联方式。通常,FlexRay节点可以支持2个信道,在双信道系统中,不是所有节点都必须与2个信道连接。与总线结构相比,星状结构的优势在于:它在接收器和发送器之间提供点到点连接。该优势在高传输速率和长传输线路中尤为明显。另一个重要优势是错误分离功能。双通道备用星型结构如图3所示。

图3 FlexRay网络拓扑结构

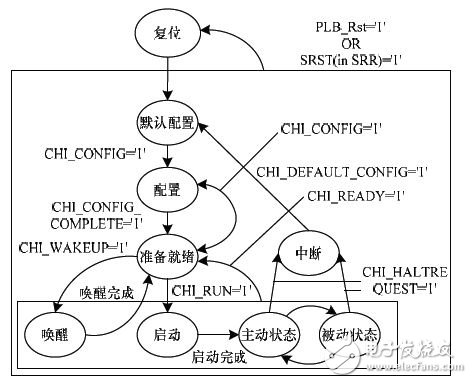

(4) FlexRay状态

FlexRay的节点有6个基本的运行状态:

1)配置状态(默认配置/配置):用于各种初始化设置,包括通信周期和数据速率。

2)就绪状态:用于进行内部的通信设置。

3)唤醒状态:用于唤醒没有在通信的节点。当节点的收发器接受到唤醒特征符后,对主机处理器和通信控制器进行上电,唤醒并激活通信控制器、总线驱动器和总线监控器。

4)启动状态:用于启动时钟同步,并为通信做准备。只有将节点唤醒后,才能启动节点工作。系统的启动由2个逻辑步骤组成,冷启动节点启动和其他非冷启动节点通过接受启动帧与冷启动节点整合到一起。

5)正常状态(主动/被动):可以进行通信的状态。

6)中断状态:表明通信中断。

FlexRay状态图如图4所示。

图4 FlexRay状态

3 车电总线接口单元设计

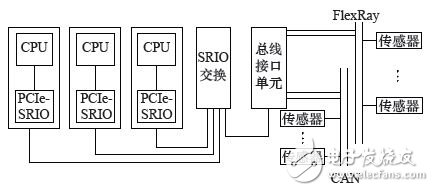

3.1 总线接口单元组成

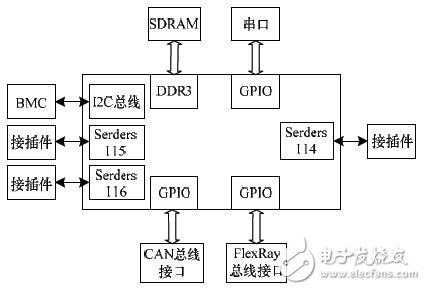

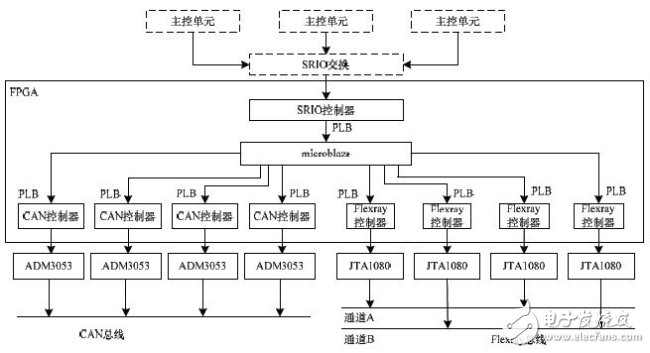

在综合化处理系统架构中,车电总线访问可简化为下列部分:主控单元,RapidIO交换单元,总线接口单元和车电总线。主控单元包含处理器和PCIe-SRIO转接桥。处理器将信号发送至PCIe-SRIO转接桥,数据通过SRIO交换,传输至总线接口单元,最终实现处理器对车电总线上各传感器的访问与控制。车电总线访问的整体架构如图5所示。

图5 系统总体架构

总线接口单元采用3U、VPX结构,板卡主要由XILINX的Virtex6系列FPGA XC6VLX75T完成CAN总线控制器、FlexRay总线控制器、RapidIO总线接口等模块功能,辅之以CAN和FlexRay总线接口PHY、晶振、电压转换器等芯片完成总线接口单元设计。总线接口单元主要完成RapidIO-FlexRay、RapidIO-CAN协议转换功能,实现了车电总线与任务总线(RapidIO)的无缝连接。由于该总线接口模块不含FlexRay总线监控功能,若要实现对总线的监控,需在节点上外接监控设备。总线接口单元功能组成框图如图6所示。

图6 总线接口单元功能组成框图

3.2 车电总线接口设计

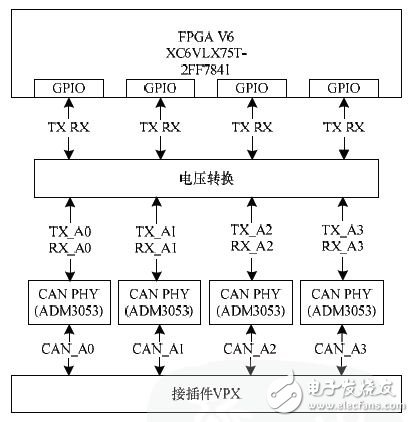

3.2.1 CAN总线接口设计

单元模块通过FPGA输出四路GPIO信号,GPIO连接电压转换芯片以完成电平转换,CAN总线信号完成电平转换后连接CAN芯片,从而输出CAN总线信号与总线接口单元VPX接插件相连,如图7所示。

图7 CAN总线接口硬件组成原理

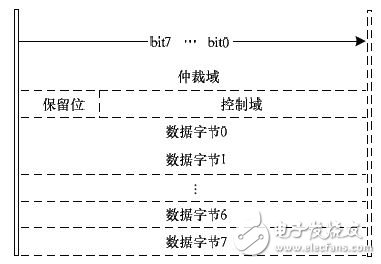

CAN帧时,处理器驱动在内存定义并组织一个下图结构体,使用RapidIO中NWRITE-R事务,写入FPGA控制器CAN发送缓冲区地址,即刻完成发送;当CAN控制器完成发送后,将对该处理器产生中断,告知发送结果。

当接收CAN帧时,处理器驱动在内存定义一个上图结构体,并将内存地址使用Rapid IO中NWRITE-R事务,写入FPGA控制器CAN接收缓冲区地址;当CAN控制器接收完一帧后,通过NWRITE-R事务写入对该处理器地址空间中并产生中断,告知发送结果。图8是内存数据结构。

图8 CAN内存数据结构

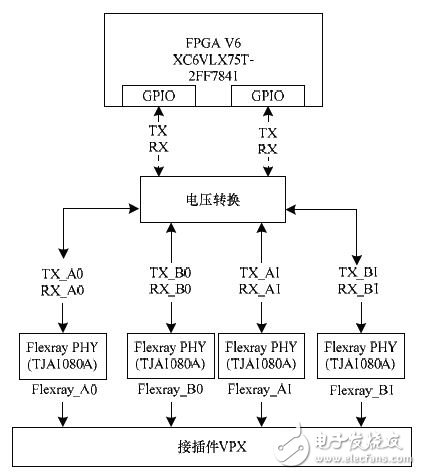

3.2.2 FlexRay总线接口设计

单元模块通过FPGA输出两路GPIO信号,GPIO连接电压转换芯片以完成电平转换,FlexRay总线信号完成电平转换后各输出两路连接FlexRay收发器。由于该XILINX核中只支持FlexRay单信道,因此选择两路FlexRay信道形成冗余设计,2组信道都分为A、B2个通道,满足FlexRay双信道的要求。收发器选用TJA1080,TJA1080收发器是恩智浦公司出品的一款针对FlexRay的具有高速时间触发通讯系统的收发芯片,也是全球第一款符合FlexRay协议2.1规定的FlexRay收发器,具有高达10Mb/s的数据传输速度。每路信号分别通过JTA1080后,最终输出四路FlexRay信号,并与总线接口单元VPX接插件相连。详细结构如图9所示。

图9 FlexRay总线接口硬件组成原理

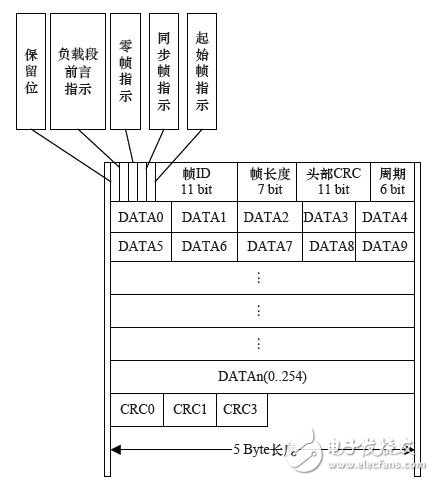

FlexRay每个数据的数据帧由帧头、有效数据段、帧尾3个部分组成。若为发送,当时间片快到时,链表控制器通过RioMaster模块发送NREAD事务包请求数据,返回的数据进入SendFIFO,由FlexRayIP读取。若为接收,当时间片到时,链表控制器提供接收的基地址,数据收到后将存放于RecvFIFO中,结合接收基地址,通过NWRITE-R写入远端内存,之后发送Doorbell使处理器产生中断。其内存数据结构如图10所示。

图10 FlexRay内存数据结构

3.3 FPGA逻辑设计

本文设计通过硬件实现CAN总线控制器、FlexRay总线控制器、RapidIO总线接口等模块功能。采用Virtex6系列FPGAXC6VLX75T完成RapidIO-FlexRay、RapidIO-CAN协议转换功能。

FPGA单元包含SRIO控制器、microblaze软核及四路CAN控制器和两路FlexRay控制器。处理器将信号发送至PCIe-SRIO转接桥,经过桥芯片转换发送至SRIO交换板。交换板的一端将信号转发到SRIO控制器上,SRIO核通过PLB总线将控制信号发送至microblaze软核,经过处理信号通过PLB总线发送至四路CAN控制器和两路FlexRay控制器。每路CAN控制器均连接CAN转换器ADM3053,每路FlexRay控制器均连接FlexRay收发器JTA1080。经过转换器最终分别连接至CAN总线和FlexRay总线上。该逻辑设计的主要特点有3个:

(1)SRIO-PLB桥实现了总线接口单元模块的srio总线接入功能。

(2)CAN和FlexRay总线控制器通过板载收发器实现了CAN、FlexRay总线的接入功能。

(3)microblaze软核实现了CAN、FlexRay控制器消息和事件的预处理,完成了与SRIO总线的互连,并做了任务迁移,减轻了主控处理器的压力。

详细逻辑结构如图11所示。

图11 FPGA模块内部逻辑结构

4 仿真与验证

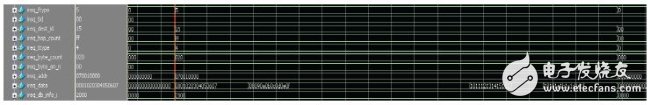

4.1 RapidIO仿真与验证

在Xilinx的ISE14.1开发环境下,基于车电总线接口单元模块对RapidIO接口进行了验证,利用ModelSim对逻辑设计进行仿真,其波形图如图12、图13所示,通过判断数据的一致性可以验证RapidIO总线接口的正确性和有效性。

图12 RapidIO数据发送时序图

图13 RapidIO数据接收时序图

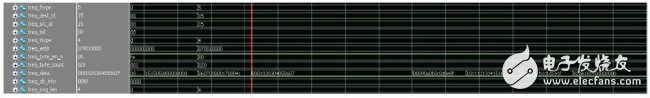

4.2 FlexRay仿真与验证

基于车电总线接口单元模块对FlexRay接口状态机制进行了验证,利用ModelSim对逻辑设计进行仿真,其波形图如图14所示。

图14 FlexRay数据收发时序图

从仿真波形中可以清楚地看出FlexRay状态机制的变化过程。当节点的收发器接收到唤醒特征符后,对主机处理器和通信控制器进行上电,唤醒并激活通信控制器、总线驱动器和总线监控器。节点0被唤醒后,将返回唤醒完成信号,并处于等待启动状态。接着节点1收到唤醒信号,返回唤醒完成信号,节点1进入启动状态,节点0也进入启动状态,最终都进入主动工作状态,开始状态机循环,显示FlexRay总线接口工作正常。

4.3 CAN仿真与验证

调用FPGA内的CAN核基于车电总线接口单元模块对FlexRay接口状态机制进行验证,利用ModelSim对逻辑设计进行仿真,结果如图15所示。端口1发送扩展帧信号,端口0接收,当接收ACK信号时,端口1也接收ACK信号,完成整个扩展帧的收发过程。

图15 CAN数据收发时序图

图15说明了总线接口单元模块RapidIO接口、FlexRay接口和CAN接口完成仿真测试,工作正常,完成了RapidIO-FlexRay、RapidIO-CAN的协议转换功能。

5 结束语

目前,笔者所在团队已成功完成核心处理机系统正样样机的整体测试及验证工作。本文设计在该系统中已经通过功能性测试,基于RapidIO的CAN总线控制器在1Mb/s的最大波特率下工作正常,满足各项功能指标,基于RapidIO的FlexRay总线控制器在10Mb/s的最大波特率下也满足各项功能指标。下一步的工作将通过专业的CAN、FlexRay网络测试仪器对本文设计进行更全面的性能测试,同时将着重解决FlexRay总线接口的信道冗余问题,通过对FlexRay控制器IP核的升级,使之支持双信道通信,从而满足FlexRay真正意义上的双信道冗余要求。

-

基于FPGA的CAN总线通信节点设计2023-06-18 4548

-

分享一款不错的采用FPGA的集群通信移动终端设计方案2021-05-25 1537

-

求一款在PCI总线上利用FPGA技术设计PCI总线接口的设计方案2021-04-15 1235

-

工业通信总线设计的实施方案演示介绍2019-05-08 3946

-

基于FPGA的车电总线接口简述及模块设计2017-11-18 10648

-

基于FPGA的VME总线与DSP通信接口设计2017-10-19 1357

-

基于FPGA的CAN总线通信系统2016-05-10 785

-

基于FPGA的I2C SLAVE模式总线的设计方案2014-02-26 21328

-

多种EDA工具的FPGA设计方案2012-08-17 2094

-

FPGA设计大赛设计方案提交规则和截止时间须知2012-05-04 20909

-

无线应急指挥通信车的设计方案2011-04-15 1126

-

基于FPGA的无线通信收发模块设计方案2009-12-10 2084

-

利用FPGA的无线通信收发模块设计方案2009-11-26 42254

-

基于FPGA的总线型LVDS通信系统设计2009-06-20 7154

全部0条评论

快来发表一下你的评论吧 !