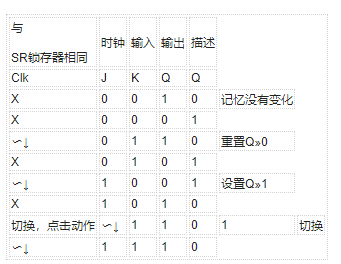

JK人字拖触发器和函数表

描述

JK触发器类似于SR触发器,但当J和K输入均为低电平时状态没有变化

基本SR NAND触发器电路在顺序逻辑电路中有许多优点和用途,但它有两个基本的切换问题。

1。必须始终避免设置= 0和复位= 0条件(S = R = 0)

2。如果在使能(EN)输入为高电平时置位或复位改变状态,则可能不会发生正确的锁存动作

然后,为了克服SR触发器设计的这两个基本设计问题,JK触发器

开发。

这个简单的JK触发器是所有触发器设计中使用最广泛的,被认为是通用触发器电路。标有“J”和“K”的两个输入不是缩写其他单词的缩写字母,例如Set的“S”和复位的“R”,但它们本身是由其发明者Jack Kilby选择的自主字母来区分翻转其他类型的翻转设计。

JK触发器的顺序操作与前一个具有相同“设置”和“复位”输入的SR触发器完全相同。这次的不同之处在于,即使 S 和 R 都处于逻辑“1”,“JK触发器”也没有SR Latch的无效或禁止输入状态。

JK触发器基本上是一个门控SR触发器,增加了一个时钟输入电路,可以防止输入S和输入时出现的非法或无效输出条件R等于逻辑电平“1”。由于这个额外的时钟输入,JK触发器有四种可能的输入组合,“逻辑1”,“逻辑0”,“无变化”和“切换”。 JK触发器的符号类似于 SR Bistable Latch 的符号,如前一个教程所示,除了添加时钟输入。

Basic JK Flip-触发器

<<<>>>>

先前SR双稳态的 S 和 R 输入现在已被两个名为 J <的输入所取代/ span>和 K 分别在其发明者Jack Kilby之后输入。然后,这相当于: J = S 和 K = R 。

两个2输入 AND 门门控SR双稳态现已被两个3输入 NAND 门取代,每个门的第三个输入连接到 Q 和 Q 的输出端。 SR触发器的这种交叉耦合允许先前无效的 S =“1”和 R =“1”状态用于产生“切换动作” “因为两个输入现在是互锁的。

如果电路现在是”SET“, J 输入被 Q 通过较低的 NAND 门。如果电路为“RESET”, K 输入被 Q 的“0”状态禁止通过上 NAND 门。由于 Q 和 Q 总是不同,我们可以使用它们来控制输入。当输入 J 和 K 等于逻辑“1”时,JK触发器将切换,如下面的真值表所示。

真相JK函数表

然后JK触发器基本上是一个带有反馈的SR触发器只有两个输入端子中的一个,SET或RESET在任何时候都有效,从而消除了之前在SR触发器电路中看到的无效状态。

同样当 J 和 K 输入同时处于逻辑电平“1”,时钟输入脉冲为“高电平”,电路将从其SET状态“切换”到RESET状态,或反之亦然。这导致当两个端子都为“高”时,JK触发器更像是T型触发器。

虽然这个电路是时钟SR触发器的改进,但如果输出 Q 在时钟输入的定时脉冲有时间之前改变状态,它仍然会遇到称为“竞争”的定时问题去“关”。为避免这种情况,定时脉冲周期( T )必须尽可能短(高频)。由于现代TTL IC有时无法做到这一点,因此开发了大大改进的Master-Slave JK触发器。

Master-Slave JK Flip-flop

主从触发器通过使用串联配置连接在一起的两个SR触发器消除了所有时序问题。一个触发器充当“主”电路,其在时钟脉冲的前沿触发,而另一个触发器充当“从”电路,其在时钟脉冲的下降沿触发。这导致两个部分,主部分和从部分在时钟信号的相反半周期期间被使能。

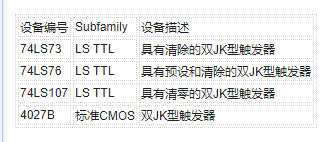

TTL 74LS73是双JK触发器IC,其包含两个单独的JK在单个芯片中键入双稳态,可以制作单个或主从触发触发器。其他JK触发器IC包括具有清零的74LS107双JK触发器,74LS109双正边沿触发JK触发器和具有预置和清除输入的74LS112双负边沿触发触发器。

双JK触发器74LS73

其他流行的JK触发器IC

主从式JK触发器

主从式触发器基本上是两个门控SR触发器,它们与从器件串联配置连接在一起具有反相时钟脉冲。来自“Slave”触发器的 Q 和 Q 的输出反馈到“Master”的输入,“Master”触发器的输出为连接到“Slave”触发器的两个输入。从从机输出到主机输入的这种反馈配置给出了JK触发器的特性切换,如下所示。

主从JK触发器

输入信号 J 和 K 连接到门控“主”SR触发器,“锁定“输入条件,而时钟( Clk )输入在逻辑电平”1“为”高“。由于“从”触发器的时钟输入是“主”时钟输入的反相(补码),因此“从”SR触发器不会切换。当时钟输入变为“低”到逻辑电平“0”时,“主”触发器的输出仅被门控“从”触发器“看到”。

当时钟为“低”时“,”主“触发器的输出被锁存,其输入的任何其他变化都将被忽略。门控“从”触发器现在响应由“主”部分传递的输入状态。

然后在时钟脉冲的“从低到高”转换时,输入“主”触发器被馈送到“从”触发器的门控输入,并且在“从高到低”转换时,相同的输入反映在“从”的输出上,使得这种类型的触发器边缘或脉冲触发。

然后,当时钟信号为“高”时,电路接受输入数据,并在时钟信号的下降沿将数据传递给输出。换句话说,主 - 从JK触发器是一个“同步”器件,因为它只通过时钟信号的时序传递数据。

在下一个教程中关于顺序逻辑电路,我们将看一下用作波形发生器的多谐振荡器,以产生时钟信号来切换时序电路。

-

怎么用jk触发器变成t触发器2024-08-28 6469

-

主从jk触发器和边沿jk触发器的区别2024-08-22 8389

-

Jk触发器的故事2024-02-23 4159

-

如何用jk触发器构成t触发器?t触发器逻辑功能有哪些2024-02-06 12999

-

JK触发器的工作原理及真值表2023-06-29 80774

-

jk触发器是什么原理2021-02-26 4339

-

JK触发器基本教程,讲的超详细!!2021-02-01 17657

-

JK触发器逻辑符号_jk触发器的特性方程2019-11-08 97494

-

jk边沿触发器工作原理2018-01-30 38735

-

jk触发器是什么原理_jk触发器特性表和状态转换图2017-12-25 192882

-

jk触发器实现74ls194功能2017-12-22 25858

-

LED发光的人字拖2012-10-22 4090

-

JK触发器,JK触发器是什么意思2010-03-08 7617

全部0条评论

快来发表一下你的评论吧 !