多种SPI总线隔离设计方案

接口/总线/驱动

描述

简介

串行外设接口(SPI)是一种同步串行总线接口,常用于微处理器和外围设备之间的短距离通信。SPI总线不是一种管理严格的协议,可以用各种方式来实现。常常需要使用电气隔离,或者电气隔离能带来好处。本应用笔记讨论各种SPI隔离技术,以帮助设计人员应对不同的系统级挑战,例如高通信速度、有限的印刷电路板(PCB)面积和低功耗。本应用笔记还可作为各种SPI隔离解决方案的选择指南。

SPI协议通常由四个单向单端通道组成。SPI主机输出三个信号:时钟、串行数据和从器件选择。一条串行数据线自从器件返回主器件。在kbps和低mbps数据速率下,此物理层使SPI成为比较容易在主器件和从器件之间实现电气隔离的协议。对于全双工通信,标准四通道数字隔离器常常就足以实现透明的“直接使用”式解决方案。如果数据速率更高,则需要其他技术。

时钟速度最大化

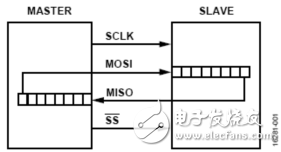

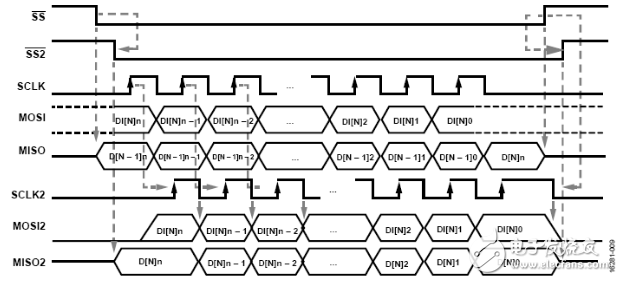

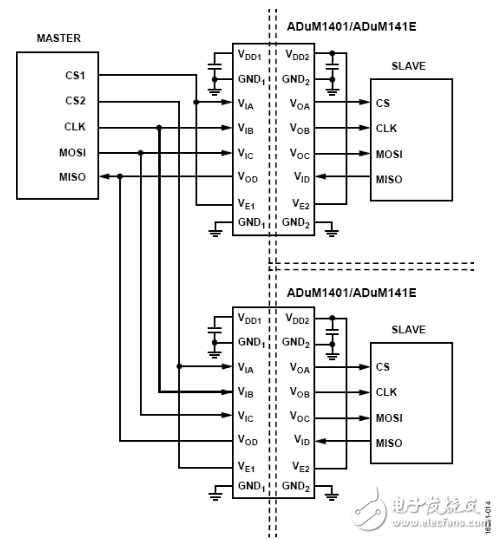

更普遍且更传统的形式是单一主器件与一个或多个从器件进行全双工通信。主器件通过将片选线设置为低电平并发送时钟信号来启动与从器件的通信。主器件和选定的从器件均在时钟上升沿写入总线,并在时钟下降沿读取数据。图1和图3中的示例系统便使用这种形式的SPI通信。

图1.标准SPI实现

三个正向通道、一个反向通道(3/1)的标准数字隔离器

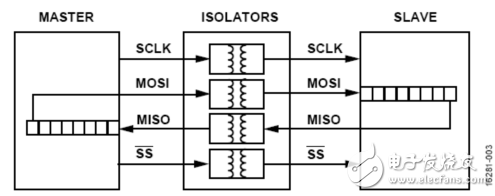

为定向通道添加隔离是相当直接的过程。数字隔离器是SPI隔离的自然选择,因为这些隔离器提供低传播延迟、良好的通道间匹配、紧凑的单芯片解决方案、鲁棒的通信且易于实施。这些特性使数字隔离器优于光耦合器解决方案。

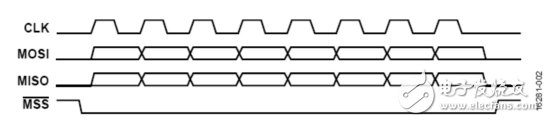

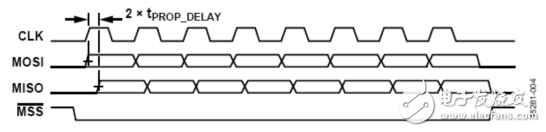

在数据采集系统中,吞吐速率不断攀升。尽管传播延迟很短,但这些延迟确实会限制全双工通信的最大数据速率。图2和图4的差异说明了这一影响。

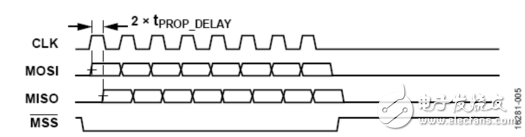

图2.标准SPI时序图

时钟速率限制

为了计算最大SPI时钟速度,全双工“直接使用”式实施方案必须考虑数字隔离器的若干特性。最小脉冲宽度、最大数据速率和传播延迟都可能是限制因素。

图3显示了利用通用3/1四通道标准数字隔离器作为“直接使用”式电气隔离解决方案的SPI总线隔离。SPI时钟信号每个周期改变状态两次,但通过数字隔离器的数字数据并非如此。标准数字隔离器必须具有支持时钟信号的最大数据速率特性。在此示例器件中,最大数据速率特性不是限制因素。

图3.标准数字隔离器SPI隔离

注意图4中传播延迟的影响。在这个例子中,数据在时钟上升沿发送,在下降沿接收。

图4.带隔离的标准SPI时序图

主器件同时开始时钟和主器件输出、从器件输入(MOSI)信号的传输。从器件的主器件输入、从器件输出(MISO)信号传输由时钟上升沿触发;由于时钟沿延迟,MISO信号也被延迟。MISO信号随后必须经过标准数据隔离器,再到达主器件。在这个例子中,从器件和主器件均在时钟下降沿读取数据。

SPI通信取决于与MISO信号同步的时钟信号。图5显示了传播延迟的影响,数据速率一直增加到通信失败。由于传播延迟,时钟下降沿导致读取发生在MISO信号转换时,而非MISO信号建立时。此系统的数据速率过高,通信不可靠。

图5.主器件视角下的时序图

如图5所示,到从器件和返回到主器件的传播延迟必须发生在小于SPI时钟周期一半的时间内。在应用中,PCB走线延迟、建立时间和从器件响应时间可能会进一步降低最大时钟速率。为简单起见,本应用笔记忽略这些因素,因此“直接使用”式全双工实施方案具有如下关系:

SPI时钟半周期 ≥ 2 × tPROP_DELAY

用数据手册中的最大传播延迟值计算最大数据速率。尽管系统在实验室中可以实现更高速度,但为了确保通信鲁棒,必须考虑温度、电源电压和器件的变化。表1提供了关于ADI公司各种数字隔离器的最大SPI数据速率的指南。

表1.“直接使用”式全双工数字隔离器最大SPI时钟速率

| 产品型号 | 数据速率(最大值) | 传播延迟(最大值) | “直接使用”式全双工SPI时钟(最大值) | 独有特性 |

| ADuM1401ARWZ | 1 Mbps | 100 ns | 500 kHz1 | 隔离式SPI基准 |

| ADuM1441 | 2 Mbps | 180 ns | 1 MHz1 | 超低功耗,本质安全,支持IEC60079-11标准下的IS-IS隔离 |

| ADuM7441 | 25 Mbps | 50 ns | 5 MHz | 成本敏感型基本隔离 |

| ADuM141D/ADuM141E | 150 Mbps | 13 ns | 19.2 MHz | 对辐射噪声和传导噪声有很高的抗干扰能力,1.8 V工作电压,提供小到QSOP的封装选项 |

| ADuM241D/ADuM241E | 150 Mbps | 13 ns | 19.2 MHz | 对辐射噪声和传导噪声有很高的抗干扰能力,1.8 V工作电压,5 kV耐受电压 |

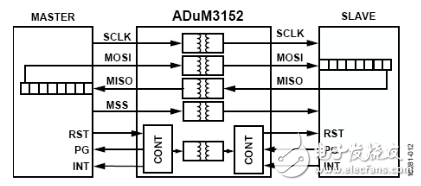

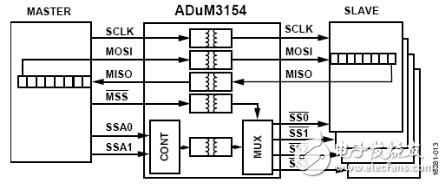

| ADuM3151/ADuM3152/ADuM3153 | 34 Mbps | 14 ns | 17.8 MHz | 高数据速率,三个额外的250 kbps控制/信号通道,小尺寸SSOP封装 |

| ADuM4151/ADuM4152/ADuM4153 | 34 Mbps | 14 ns | 17.8 MHz | 高数据速率,三个额外的250 kbps控制/信号通道,5 kV耐受电压 |

1 受最小脉冲宽度特性限制。

独立延迟时钟(回绕时钟)

将标准数据数字隔离器插入SPI信号链可以实现的数据速率较低,一些全双工应用要求更快的SPI数据速率。图5所示的同步困境可以通过将时钟信号与MISO信号一道送回主器件来解决。更高数据速率是可以实现的,但采用这种方法时要考虑给SPI主器件设计带来的额外复杂性。通常,读取延迟的MISO和时钟信号需要额外的移位寄存器。

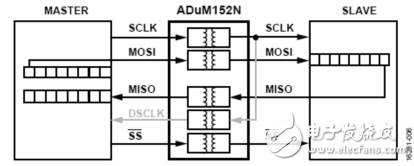

采用标准数据隔离器实现的独立延迟时钟技术需要额外的隔离通道来返回(或回绕)主时钟信号。回绕时钟信号通过额外的隔离通道返回主器件。该延迟时钟信号被隔离器的正向和反向传播延迟所延迟,就像MOSI信号传输到从器件和MISO信号返回被延迟一样(见图6)。对于这种方法,必须使用具有低通道匹配时序特性的数字隔离器。最小SPI时钟周期(不考虑从器件和走线延迟)由最大脉冲宽度失真和同向通道匹配特性决定。确保计算出的最小SPI半时钟大于器件最小脉冲宽度特性。

SPI时钟半周期 ≥ 2 × tPWD+ tPSKCD

例如,ADuM152N的最大脉冲宽度失真为4.5 ns,最大同向通道匹配为4.0 ns,理论上可以获得最大38.4 MHz的时钟速度。

实践中,必须考虑走线长度和从器件响应的延迟。

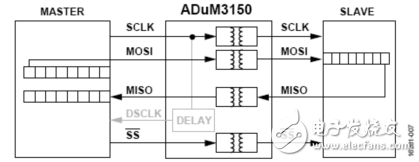

图6.使用隔离通道延迟的高速SPI

SPI数字隔离器ADuM3150和ADuM4150提供一个经调整的延迟时钟信号作为标准特性。如图7所示,ADuM3150在主器件侧实现了一个延迟电路。ADuM4150也在主器件侧实现了一个延迟电路。延迟时钟(DCLK)信号在ADuM3150出厂测试期间进行调整,以匹配各隔离器的往返传播延迟。与图6不同,ADuM3150不需要额外的隔离通道。这些SPI数字隔离器能够处理的最高时钟速率为40 MHz。

图7.使用精密时钟延迟的高速SPI

表2.回绕时钟SPI数据速率

| 产品型号 | 电源电压(V) | SPI时钟(最大值) | 独有特性 |

| ADuM152N/ADuM162N | 1.7至5.5 | 38.4 MHz | 对辐射噪声和传导噪声有很高的抗干扰能力,1.8 V工作电压 |

| ADuM252N/ADuM262N | 1.7至5.5 | 38.4 MHz | 对辐射噪声和传导噪声有很高的抗干扰能力,1.8 V工作电压,5 kV耐受电压 |

| ADuM3150/ADuM4150 | 3.0至5.5 | 40 MHz | 延迟时间特性,两个额外的250 kbps控制/信号通道,小尺寸SSOP封装 |

延迟回读隔离器

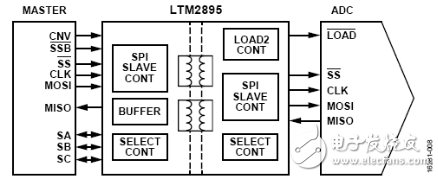

可以不增加延迟时钟信号来同步延迟MISO数据信号,而是用延迟回读隔离器缓冲主器件侧的MISO数据,直到下一个字传输到总线上为止。缓冲MISO数据后,便不需要主器件支持延迟时钟。此过程要求应用容忍MISO数据中的一个字延迟。对于数据主要从主器件写入从器件的应用来说,这不是一个重大限制。延迟回读技术由LTM2895实现,其还包含三个双向选择信号和一个低抖动信号,使该器件成为隔离数模转换器(DAC)的理想选择。

LTM2895跨越隔离栅仅传输关键信号的显著边沿(见图8),从而支持100 MHz时钟的SPI总线操作。使用集成状态机和缓冲器的组合,LTM2895可以完全再生SPI信号。所需的配置信息(例如SPI时钟频率和字长)通过SPI接口和次级端从器件选择()进行配置。在LTM2895完成配置后,该次级端从器件选择信号可改变用途以支持写入另一个隔离侧SPI器件。

图8.超高速DAC流传输隔离器

LTM2895的初级端和次级端通过使用高速异步串行链路(一个正向和一个反向)跨越隔离栅进行内部通信。先占式优先级划分方案确保时序关键信号以低延迟和低抖动进行更新。

图9显示了LTM2895的正常操作序列,其从初级端()的下降沿开始,在次级端()产生相应的下降沿,并使MISO输出先前采样的MISO2字的MSB。初级端SCLK的第一个上升沿触发LTM2895对MOSI采样并跨越隔离栅发送信息。当次级端状态机接收到此数据时,状态机更新MOSI2并在一定时间(由SPI时钟频率配置决定)内让SCLK2保持低电平。经过指定的SCLK2低电平时间后,次级端状态机让SCLK2变为高电平,对MISO进行采样,然后将数据发送到初级端缓冲器。当初级端SCK下降时,缓冲的MISO数据发生更新。随后的SCLK上升沿迫使SCKL2在规定时间内保持低电平,而其他信号保持不变。当上升时,SPI事务结束,驱动MISO到高阻态,并让次级端SCLK2和MOSI2处于低电平,让处于高电平。由于未选择LTM2895时MISO为高阻态,所以MISO可与其他从器件共享初级端SPI总线。

MISO数据缓冲器是循环式,使用由配置的字大小分隔的读写指针。

当选择66 MHz或100 MHz的SPI时钟频率时,LTM2895在SCK上升沿更新初级端MISO数据,以提供额外的传播和建立时间。

当保持低电平时支持SPI页模式,可以传输所需倍数的字长。

当用DAC输入端隔离DAC时,LTM2895信号会在下降沿之间产生一个典型抖动为30 ps rms的窄脉冲。的上升沿由LTM2895产生,脉冲宽度为40 ns或60 ns(取决于SCLK2频率设置)。

图9.LTM2895 SPI时序

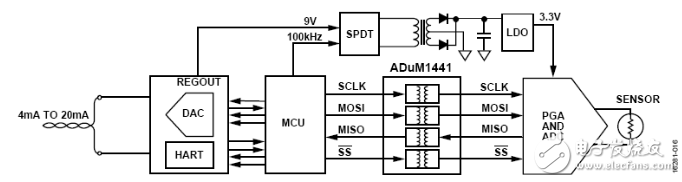

集成隔离电源

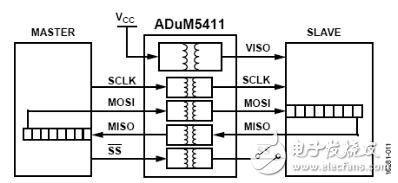

独立电源在某些应用中可能不经济或不可行。在这些设计中,初级端需要隔离电源来为次级端器件供电。传统隔离电源解决方案体积庞大,难以满足隔离鲁棒性和认证要求。这些挑战只需几个isoPower®或μModule®器件就能解决。ADuM5411就是这样一种解决方案(见图10)。该器件提供四个隔离信号通道和高达150 mW的集成隔离电源,但仅占用90 mm2的PCB区域,包括支持性旁路电容。150 mW的集成隔离电源通常足以支持精密ADC或低功耗微控制器单元(MCU)。

图10.带isoPower的SPI隔离

对于隔离功率要求更高的隔离式SPI应用,表3列出了其他解决方案。ADuM5401可以自行提供高达500 mW的隔离功率。ADuM5401还有控制其他兼容isoPower器件的能力。ADuM5401可以用作主器件并将其脉宽调制(PWM)信号发送到一个或多个ADuM5000器件,从而调节自身和每个ADuM5000从器件。

LTM2883-S、LTM2886-S和LTM2887-S是6通道数字μModule隔离器,能够提供高达1 W的输出功率,并有多种输出电压范围可供选择。

ADuM3471集成四个用于SPI的隔离数据通道以及一个开关稳压器。利用一个外部变压器,该器件提供最高2 W、3.3 V至24 V的调节隔离电源。ADuM3471的输出功能使其适合在需要更高功率和更宽电压范围的系统(如模拟输出模块)中提供隔离电源。

表3.集成隔离电源的SPI信号隔离

| 产品型号 | 隔离电源电压 | 隔离电源 | 数据速率(最大值) | “直接使用”式全双工SPI时钟(最大值) |

| ADuM5411 | 可调,3.3 V至5 V | 150 mW | 150 Mbps | 19.2 MHz |

| ADuM5401 | 固定,3.3 V或5 V | 500 mW | 25 Mbps | 4.1 MHz |

| ADuM5401/ADuM5000 | 固定,3.3 V或5 V | 1 W | 25 Mbps | 4.1 MHz |

| LTM2883-S | 固定5 V | 100 mW | 20 Mbps | 4 MHz |

| 固定+12.5 V | 250 mW | |||

| 固定-12.5 V | 187.5 mW | |||

| LTM2886-S1 | 可调,3.0 V至5 V | 500 mW | 20 Mbps | 4 MHz |

| 固定+5 V | 500 mW | |||

| 固定-5 V | 500 mW | |||

| LTM2887-S | 可调,3 V至5 V | 500 mW | 20 Mbps | 4 MHz |

| 可调,0.6 V至5 V | 500 mW | |||

| ADuM3471 | 可调,3.3 V至24 V | 2 W | 25 Mbps | 4.1 MHz |

1 总输出功率高达1 W。

辅助数据通道

除了选择多个从器件之外,低速通道还可以跨越隔离栅传输额外的控制信号,如图11所示。在这种情况下,ADuM3152低速通道支持混合通道方向,将复位信号从主器件发送到从器件,同时沿相反方向发送电源正常和中断信号。SPIsolator®器件系列中的不同器件可创造不同的辅助数据通道方向组合。

图11.带补充功能的SPI隔离

多从器件控制

将多个从器件连接到SPI总线有两种方法:菊花链或独立从器件配置。菊花链只需要一条从器件选择(SS)线,通过单个隔离端口将链上的全部内容串行移出。如果数据采集序列不固定,则每个SPI从器件必须单独寻址。

一种简单的解决方案是添加更多数字隔离通道,例如ADuM161N。对于需要为SS信号精确定时的系统,建议使用此解决方案。例如,当从器件是ADC时,SS信号也会启动数据转换。

在时序约束较宽松的应用中,集成4个高速通道和1个低速通道的ADuM3154隔离器可提供一种替代解决方案,如图12所示。ADuM3154支持最高17 MHz的SPI时钟速度,并可控制多达四个独立的从器件。多路复用选择线的传播延迟为100 ns至2.6 μs,具体取决于输入数据边沿随内部采样时钟而变化的位置。通过消除三个隔离通道,此解决方案比标准数字隔离器解决方案更紧凑,性价比更高。

图12.带多从器件控制的SPI隔离

当一个主器件与多个从器件在独立的隔离平面上通信时,例如图13所示,数字隔离器必须能够让初级端MISO线处于三态。如果MISO不处于三态,由于数字隔离器的输出引脚处于争用状态,通信将不可能进行。

对于具有一个主器件和多个非隔离/隔离从器件的应用,还需要对来自隔离器的MISO信号进行三态缓冲。

图13.针对相互隔离的从器件的MISO三态

超低功耗应用

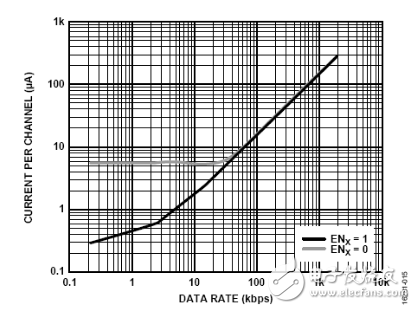

隔离对电子系统安全是必需的,但隔离也被认为是一种负担,因为它会限制通信速度,占用电路板空间,并且消耗相当多的功率。前两者通过创新来解决,即实现时钟速度最大化和电路板空间最小化。有些应用要求超低功耗,如电池供电设备和4 mA至20 mA环路供电工业变送器。目前,数字隔离器的功耗(远远低于光耦合器)必须降低两至三个数量级才能进入这些新的应用领域。

数据速率固定之后,数字隔离器的功耗水平主要由数据编码方案决定,这些方案大致可分为脉冲编码架构和开关键控(OOK)架构。脉冲编码方案的优势是在较低数据速率时消耗的电源电流较低,而OOK在较高数据速率(10 Mbps以上)时消耗的电流比脉冲编码方法要低。在大多数低功耗应用中,SPI时钟速度低于1 MHz,因而脉冲编码方案是更好的选择。

不过,脉冲编码方案有一个缺点:如果输入端无逻辑变化,则不会将数据发送到输出端。系统上电后输入和输出之间可能出现不匹配,或者外部噪声可能会扰乱输出数据。定期重新发送直流状态可以解决此问题。大多数脉冲编码数字隔离器每隔1 µs刷新一次直流状态,但刷新速率也会设置一个点:在该点,当数据速率下降时,功耗停止下降。

ADuM1441将刷新速率降至17 kHz,因此功耗非常低。为了尽可能降低功耗,刷新电路可以完全禁用。如图14所示,在禁用刷新电路的情况下,ADuM1441的功耗降至μW范围。系统设计人员可以低得多的频率发送直流正确性脉冲来平衡功耗与数据完整性。

图14.ADuM1441每个通道的总电源电流(VDDX = 3.3 V)

大部分现场仪表是环路供电型设备。从环路获得的电源必须为仪表内的一切供电,包括传感器和所有支持电子电路。最小环路电流为4 mA,因此这种设计只能使用3.5 mA,这是允许的最大系统功耗。为现场变送器设计选择器件时,功耗是首要考虑因素。大多数标准数据数字隔离器的两侧都会消耗几毫安的电流,而ADuM1441及其超低功耗特性能为隔离式现场仪表提供此功能,如图15所示。

图15.4 mA至20 mA环路供电仪表中的超低功耗SPI隔离

结论

相比于仅在主器件和从器件之间插入四通道数字隔离器,SPI总线隔离可能更为复杂。数据采集系统需要电气隔离以实现抗噪性和安全性,同时不能牺牲吞吐速率。最近的创新使隔离时钟速度达到100 MHz。破天荒第一次,看不见的隔离器(即不会降低时钟速度的隔离器)在如此高的速度下变得可行。与分立解决方案相比,采用小型封装的集成信号与电源隔离方案可大幅简化带次级端电源的SPI隔离的设计,显著缩小电路板空间并降低成本。集成额外低速隔离通道可为多从器件控制或辅助通道应用提供紧凑且高性价比的选择。先进的脉冲编码技术针对超低功耗进行了优化,实现了以前由于电源受限而无法实现的SPI隔离。

-

SPI总线限制及其在隔离系统中的处理方法2023-11-27 470

-

ADI-ADuM隔离DCDC控制器参考设计方案2021-09-17 1379

-

CAN总线接口EMC标准电路设计方案2021-07-12 3767

-

分享一款不错的LPC2294 CAN总线主节点设计方案2021-05-25 1611

-

AN-1478:针对不同系统要求的隔离式SPI总线2021-05-17 666

-

多种负电源轨的设计方案2021-03-11 2346

-

满足各类不同系统需求的多种SPI总线隔离方案分享2021-01-05 3696

-

SPI总线在隔离系统中的处理方法2018-10-10 4517

-

基于CAN总线中的iCoupler隔离方案2017-10-30 973

-

在SPI总线中常用的6N137和ADuM315x两款隔离芯片分析2017-08-25 25258

-

多种EDA工具的FPGA设计方案2010-05-25 939

-

基于TMS320F2812的SPI接口设计方案2010-04-23 2833

-

机载TM总线接口设计方案2010-03-24 1650

全部0条评论

快来发表一下你的评论吧 !