Spartan-3的FPGA与DDR2 SDRAM的接口实现

接口/时钟/PLL

描述

概述: 本应用文档描述了赛灵思斯巴达3系列FPGA与DDR2 SDRAM的接口实现。本文档提供了DDR2 SDRAM的简述,然后一个存储器接口实现的详细描述。

DDR2 设备概述:DDR2 SDRAM接口是源同步、支持双速率传输。比如DDR SDRAM ,使用SSTL 1.8V/IO电气标准,该电气标准具有较低的功耗。与TSOP比起来,DDR2 SDRAM的FBGA封装尺寸小得多。通过时钟上升下降沿的数据集采集,DDR2 SDRAM可以获得高速传输。存储器使用控制器的差分时钟。在每个时钟的上升沿寄存命令信号,双向数据选通信号DQS与数据信号一同传输。在读阶段,DQS由DDR2 SDRAM 设备产生,并且与数据信号边缘对齐;在写阶段,DQS由控制器产生,并且与数据信号中心对齐。对DDR2 SDRAM的读写操作都是突发模式。操作是由激活命令后紧跟一读写命令组成的。

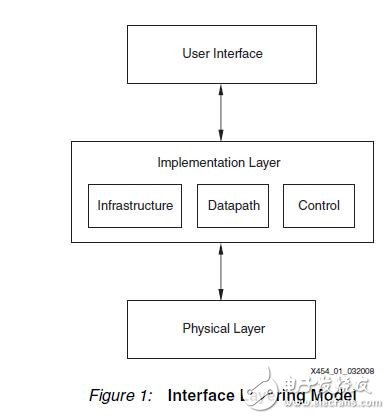

接口模式:

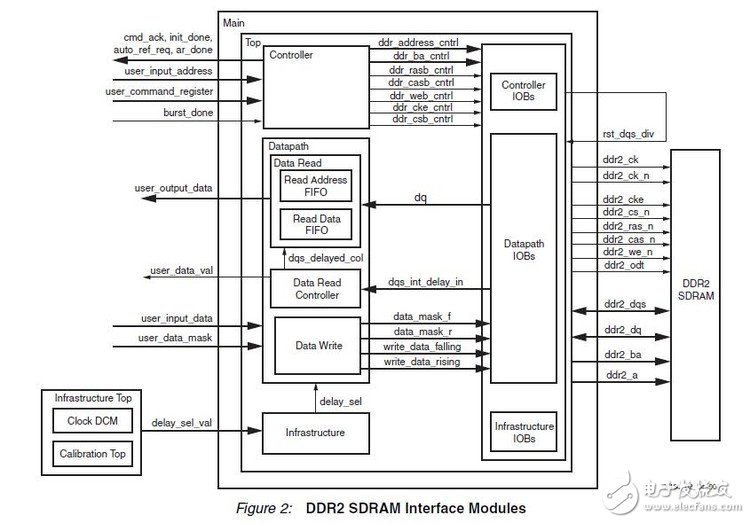

DDR2 SDRAM 控制器模块:

控制器:

控制器支持4或者8字节长度的突发传输,三个CAS延时。控制器在加载命令时初始化EMR2、EMR3寄存器并产生差分数据选通信号。控制器接受用户命令,对用户命令译码并产生读、写和刷新命令。控制器同时产生其他模块的接口信号。

数据路径:数据路径模块负责与存储器进行数据的发送和接收。主要功能包括:

# 写数据到存储器

#从存储器读数据

#将存储器时钟域数据转到FPGA时钟域

写数据和选通信号由FPGA扇出,选通信号与数据信号中心对齐。对于DDR2 SDRAM存储器来说,选通信号是非自由运行。为了满足这些要求,使用FPGA主时钟移相90和270度将写数据扇出。存储器读数据和源同步时钟边缘对齐。

读数据捕获:

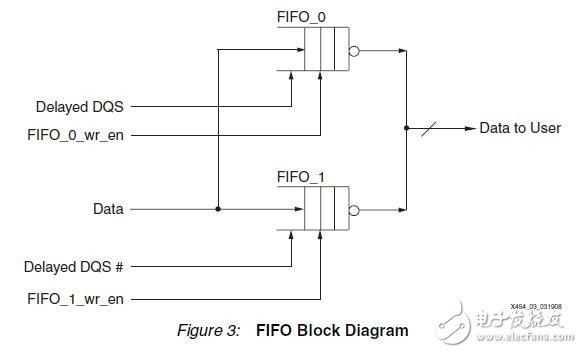

在读数据阶段,DDR2设备发送DQS选通信号和数据信号到FPGA。DQS与数据DQ边缘对齐。数据在每个时钟边缘更新,在FPGA逻辑中,使用DQS延时信号去捕获数据DQ信号。在FPGA中不使用IOB寄存数据而是用基于LUT的双端口专用RAM用于数据捕获。这是最简单的数据捕获模式,不需要在系统时钟域进行二次采集。LUT RAM配置为成FIFO对,每个数据都被写入到两个FIFO。如图3。这些16比特深度的FIFO是异步操作且与读写端口独立。

读数据时钟:

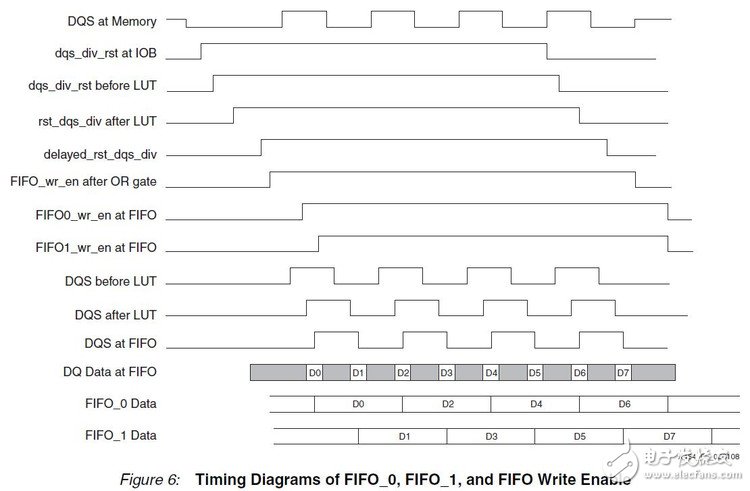

在延时的DQS上升沿从DDR的读取数据写到FIFO_0,在下降沿将数据写到FIFO_1。而数据却能同时从FIFO中读出。

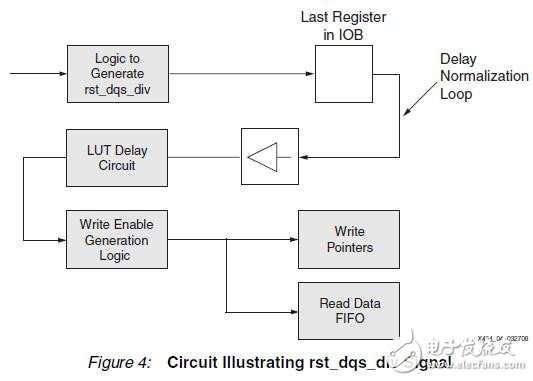

FIFO写指针由延时的DQS驱动。FIFO的读指针是由FPGA内部时钟驱动。当FIFO写使能为高时,FIFO可以被写入数据。FIFO写使能信号由RST_DQS_DIV在每个DQS前导信号产生。

RST_DQS_DIV信号驱动到IOB并且输出,经过一个回环延时后输入到输入缓冲器。环路延时的长度等于前向的时钟信号长度加上DQS的长度。LUT延时电路用于延时DQS。这就保证了RST_DQS_DIV和DQS延时电路在进入FIFO之前具有相同的路径和相似的延时。

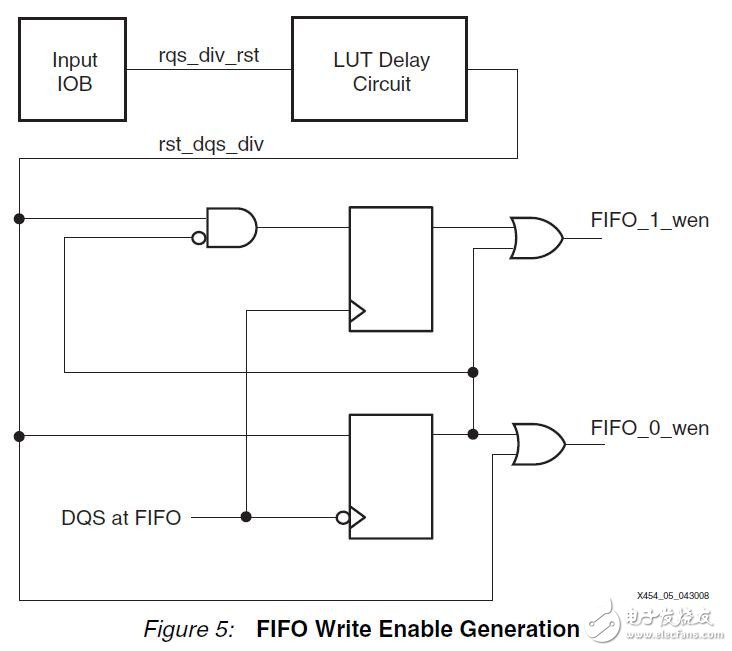

写使能产生:

FIFO_0写使能信号是RST_DQS_DIV和锁存的RST_DQS_DIV信号的逻辑“或”输出。FIFO_1在DQS信号第一个正沿后使能。这个逻辑消除了虚假的数据信号被锁存到FIFO当中,同时也消除了写指针的错误增加。

RST_DQS_DIV无效时的前导周期,锁存的输出使能FIFO和FIFO指针。在DQS最后一个边沿信号,锁存的RST_DQS_DIV标记被清除,此时FIFO和FIFO写指针被禁止。

图6显示了DQS_DIV_RST, RST_DQS_DIV和FIFO写使能信号的时序图。RST_DQS_DIV和FIFO写使能信号的总延时不能超过一个存储器时钟周期。MIG工具生成必须的DQS_DIV_RST,RST_DQS_DIV以及FIFO写使能信号约束(UCF)。

当延时的DQS有效时,数据被锁存到FIFO。FIFO_0、FIFO_1写指针使能当RST_DQS_DIV 有效的时候。数据在延时的DQS上升沿时写入FIFO_0,同时写指针增加。在下降沿数据锁存到FIFO_1,同时FIFO_1写指针增加。

结构:

顶层结构模块产生FPGA时钟信号和复位信号。DCM用于产生CLK0和CLK90.一个延时校准电路实现这个功能。

延时校准电路:

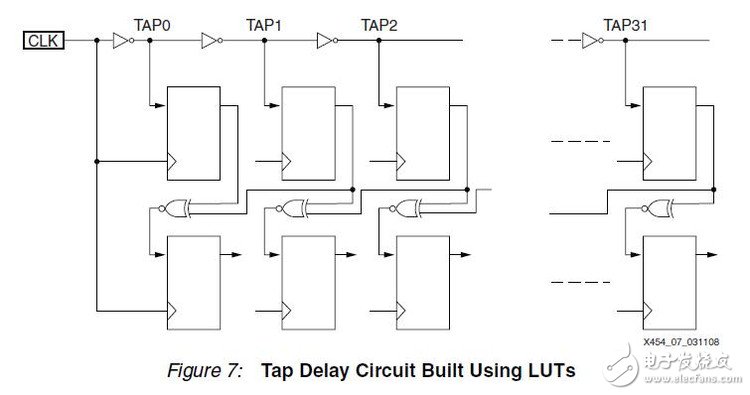

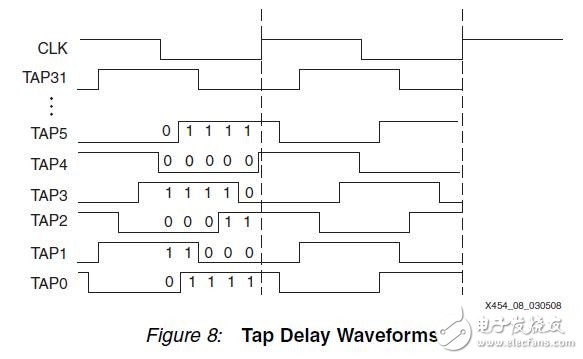

有几个因素可以影响在DQ数据有效窗口中的DQS中心。由于进程、电压、温度变化、LUT延时可能在250~625pS中变化。在抽头延时电路中,LUT延时可以测量。

每个抽头延时都有输入反向。一般XC3S700-5FG484的LUT延时为620ps。对于一个166MHZ的设计,大约有5个或者6个LUT在时钟相位里边。边缘行为(10101101011010或者0101001010010)从抽头电路中产生。

延时电路:

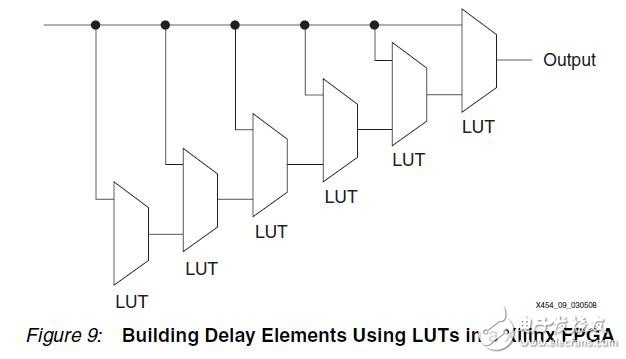

选通信号使用内部延时元件产生,延时元件由LUT和其他资源组成。

-

为什么利用Spartan-3 FPGA来实现DSP系统?2021-04-29 1231

-

Spartan-3系列FPGA的用户指南2020-03-05 2094

-

如何使用DDR2 SDRAM?2019-07-31 1782

-

采用Cyclone III FPGA实现DDR2接口设计2019-05-31 2380

-

如何获得 Spartan-3A FPGA 器件的节能模式2018-05-22 3581

-

SDRAM,DDR3,DDR2,DDR4,DDR1的区别对比及其特点分析2017-11-17 28388

-

基于Spartan3_FPGA的DDR2_SDRAM存储器接口设计2015-11-10 916

-

基于FPGA的DDR2 SDRAM存储器用户接口设计2013-01-08 1766

-

基于Xilinx FPGA的DDR2 SDRAM存储器接口2012-08-20 4605

-

基于Spartan-3 FPGA的DSP功能实现方案2010-12-17 1110

-

基于Spartan-3A的DDR2接口数据采集2010-12-13 903

-

Spartan-3 Generation FPGAs应用资料2010-05-13 912

-

DDR2,DDR2是什么意思2010-03-24 1736

-

什么是DDR2 SDRAM2009-12-17 1000

全部0条评论

快来发表一下你的评论吧 !