Allegro的通用等长规则设置方法

EDA/IC设计

描述

在当今高速PCB设计中,一组走线的等长越来越重要。Allegro为工程师提供了功能强大的Constrain Manager,即约束管理器,工程师可以很方便地进行各种规则的设定,包括等长规则。 在无线时代早前发表的《DDR布线规则与过程》一文中,已经给出了一种设置等长规则的方法,但这种方法具有一定的局限性,一旦某条网络的拓补不符合规律,将出现异常。本文以朋友设计的EMMC小卡为例,给出一种相对通用的等长规则设置方法,希望对读者有帮助。

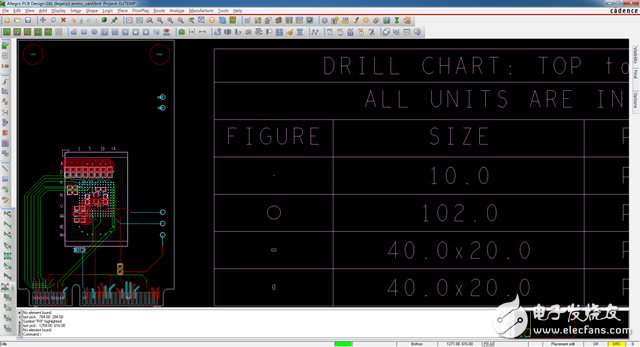

1. 本例中需要实现PCI-e金手指到EMMC芯片等长,包括D0-D7,CLK,CMD这10条网络。查看各条网络,确认是否存在串联匹配电阻。本例中,仅在时钟线上存在,如下图的高亮器件。

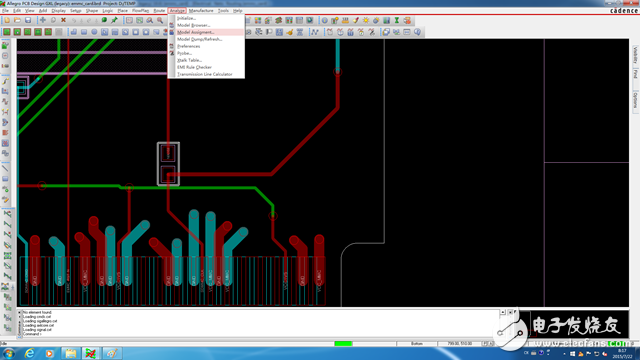

2. 为串联匹配电阻分配仿真模型,这样做的目的只有一个:建立Xnet。因为我们要实现的是金手指到达EMMC芯片的引脚等长,所以必须将串联匹配电阻的两端网络视为同一条。点击Analyze—>Model Assignment,如下图,

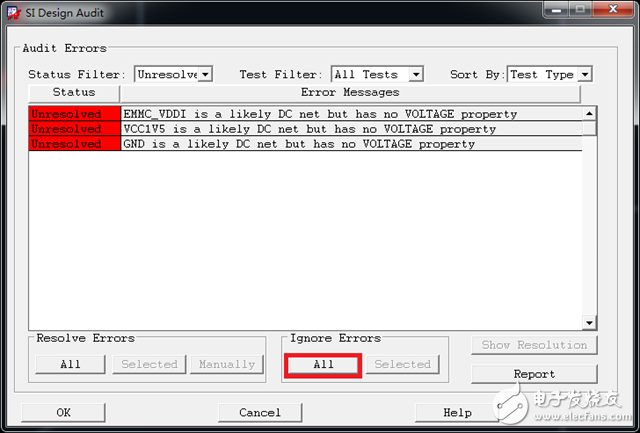

3. 在16.6版本中会弹出一个对话框,就是一些设计错误,直接点击Ignore Errors下面的“All”,然后再点击“OK”即可,如下图。

4. 勾选右侧Find窗口中的Symbols,如下图。

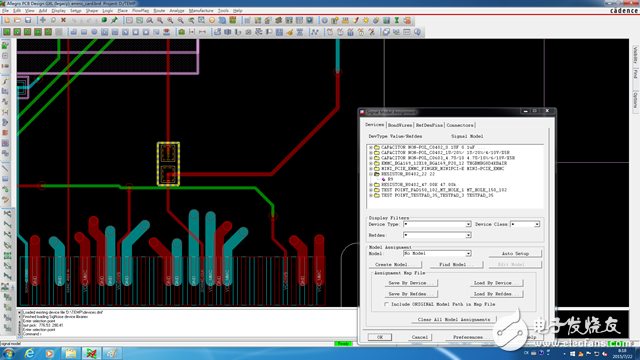

5. 点击时钟线上的串联匹配电阻R9,会出现Signal Model Assignment的界面,如下图。

6. 点击“Create Model,如下图。

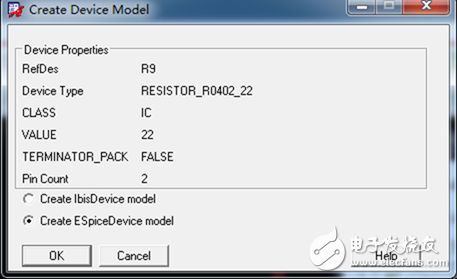

7. 在弹出的Create Device Model对话框中点击“OK”,如下图。

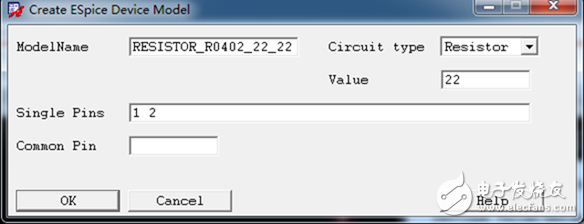

8. 在弹出的Create ESpice Device Model对话框中点击“OK”,如下图。

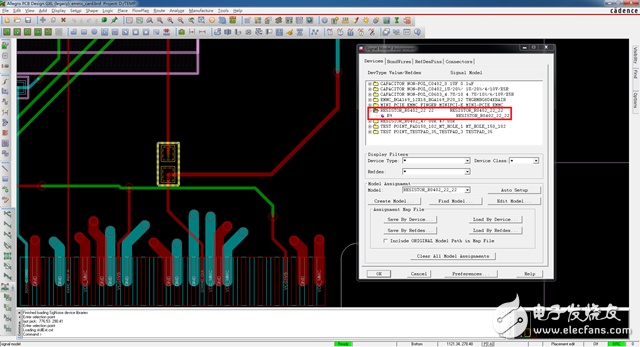

9. 此时返回Signal Model Assignment界面,发现R9已具备Model,如下图。

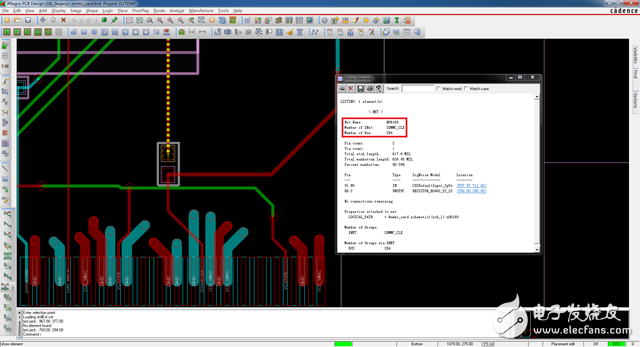

10. 点击Show Element快捷按钮,选中EMMC CLK网络,发现已具备Xnet,如下图。

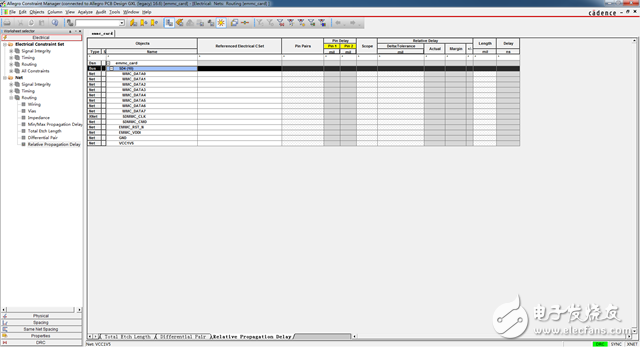

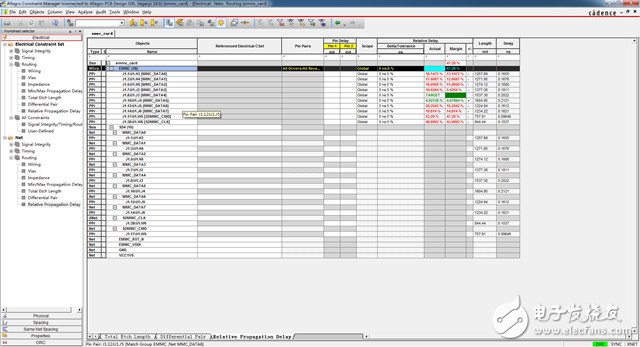

11. 接下来就是创建Match Group,即等长组。点击Constrain Manager图标,在弹出的Constrain Manager界面中,点击左侧的Electrical类别下的Relative Propagation Delay,右侧出现相对传输延迟规则,可以看到EMMC CLK网络作为Xnet出现在其中,如下图。

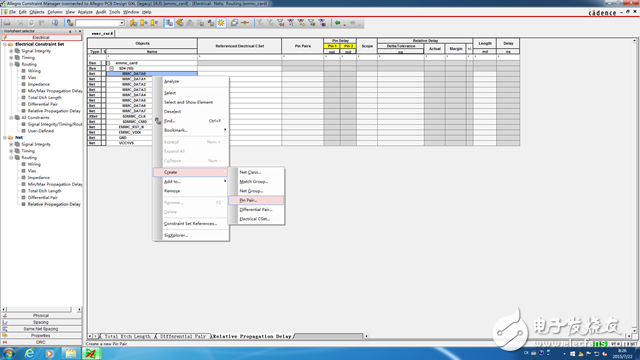

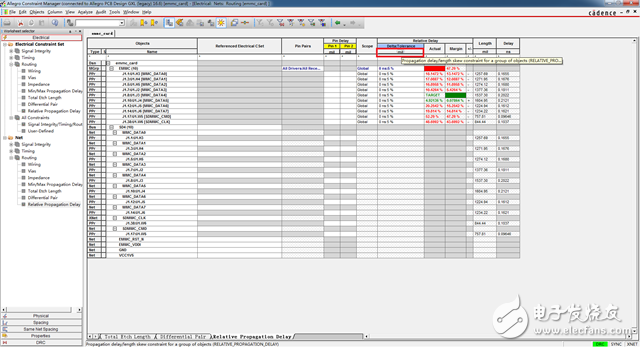

12. 在进行这步操作之前, 笔者再次强调我们要实现金手指到EMMC芯片引脚的等长,即pin到pin的等长,每条网络可以视为一对Pin Pair。在任意一条网络上点击右键Create Pin Pair,如下图。

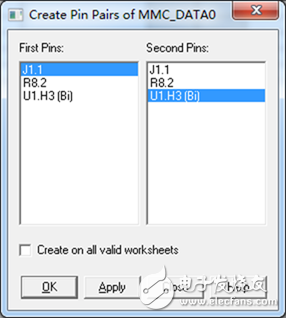

13. 在弹出的Create Pin Pairs of MMC_DATA0对话框中分别选择需要等长的pin,然后点击OK,如下图。当然,我们选择金手指(J1)和EMMC芯片(U1)的引脚,而不是上拉电阻(R8)。

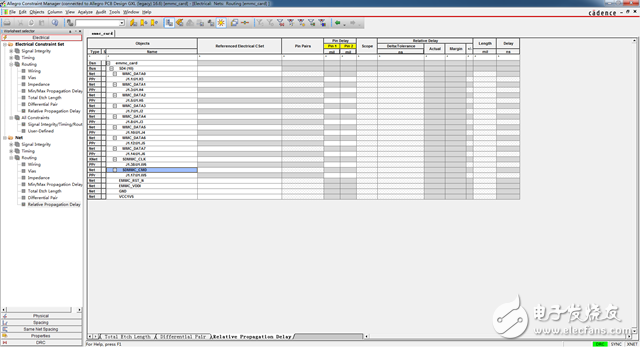

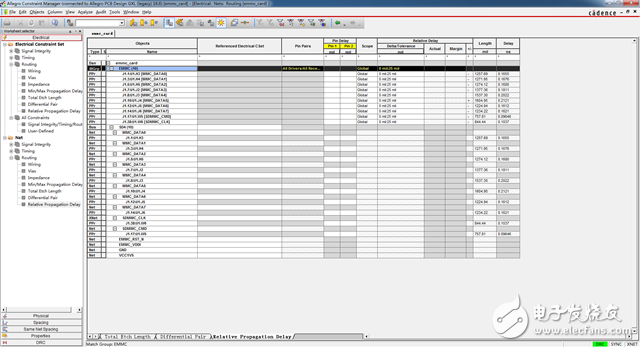

14. 依次处理所有需要等长的网络,完成后如下图所示。

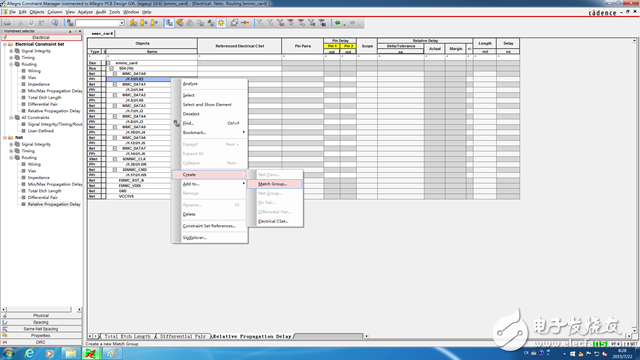

15. 在任意一对pin pairs上点击右键—>Create—>Match Group,如下图。

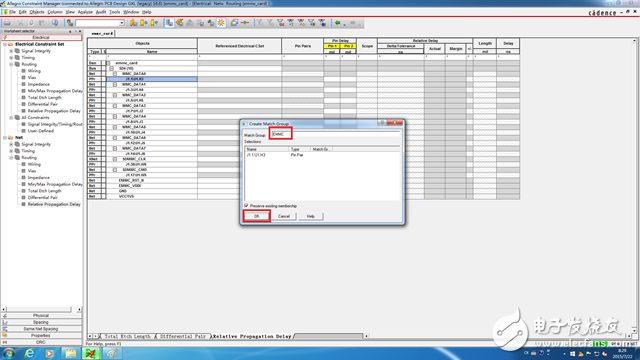

16. 在弹出的对话框中输入名称EMMC,然后点击OK,如下图。

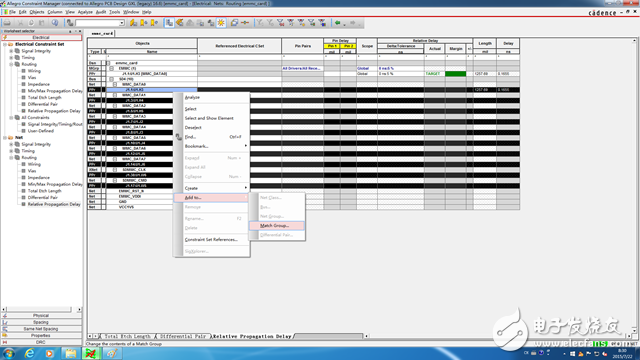

17. 按住Ctrl,依次选择需要等长的pin pair,然后点击右键—>Add to—>Match Group,如下图。

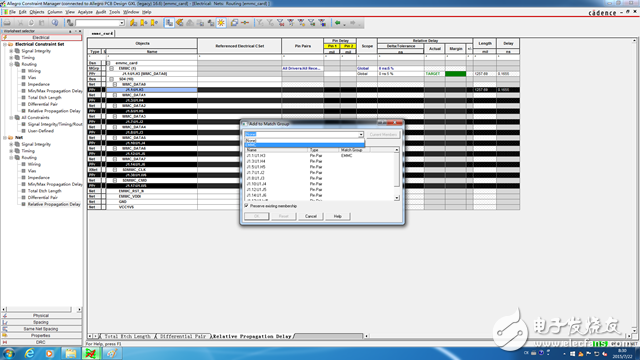

18. 在弹出的对话框中点击下拉箭头选择刚刚创建的EMMC,如下图。

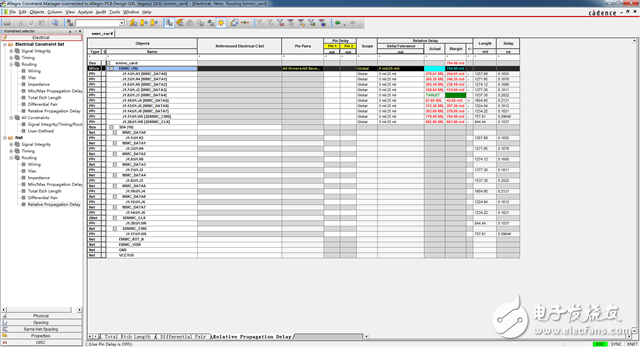

19. 回到Constrain Manager界面,可以看到Match Group已正确建立,如下图。

20. 但默认是以时间做等长单位,不符合一般习惯,改为mil。点击“ns”,在弹出的对话框中选择“mil”,如下图。

21. 在MGrp中的EMMC名称所在一行与Delta:Tolerance所在一列的交叉位置输入等长条件“0:25”,即Delta为0,Tolerance为25,此时看到已变成mil单位,如下图。

22. 在MGrp中的EMMC名称上面点击右键—>Analyze,看到当前的等长状态。

至此,EMMC等长设置完成,接下来就是绕等长了,不是本文讨论的内容。本文的核心思想是使用Pin Piars建立等长规则,这种方法相对通用,在Allegro中应用广泛。在这些年使用Allegro进行PCB设计的 过程中,感受很深的一点就是:如果想很好地掌握Allegro,就必须多思考,多练习,举一反三。

-

ALLEGRO 约束规则设置步骤(以DDR 为例).zip2022-12-30 850

-

DDR4布线之allegro约束规则设置综述2021-09-08 2251

-

Allegro如设置等长线规则2020-08-10 2759

-

Allegro PCB设计时等长设置的一些方法与技巧解析2018-11-27 2637

-

allegro_差分线等长设置2016-02-22 2350

-

allegro中 ddr等长设置及绕线的步骤2015-12-28 18886

-

Allegro16.6约束规则设置详解(图文并茂)2015-11-20 3056

-

allegro中等长设置总结2013-12-26 14486

-

求Allegro电气规则设置?????2012-06-12 6142

-

allegro规则设置里常见缩写的含义2011-11-22 6247

-

教您在Allegro中设置走线等长进阶2010-06-28 31054

-

用allegro使二条时钟线等长的设计置2010-06-21 2005

-

allegro16.2过孔设置方法2010-03-18 1080

全部0条评论

快来发表一下你的评论吧 !