使用Cadence绘制PCB流程(个人小结)

电子说

描述

之前使用过cadence画过几块板子,一直没有做过整理。每次画图遇到问题时,都查阅操作方法。现在整理一下cadence使用经历,将遇到问题写出来,避免重复犯错。

使用软件版本号:Cadence 16.6

一、SCH原理图设计

1.1原理图设计

1.2标注、DRC电气规则检测

1.3网络表netlist生成 (设置元件封装)

二、PCB绘制

2.1零件库开发

零件库开发包括:1、创建焊盘 2、创建零件封装

2.1.1 pad结构和零件文件类型

在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。元件封装大体上分两种,表贴和直插。针对不同的封装,需要制作不同的Padstack。首先介绍Pad焊盘的结构,详见下图:

pad焊盘结构

1. Regular Pad,规则焊盘。

● Circle 圆型

● Square 正方型

● Oblong 拉长圆型

● Rectangle 矩型

● Octagon 八边型

● Shape形状(可以是任意形状)。

2. Thermal relief,热风焊盘。

● Null(没有)

● Circle 圆型

● Square 方型

● Oblong 拉长圆型

● Rectangle 矩型

● Octagon 八边型

● flash形状(可以是任意形状)。

3. Anti pad,隔离PAD。

起一个绝缘的作用,使焊盘和该层铜之间形成一个电气隔离,同时在电路板中证明一下焊盘所占的电气空间。

● Null(没有)

● Circle 圆型

● Square 方型

● Oblong 拉长圆型

● Rectangle 矩型

● Octagon 八边型

● Shape形状(可以是任意形状)。

4. SOLDERMASK:阻焊层,作用:为了避免相邻铜箔导线短路和减缓铜箔氧化,在PCB板覆盖绿油解决问题。如果将绿油覆盖待焊盘上,则焊盘无法焊接。所以提出阻焊层概念,即在覆盖绿油位置 为焊盘开个窗口,使绿油不覆盖窗口(该窗口的大小必须大于焊盘尺寸)。可以理解成去阻焊层(即使用模具上绿油时,将焊盘位置遮挡,其他位置上绿油)

(1)负片时,Allegro使用Thermal Relief和Anti-Pad;(VCC和GND层)

(2)正片时,Allegro使用Regular Pad。(信号层)

负片的Thermal Relief 负片的Anti-Pad 正片的Regular Pad

5. PASTEMASK:胶贴或钢网。应用:是机器贴片时要用的,是对应所有贴片元件的焊盘的,大小与toplayer/bottomlayer层一样,是用来开钢网漏锡用(即上焊锡膏)的。

6. FILMMASK:预留层,用于添加用户需要添加的相应信息,根据需要使用。

零件文件类型说明:

后缀名“.pad” 的文件:焊盘文件

后缀名".psm"的文件:零件的封装数据

后缀名“.fsm”的文件:Flash焊盘文件,应用电路板的内层的电源和GND作为负片。

后缀名“.dra"的文件:绘图文件,可以直接用Allegro PCB Editor打开。

后缀名“.ssm”的文件:自定义焊盘图形数据文件

2.1.2 焊盘制作

目前焊盘制作方法由allegro的Pad_Designer或第三方软件FPM (Allegro封装生成器0.08的功能)生成焊盘。下面两种方式介绍焊盘制作,以c155h50m165通孔焊盘为例说明。

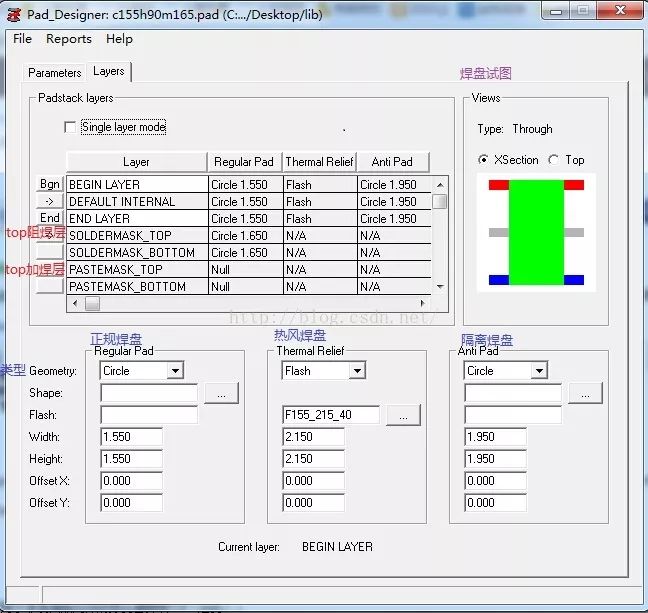

第一种方法:使用 Pad Design 制作焊盘, 打开Pad_Designer软件,详见下图

Padstacks中

1)Type主要有三种:

Through:穿孔,一般用于非表面贴元件的穿孔管脚或Via(过孔)。

Blind/Buried:盲孔和埋孔,分别指顶层和底层都看不到的内部孔,和只有顶层或底层能看到而另一层是不可见的孔。他们也是用于制作Via。

Sigle layer:单层,用于制作表面贴元件件的管脚。

注:在candence 16.6版本中,不可以手动设置。Type类型根据你设计的Pad定义(即Layers中设置)。如果是贯穿就会显示through,表面型就是single。

2)Units是尺寸的单位,一般选择Mils或Millimeter(公制:毫米),根据方便选择。换算关系:100mil =2.54 mm 1mil=0.00254mm

3)Multiple Drill:设置钻孔数量等

4)Drill/Slot hole:钻孔信息,选择类型(Hole Type)、是否Plate和钻孔尺寸等。

5)Drill/Slot symbol:钻孔符号,在PCB制作时会显示出来,可以用来标识不同的钻孔。这里就是选择一下形状和大小尺寸。

在Layers标签下:

配置焊盘在各层的形状和尺寸。对于表面贴元件,一般勾选SingleLayer Mode,只配置单层信息。

Layer有很多层:

Ø BEGIN LAYER :定义焊盘在PCB板中的起始层,一般指TOP层。

Ø DEFAULT INTERNAL :定义焊盘在PCB板中处于顶层和底层之间的各层(可能是电源层、地层、信号层)。

Ø END LAYER:定义焊盘在PCB板中的结束层,一般指Bottom层。

Ø SOLDERMASK_TOP和SOLDERMASK_BOTTOM分别表示顶层阻焊层和底层阻焊层。

Ø PASTEMASK_TOP和PASTEMASK_BOTTOM分别表示顶层助焊层和底层助焊层。

注: 焊盘参数设定的推荐值

1、过孔径与正规焊盘的外径关系:焊盘的外径 = 过孔径 +0.6mm

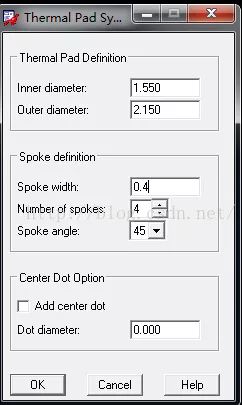

2、热风焊盘与正规焊盘的外径关系:热风焊盘的外径=正规焊盘外径 + 0.5mm;热风焊盘的内径= 正规焊盘外径;

开口宽度= 0.4mm(经验值)

还有一种理解:开口宽度=DRILL SIZE × Sin30° ,同时开口宽度,则要根据圆周率计算一下,保证连接处的宽度不小于10mil(0.254mm),例如过孔径0.9mm,则开口宽度= 0.9mm x 0.5 =0.45mm

3、隔离焊盘与正规焊盘的外径关系:隔离焊盘的外径=正规焊盘外径 + 0.5mm

3、阻焊层外径与正规焊盘的外径关系:阻焊层外径 =正规焊盘外径 + 0.1mm

4、加焊层外径与焊盘的外径关系:加焊层外径 =正规焊盘外径

flash焊盘制作(以f155_215_40为例说明)

NO1、在PCBEdior下,运行File|new 进入下面界面

NO2、配置坐标、网格等环境

NO3、设置焊盘,即Add|flash

NO4、点击File|save,保存。

第二种方法:使用第三方软件FPM

2.1.3 pad命名规则

1、Pad焊盘命名规则

圆形焊盘:c焊盘外径h过孔径m阻焊层圆形外径,

例如:c300h140m310表示 焊盘外径:3.00mm,过孔径:1.40mm,阻焊层外径:3.10mm

注:过孔焊盘 应用零件封装中机械定位孔(不需要电气连接),例如c0h300表示焊盘0mm,过孔3.00mm

正方形焊盘:s焊盘外径h过孔径m阻焊层正方形长度,

例如:s300h140m310表示 正方形焊盘长度:3.00mm,过孔径:1.40mm,阻焊层正方形长度:3.10mm

正方形焊盘:r焊盘长度_宽度m阻焊层长度_宽度

例如:r130_85m140_95表示正方形焊盘长度1.30mm 宽度0.85mm,阻焊层长度1.40mm 宽度0.95mm

2、Flash焊盘命名规则

Flash焊盘:f内径_外径_开口

例如:f185_225_40表示flash焊盘内径1.85mm 外径2.25mm,开口宽度0.4mm

3、VIA过孔命名规则

VIA过孔:v焊盘外径h过孔径

例如:v75h40 表示焊盘外径0.75mm,过孔径0.4mm,阻焊层0mm(即使用阻焊油堵孔)

2.1.4 零件封装制作

个人经验:通过变换网格间距和中心原点,来快速制作零件封装。

2.2 PCB板基本信息设置

PCB板子尺寸、层叠结构、布线区域。绘制板子outline外框、Rout keepout禁止布线区、定位孔并标注尺寸。

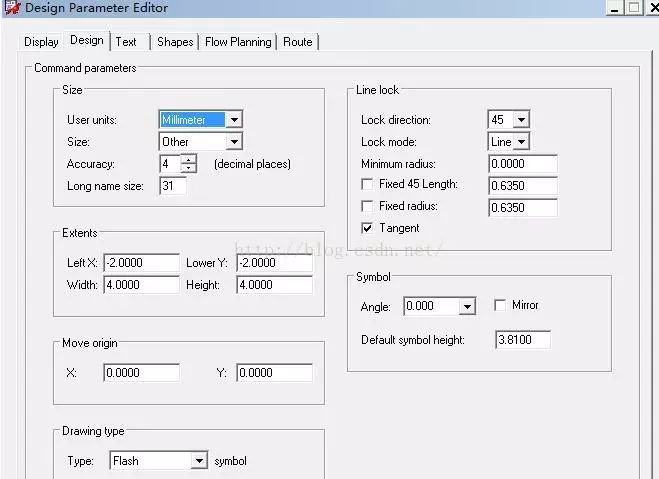

第一步:创建后缀名 ".brd"的PCB文件。

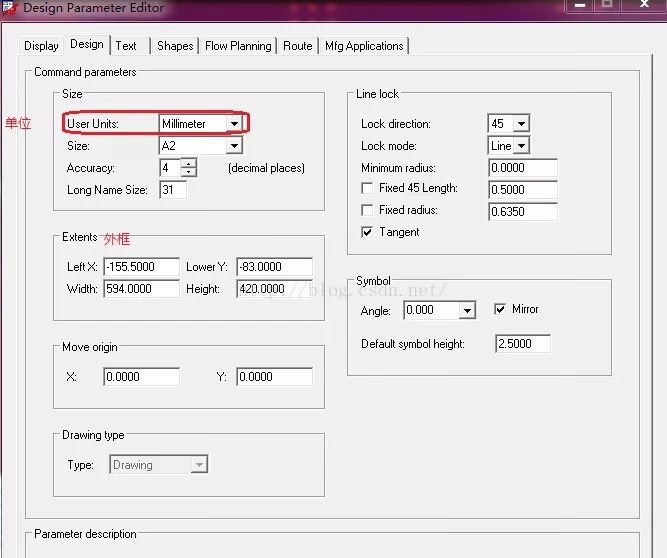

第二步:设置工作区尺寸,设置如下图(注意:建议使用公制Millimeter)

工作尺寸设置

第三步:绘制板子outline外框和倒角

使用Add | Line、Add | rectangle或Steup |outline| board outline命令绘制电路板的外框线。

具体步骤:

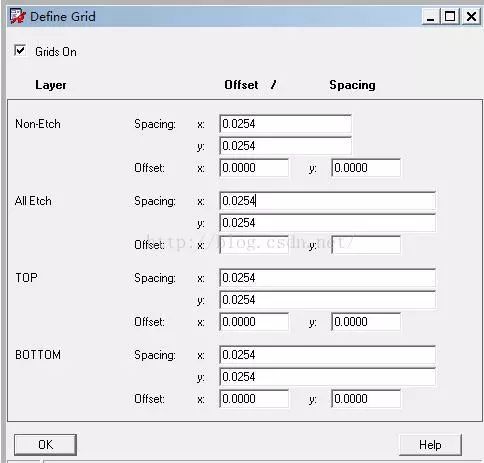

1)根据需要绘制外框设置 网格间距。例如PCB外框是120x200,则网格设置 X= 120 Y=200

2)选择Add | line命令,激活右侧 Options 选项卡中 Active Class and Subclass下拉列表选择 Board Geometry和 Outline选项,表示添加线属于电路板外框。

3)根据网格间距 画外框

4)外框倒角方式有两种:1、45度倒角(Chamfer选项)2、圆弧倒角(Fillet选项)

● 选择Manufacture | draftl Fillet命令

● 1.在右侧控制板中Radius修改成;2.表示倒角圆弧半径约为2mm

● 分别单击需要 矩形外框的两边,即可倒角。

注:如使用Add | rectangle,则不支持上述倒角操作。Add | Line支持上述倒角操作。

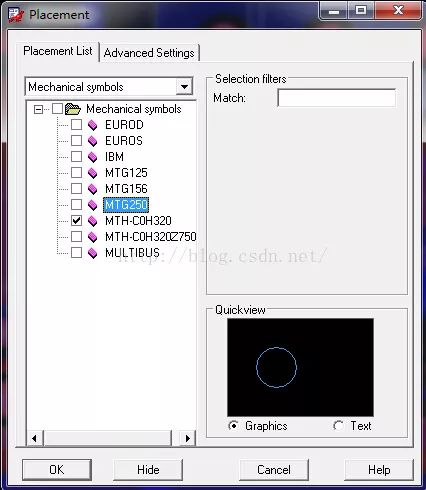

第四步:添加定位孔和光学定位孔

具体步骤如下:

1)根据定位孔位置,设置网格间距。

2)Place|Manually命令,弹出Placement窗口

3)打开Advanced Setting选项卡,选择LIbrary复选框(设置显示 lib库元件)

4)打开Placement List选项卡,选择 Mechanical Symbols下拉边框选择 定位孔,然后点击Hide放置定位孔。具体详见下图。

第五步:设置禁止布线区和禁止元件放置区。

为了避免焊接或安装过程中伤及板上的走线,所以电路板的走线与板边有一定距离(建议:3mm)。设置Route Keep out禁止布线区和 Package keepout,具体步骤:

方法一、单击Shape add Rect 命令,激活右侧 Options 选项卡中 Active Class and Subclass下拉列表选择 Rout Keepout选项(具体详见下面)。

激活后,绘制Route Keep out。

方法二、(使用画线):选择Setup | Areas | Route Keepout,然后绘制Route Keep out 即可。

第六步:设置层叠结构。

在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层,6层,还是更多层数的电路板。确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。本节将介绍多层PCB板层叠结构的相关内容。

1、使用多层板好处:

1)利用内电层的大铜膜来为信号层提供屏蔽。同时高速信号可以走中间信号层 ,通过相邻两个内电层的铜膜可以为高速信号传输提供电磁屏蔽,同时也能有效地将高速信号的辐射限制在两个内电层之间,不对外造成干扰。

2)多个接地的内电层可以有效地降低接地阻抗。例如,A信号层和B信号层采用各自单独的地平面,可以有效地降低共模干扰。

3)降低布线难度

2、Layer Type层的类型

Conductor 信号层的类型

Dielectric 电介质,一般选用FR-4

Plane 地层和电源层的类型,一般应用内电层

DRC as Photo File Type

Positive 正片

Negative 负片

(Positive )正片:简单地说就是,在底片上看到什么就有什么。

(Negative)负片:正好相反,看到的就是没有的,看不到的就是有的。

下面通过4层板的例子来说明如何优选各种层叠结构的排列组合方式。 常用的4层板来说,有以下几种层叠方式(从顶层到底层):

显然,方案3电源层和地层缺乏有效的耦合,不应该被采用。

那么方案1和方案2应该如何进行选择呢?

一般情况下,设计人员都会选择方案1作为4层板的结构。选择的原因并非方案2不可被采用,而是一般的PCB板都只在顶层放置元器件,所以采用方案1较为妥当。但是当在顶层和底层都需要放置元器件,而且内部电源层和地层之间的介质厚度较大,耦合不佳时,就需要考虑哪一层布置的信号线较少。对于方案1而言,底层的信号线较少,可以采用大面积的铜膜来与POWER层耦合;反之,如果元器件主要布置在底层,则应该选用方案2来制板。

如果采用如图11-1所示的层叠结构,那么电源层和地线层本身就已经耦合,考虑对称性的要求,一般采用方案1。

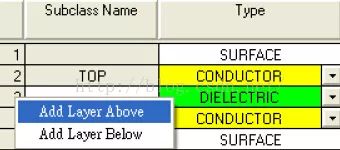

3、设置层叠步骤及方法

选择Steup | Cross-section命令或

1)进入Layout Cross Section窗口,添加层操作如下

2) 设置每层名字 TOP、GND、POWER、BOTTOM

3)设置层类型,总共有Conductor 信号层、Dielectric 电介质层、Plane地层和电源层。

4)设置每层厚度,主要是外层厚度(信号层)、内层厚度和电介质层厚度。1oZ=35um,线宽1mm,可以通过2A电流。

注意:设置完每层厚度后,观察PCB总体厚度。

5)Artwork光绘文件是否负片输出,一般内电层使用负片输出,减少数据文件大小。上述5步设置,详见下图:

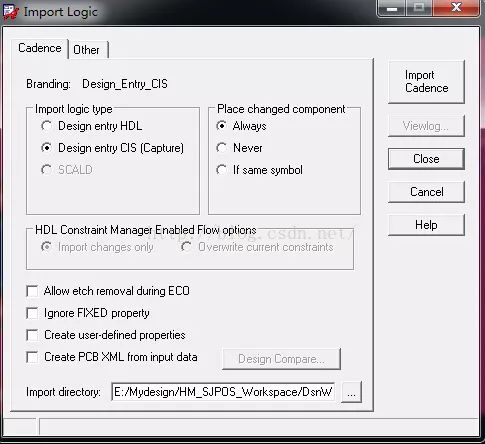

2.3导入netlist网表

在PCBEdior下,操作File | Import | logic进入下面界面:

在导入路径中选择 原理图中生成netlist后,单击“ Import Cadence”导入网表。根据导入提供信息,判断导入是否成功。

2.4设置约束规则

约束规则作用:allegro设计软件优势是高速信号PCB设计,而高速信号需要 考虑信号完整性(信号需要等长)、差分信号等。

当约束设置完成后,PCB工具会自动根据定义的约束对设计进行检查,不合符约束的地方会用DRC Markers 标记出来。

操作步骤:

● 选择“Setup-> Constraints->Constraint Manager”,启动约束管理器

● Allegro中规则分为两类:DefaultConstraint和Special Constraint。用户既可以修改默认规则,还可以创建新规则

● 约束设置方法:1 确定约束类型 2 创建或修改约束设置 3 分配约束

在PCB 设计中,设计规则主要包括:Electrical时序规则、物理规则、间距规则、相同网络名间距规则、properrties性能规则共4个部分。下面重点介绍以下3个规则设置。

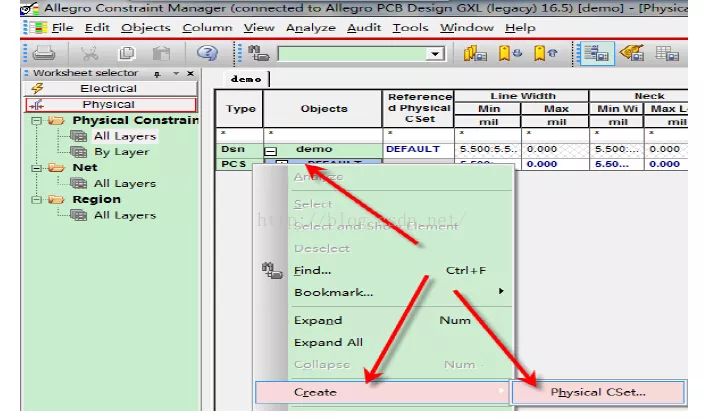

2.4.1 Physical物理规则条件设置

点选Physical Constraint Set 即可出现Default 的Physical 相关设定值,如Line Width线宽、Neck width..、过孔等(对于BGA封装元件,需要使用Region区域约束规则设置)。 Physical物理规则可以使用Defaul约束t规则,也可以新建约束规则。

1)设置Default约束规则:

2)新建约束规则方法:以新建电源 PWR为例说明

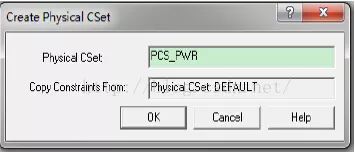

3)设置约束参数:设置线宽、过孔等

线宽:一般设置Line Wdith min、Neck min Width

过孔:物理规则设置里面有一栏是Vias,点击即可设置,如下图所示

4)分配约束:

对于一般net线宽,使用默认DEFAULT线宽;而有特殊要求线宽单独设置。例如:电源相关net,先建立一个CLS_POWER的类,然后将所有电源相关net添加进去,一起设置线宽约束。

区域约束规则:这里不详述,具体参见詹书庭 的<< Allegro16.6 约束规则设置详解.pdf>>

2.4.2 Spacing间距规则条件设置

1、设置间距值约束规则

进入约束管理器,单击 Spacing,再点击AllLayers,如下图所示。右边有一个DEFAULT 就是默认规则,我们可以修改其值。也支持定义特殊间距约束,点选Default按鼠标右键,执行Create-Spacing CSet。

间距推荐值:待完善

1)line to line:根据3W原则,走线之间的间距不应小于两倍走线宽度。对于特殊的信号,如时钟走线,应适当增加走线的间距,至少为走线宽度的两倍,如果可以最好用地线隔离。

2)line to hole:可参考line to line原则

2)line to shape:可参考line to line原则

4)shape to shape:这个间距需要考虑两个shape之间电压差。电压差低于24V,不低于0.5mm即可。具体《距离及相关安全要求》

2、对net设置间距约束

一般间距使用默认DEFAULT。对间距有特殊要求,建立新的间距规则,然后对其net分配该规则。详见下面电源间距约束设置。

2.4.3 Electrical电气规则条件设置

Electrical电气规则主要关注:差分信号约束规则、等长约束规则。下面以差分和等长为例说明:

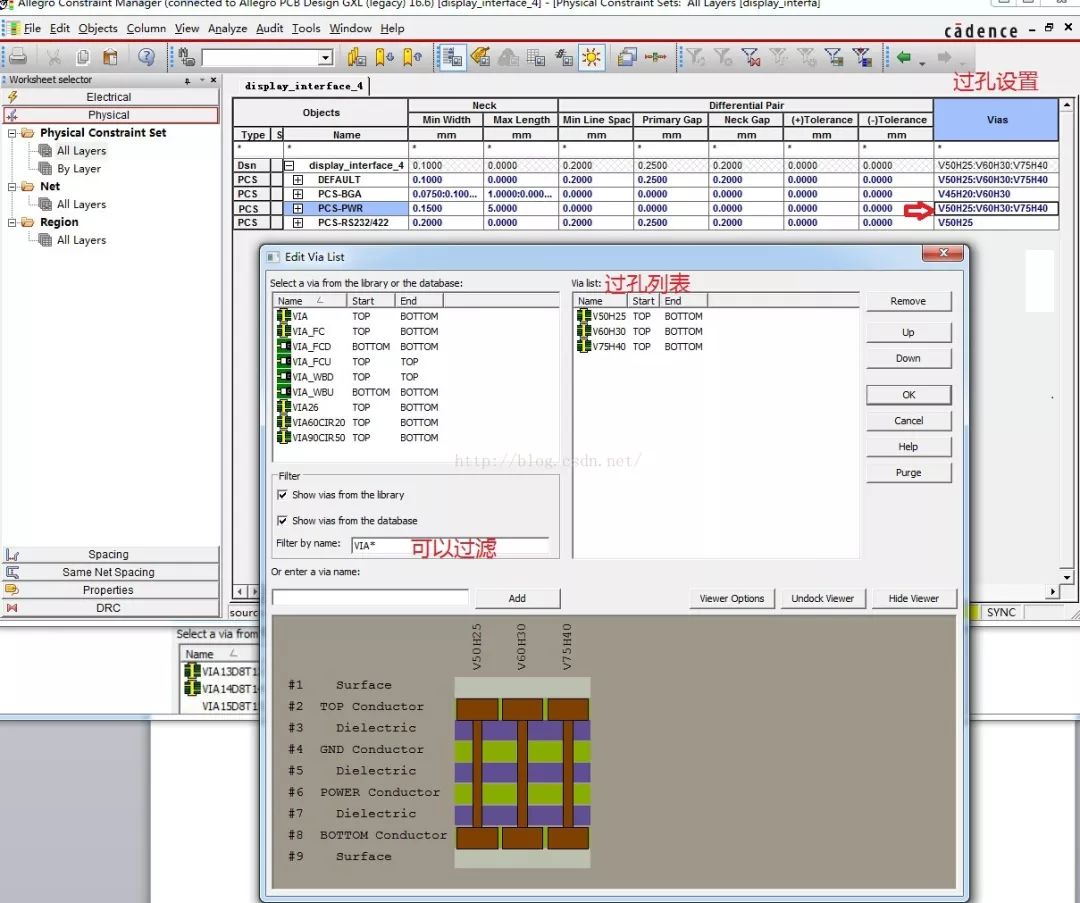

2.4.3.1差分信号约束规则

先说差分线相关参数

1、 Coupled Tolerance:两条差分线间距的误差值

2、 Min Line Spacing: 两条差分线 的最小间距

3、 Primay Gap: 两条差分线优先线间距(边到边间距)。

4、 Primary Width :差分线优先线宽

5、 Line Width:差分线的线宽(在Physical Constraint Set 设置)

6、 Neck Gap :差分对Neck模式下的线间距(边到边间距),用于差分对走线在布线密集区域时切换到Neck值。

7、 Neck Width:差分对Neck模式下的线宽,用于差分对走线在布线密集区域时切换到Neck值。

8、 Dynamic Phase:动态相位检查

9、 Static Phase Tolerance 这个约束设置了两根差分线之间线长差值,单位是mil或ns

10、Uncoupled length:该约束限制了差分对的一对网络之间的 不匹配长度。

设置步骤如下:

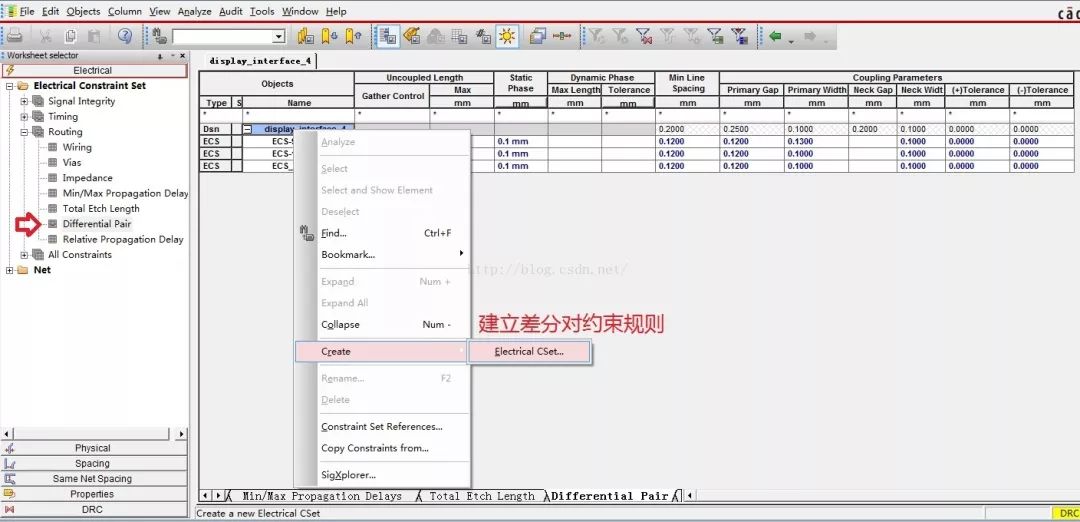

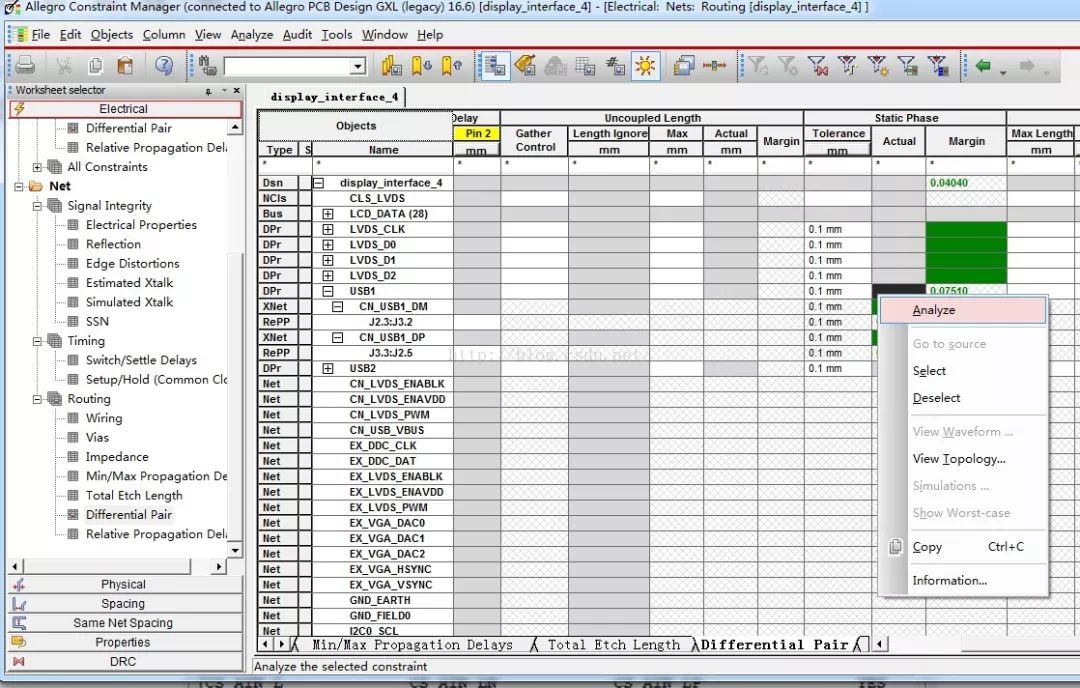

1、 建立差分规则并设置参数:打开约束管理器,定位到Routing | Differential Pair 下,如下图所示。

参数设置

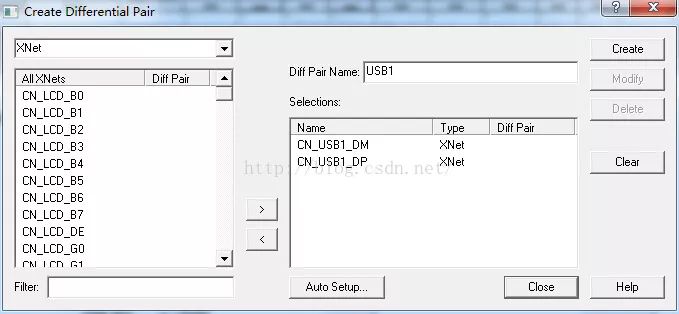

2、 建立差分对。以USB为例,选择中CN_USB1_DM和CN_USB1_DP,右击 Creat --->DifferentialPair

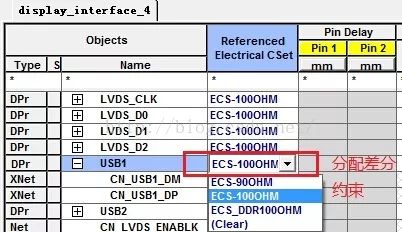

3、分配约束规

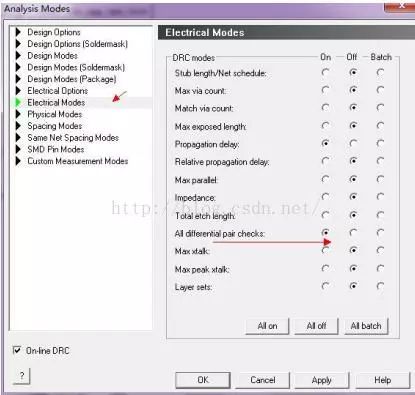

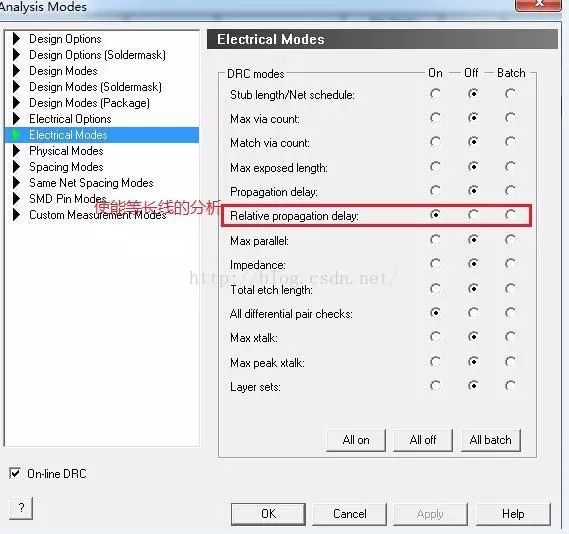

4、打开差分对检查。执行 Analyze-Analysis Modes,详见下图:

Analyze分析差分线

2.4.3.2等长约束规则

高速布线中等长设置是经常使用的约束规则,在Allegro中等长设置使用相对延时约束规则。在实际使用过程遇到:同一个Net(直接连接的)和 不同Net(XNet)情况。

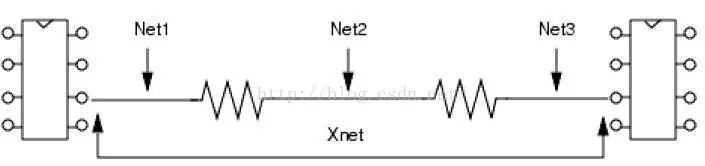

参考:Allegro_xnet_setup.pdf和于博士《Cadence入门手册》等。在这之前首先介绍一下一个新个概念Xnet,见下图:

我们把连续的几段由被动元件(如电阻,电容或电感)连接的net合称为一段Xnet.。Allegro中有两个常用的走线长度设置

,PROPAGATION_DELAY, RELATIVE_ PROPAGATION_DELAY 都只能针对同一Net设置。

Xnet应用实例:

现在要求U1 到U2 的走线Net*A + Net*B等长, 误差为+/-20Mil,最简单的方式就是分别设置Net*A等长和Net*B等长,误差各为+/-10Mil, 这样是可以达到要求,不过会加大Layout工程师绕线的难度,因为可能Net*A部分空间比较大有足够的绕线空间,而Net*B部分没有空间绕线,所以就比较难达到要求.如果一种设置能把Net*A与Net*B相加,然后再做等长比对,这样就可以解决问题了,好的就是Allegro都早为这些问题考虑过了,只要把Net*A与Net*B设置为一个Xnet问题就解决一半了.

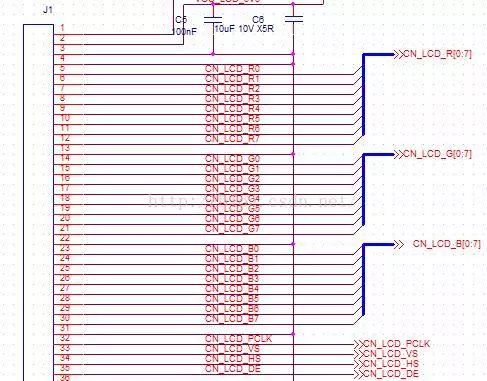

1、 同Net等长设置

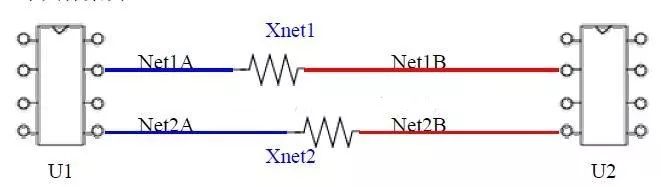

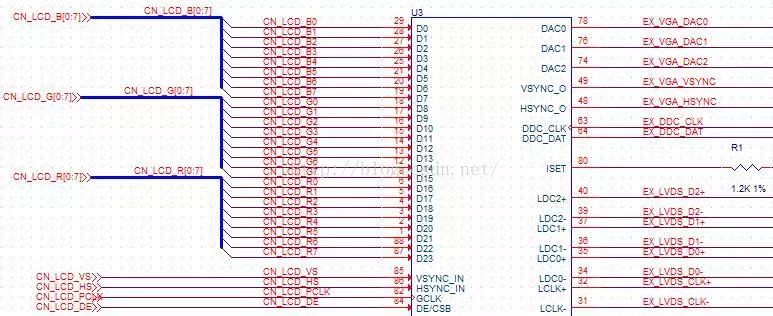

下面以LCD板实例说明一下,原理图如下:

原理图1

原理图2

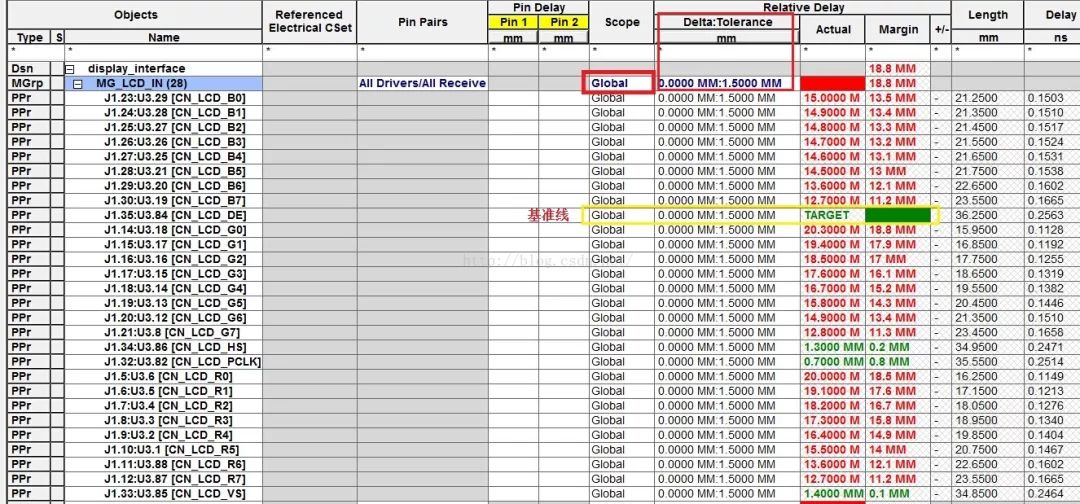

LCD接口数据线、信号线需等长,即原理图J1同U3的CN_LCD_B[0:7]、LCD_B[0:7]、LCD_B[0:7]、CN_LCD_VS、CN_LCD_HS、CN_LCD_PCLK、CN_LCD_DE等长。

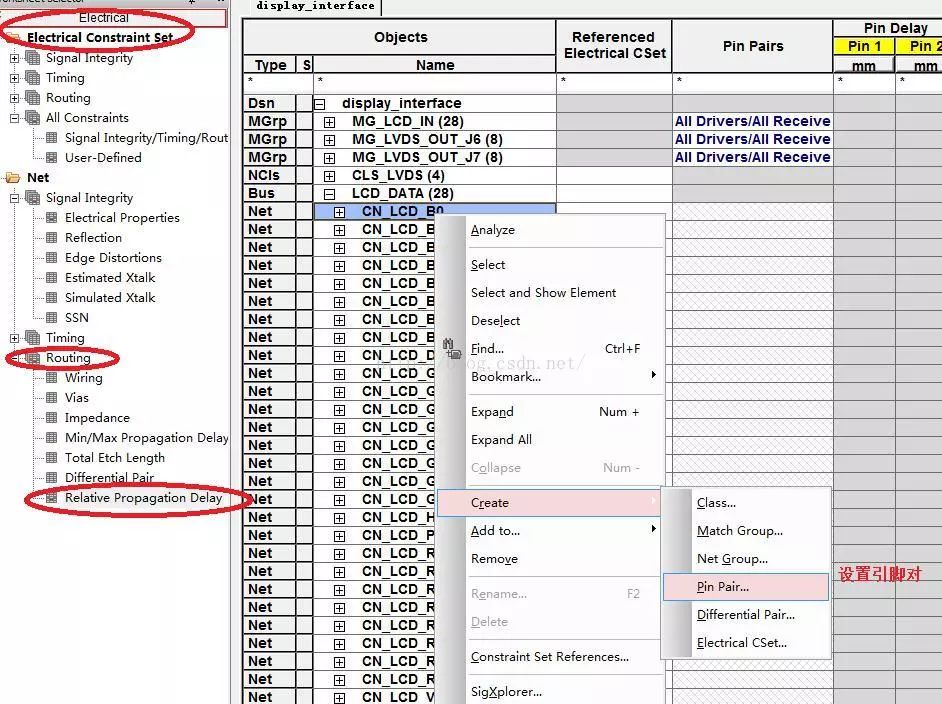

第一步:设置引脚对(pin pair)。在约束管理器Electrical|Net |Routing|Relative Propagation Dleay界面下操作:

依次设置所有需要等长引脚,即LCD_DATA[28] 总线上引脚。

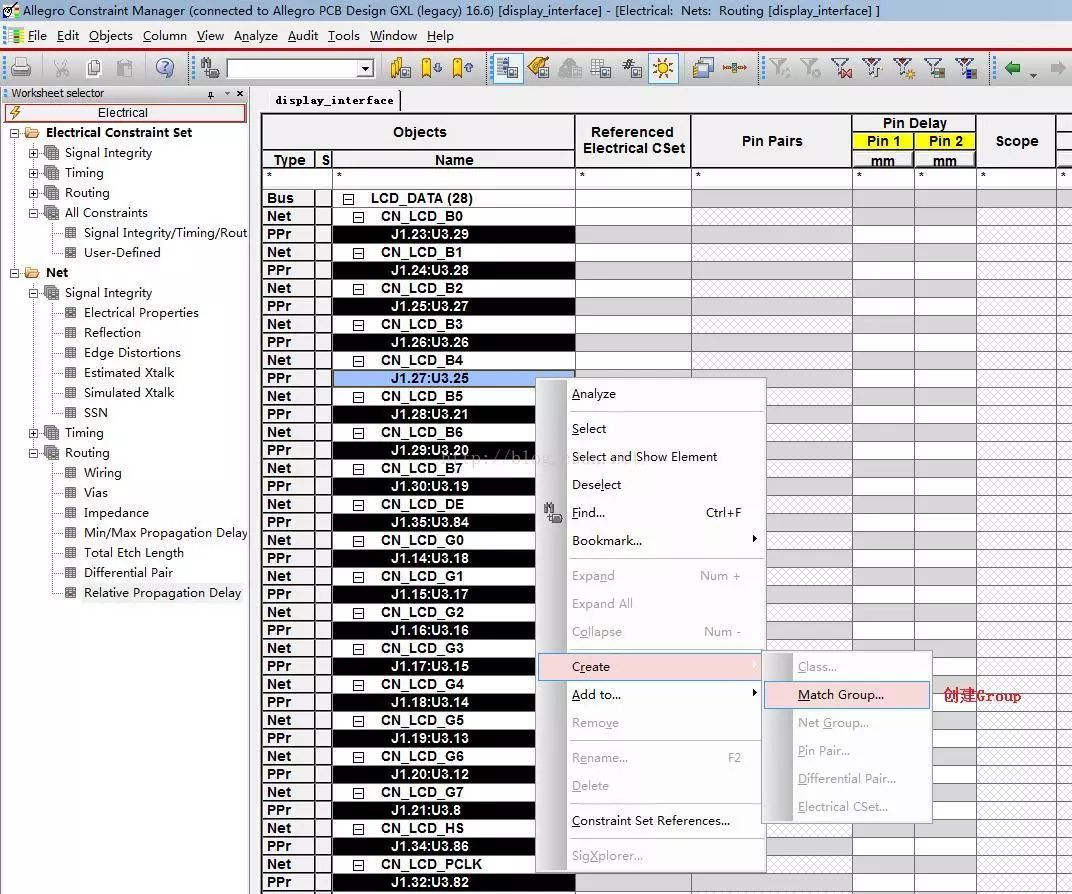

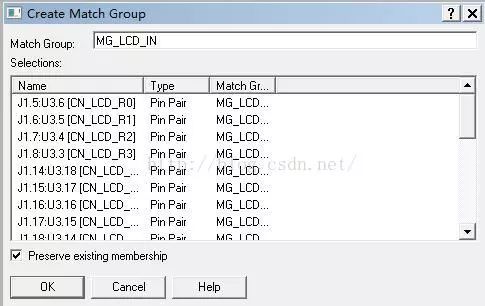

第二步:创建match group。将所有设置等长的网络创建好的管脚对后,选中管脚对,右键选择create-match group。

第三步:设置等长相关参数。主要设置参数如下图所示。

1)使能等长线的分析

2)设置等长基准线和+/-误差。下面以设置CN_LCD_DE为基准线,正负误差:0-1.5mm

参数说明:

1、Scope选择Global。Scope:可以选择Local和global。Local意为仅比较同一Net或XNet内的管脚对,Global意为比较同一Match Group内的所有管脚对。一般选择Global即可。

2、Pin delay:大多是在pin之间的延时不一致时,需要做一个补偿,那就需要设置pin delay,指的是IC包装内部的长度。需要在菜单Analyze -> Analysis Modes填入->Options.勾Analyze选PinDelay开启此功能。打开后,在计算线长时就会包括这段线长。另外pin delay下的Z Axis Delay指的是计算线长时是否考虑Via的长度,设置好了叠层参数后就会加上via的长度。

一般Pin delay 忽略不计。

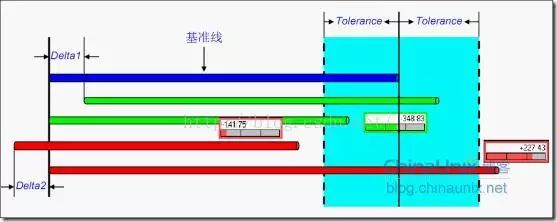

3、 Delta:tolerance:这项控制了match group内的线长差。单位有三种:ns,mil,%;单位%指以目标线的N%为公差。对已经走好的线,以最长值为目标线。

1)Delta指的是基准线比目标线长还是短,长则写入+delta值,短则写入-delta值,和目标线一样长则写入0,计算公差时的基准线便是目标线长加上delta值的结果。一般等长设置中,Delta为0。

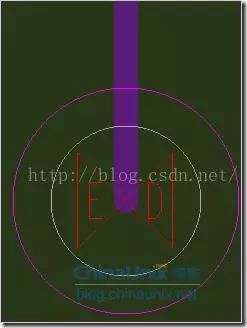

对不满足约束的走线,显示“ED”错误,如图所示。

2)Tolerance值为于基准线的误差,是+/-误差。如果写50mil其实为+50/-50mil误差,实际为100mil的误差。一般设置等长时Delta为0,有特殊需要时可以考虑设置delta值。

注:如何修改等长线束中 基准线???方法如下:

2、设置Xnet与Xnet等长.

2.5布局、布线、铺铜

2.5.1 布局

1、手工摆件:选择Plalce | Manually命令,弹出Placement窗口

2、摆放零件的相关操作

移动零件:选择Edit |Move命令,可在Allegro的右下角Cmd中看到move状态,即可移动零件。打开右侧控制面板Find选项,选择合适项。

旋转零件:首先零件处于move状态,右键选择Rotate。

镜像摆放零件:首先零件处于move状态,右键选择Mirror。

3、使用原理图交互式摆放零件

操作步骤:

1)打开原理图和PCB工程。

2)在原理图中选择Option | Preferences命令,弹出Preferences窗口。

3)打开Miscellaneous选项卡,选择InterTool Communication选项组中Enable InterTool Communication复选框。

4)单击OK按钮,激活Orcad Capture CIS和 Allegro PCB Editor之间的通信程序。

5)在Allegro PCB Editor窗口中选择 Place | Manully命令,弹出Placement窗口。

6)点击原理图元件,此时元件的封装出现在 Allegro PCB Editor工作区。

2.5.2 布线

1、布线准备

1)使用不同颜色显示多个网络:选择Dispaly |Assign color命令,选择右侧面板 Option中分配颜色。

2)设置布线栅格点:选择Setup | Grids命令,弹出栅格窗口。

2、手工布线

控制面板说明:选择Route | Connect, Allegro PCB Edito进入add connect命令状态,单击右侧option,详见下图:

参数说明:

1)line lock下拉列表框:选择走线改变方向时,所用的转角型和角度。

● line:转角处使用直线段

● arc:转角处使用圆弧

● off:走线使用任意方向

● 45:转角方向为45度斜线

● 90:转角方向为90度斜线

2)Miter下拉l列表框“:当line lock选择45时,用于设置 转角处小斜角的尺寸。

3)Line width:显示当前线宽,可以输入修改。

4)Bobble下拉列表框:选择操作,走线遇到障碍(过孔和焊盘)时,其中包括以下四项:

● off:关闭Bobble方式,该方式走线完成忽略障碍物的存在,直接从障碍物穿过,必然导致DRC错误。

● Hug only:遇到障碍物时采取抱紧障碍物的方式, 与障碍物的间距采用Spacing规则中设置的间距值。

● Hug preferred:优先选择抱紧,如果没有空间走线,则采用推挤方式。

● Shove Preferred:优先选择推挤,如果无法推挤,则采用抱紧方式。

5)Shove Via下拉表框:

3、群组布线

4、差分布线

5、蛇形走线

6、修线

2.5.3铺铜

1、内电层铺铜

2、外层铺铜

3、编辑shape边界

4、指定网络

5、手工挖铜void

6、删除孤岛

7、铺静态铜皮

8、合并铜皮

9、分割内电层

2.6设计完善

设计完善包括:

1)添加测试点

2)添加局部光学定位点

3)重新编号发标回原理图

4)设计规则检查(DRC和Unconneted pin检测等)

5)丝印信息处理:1、调整元件丝印信息方向和大小 2、添加板子型号MD、编号SN、时间等 丝印信息

2.7生成钻孔文件

2.7.1 设置钻孔参数

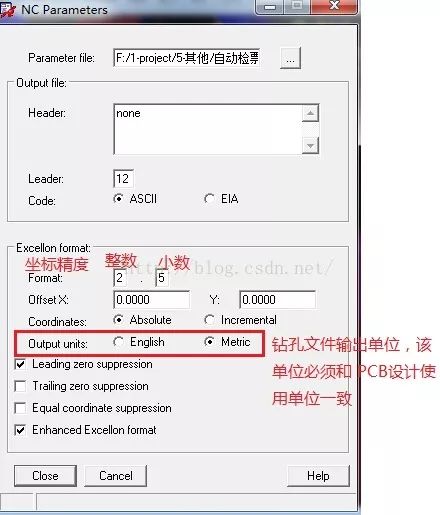

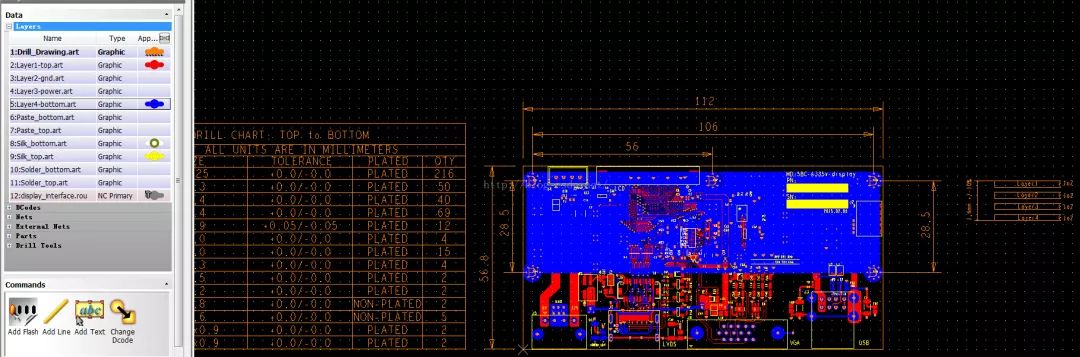

使用NC Parameters设置生成钻孔文件的坐标格式、单位、参数位置和名称参数等。具体设置如下图2.7.1:

图2.7.1 NC参数设置

2.7.2 生成钻孔文件

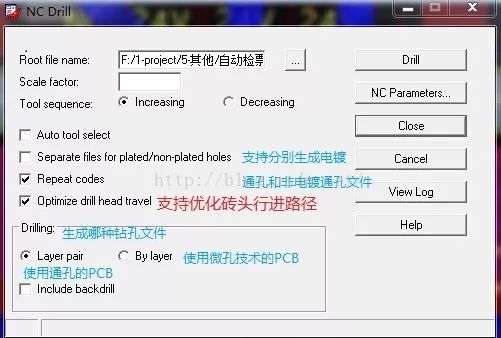

钻孔文件包括PCB板上通孔类引脚和过孔的坐标值,供数控机床使用。生成钻孔文件的操作步骤如下

1)选择Manufacture |NC | NC Drill命令,弹出NC Drill窗口

2)设置如下图2.7.2:

图2.7.2 钻孔文件生成设置

说明:

Root file name文本框:设置钻孔文件保存路径和名称,文件的后缀名".drl"。一般使用默认即可

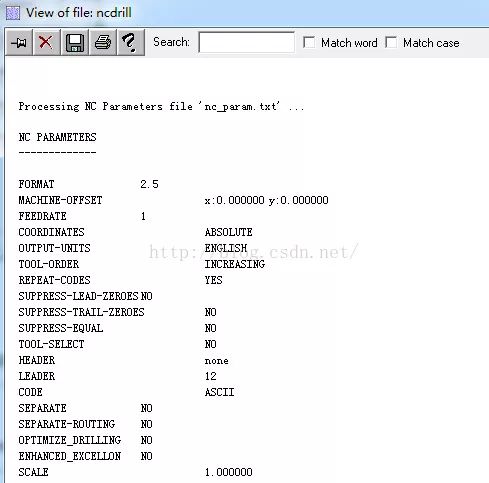

3)单击Drill按钮产生钻孔文件,内容如下图:

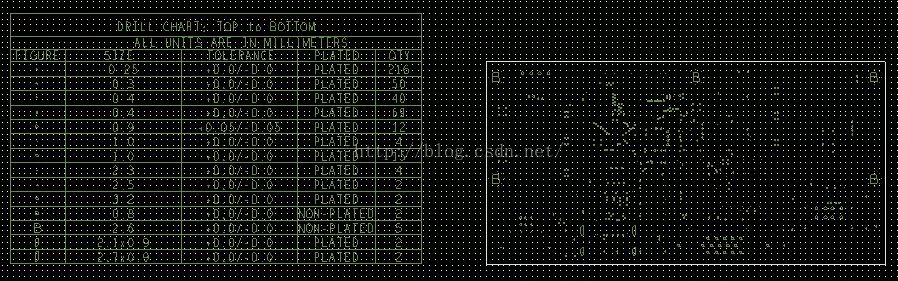

2.7.3 生成钻孔表和钻孔图

1)选择 Display|Color|Visibility命令,弹出 Color and Visibility窗口。

2)在Global Visibility选择 off,清除所有的显示。在Board Geometry选项组中 选择 outline复选框,打开电路板边框。

3)在Manufacturing选项组中 选择Nelegend-1-4复选框,并设置颜色。

4)选择Manufacture |NC | NC Legend命令,弹出Drill Legend窗口。只需要选择 Legends复选框中Layer pair按钮,其他保持默认。

具体如下图2.7.3

图2.7.3

5)单击ok按键,生成钻孔表并附在光标上。在电路板外框内 自动生成钻孔图,同时显示钻孔表。详见下图2.7.4。

图2.7.4 生成钻孔图和钻孔表

2.8生成Atwork光绘文件

为什么使用Gerber文件?

很多PCB厂家都没有装Allegro软件,所以你不能直接发.brd文件。(很多PCB小厂连ProtelDXP也没有,只支持Protel99)

什么是Gerber文件

Gerber文件是所有电路设计软件都可以产生的文件,在电子组装行业又称为模版文件(stencil data),在PCB制造业又称为光绘文件。可以说Gerber文件是电子组装业中最通用最广泛的文件格式。

Gerber文件是EIA的标准格式,分RS274-D和RS274-X两种,其中RS274-X是RS274-D的扩展文件。生产制造部门在条件许可的情况下,应当尽可能要求用户或设计部门提供RS274-X的Gerber文件,这样有利于各工序的生产准备。

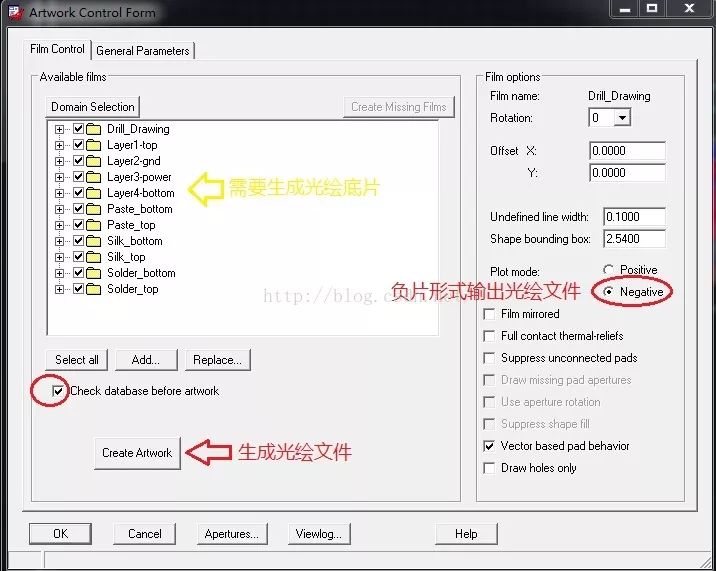

生成的光绘文件应包括:所有电气层(TOP、BOTTOM、GND、POWER)、阻焊层(Soldmask )、加焊层(Pastemask)、丝印层(Silk)、钻表(Drill)和自己定义内容。下面以四层板为例说明:

电气层:

Layer1-top

VIA CLASS/ TOP (过孔类)

PIN/ TOP (引脚)

ETCH/ TOP(电气层)

Layer2-gnd

VIA CLASS/ GND

PIN/ GND

ETCH/ GND

Layer3-power

VIA CLASS/ POWER

PIN/ POWER

ETCH/ POWER

Layer4-bottem

VIA CLASS/ BOTTEM

PIN/ BOTTEM

ETCH/ BOTTEM

加焊层:

Paste-bottom

VIA CLASS/ PASTEMASK_BOTTOM (过孔类加焊层)

PIN/ PASTEMASK_BOTTOM(引脚加焊层)

PACKAGE GEOMETRY/ PASTEMASK_BOTTOM (封装)

Paste-top

VIA CLASS/ PASTEMASK_TOP

PIN/ PASTEMASK_TOP

PACKAGE GEOMETRY/ PASTEMASK_TOP

阻焊层:

Solder-bottom

VIA CLASS / SOLDERMASK_BOTTOM( 过孔类阻焊层 )

PIN/ SOLDERMASK_BOTTOM( 引脚阻焊层)

PACKAGE GEOMETRY/ SOLDERMASK_BOTTOM (封装)

BOARD GEOMETRY/ SOLDERMASK_BOTTOM (板子阻焊层)

Solder-top

VIA CLASS / SOLDERMASK_TOP

PIN/ SOLDERMASK_TOP

PACKAGE GEOMETRY/ SOLDERMASK_TOP

BOARD GEOMETRY/ SOLDERMASK_TOP

丝印层:

Silk-bottom

REF DES/ SILKCREEN_BOTTOM ( 元件标号REF丝印)

PACK GEOMETRY/ SILKCREEN_BOTTOM( 元件封装丝印)

BOARD GEOMETRY/ SILKCREEN_BOTTOM(板子上丝印)

Silk-top

REF DES/ SILKCREEN_TOP

PACK GEOMETRY/ SILKCREEN_TOP

BOARD GEOMETRY/ SILKCREEN_TOP

钻孔表和自己定义内容:

Drill_Drawing

MANUFACTURING / NCLEGEND1-4 (钻孔表)

DRAWING FORMAT/ OUTLINE ( 绘制A3尺寸的外框)

DRAWING FORMAT/ TITLE_BLOCK (自己定义的表格外框 )

DRAWING FORMAT/ TITLE_DATA( 自己定义的表格数据 )

DRAWING FORMAT/ FABRICAION (加工文件说明)

BOARD GEOMETRY/ OUTLINE ( PCB板子外框 )

BOARD GEOMETRY/ DIMENSION ( 板子标注尺寸 )

2.8.1设置输出

设置输出方法:

1)设置光绘文件输出路径方法:

我们可以通过设定“User Preferences”来指定生成Gerber数据文件的保存目录。

菜单栏“Setup”->”User Preferences…”->”File_management”->”Output_dir”,设定”ads_sdart”项的”Value”内容为指定目录名称,如“gerber”,则在生成gerber数据操作时,会自动在当前pcb文件目录下生成“gerber”文件夹,在该文件夹下保存有所生成的全部gerber文件。

2)选择Manufacture | Artwork命令,弹出Artwork Control Form窗口。

3)设置底片内容方法:以加焊top层 Paste-top为例说明一下。

步骤1:打开Artwork Control窗口,在allegro中选择 Display|Color|Visibility命令,弹出 Color and Visibility窗口

步骤2:在Global Visibility选择 off,清除所有的显示。

步骤3:在Stack-up选项中,选择Pin和Via对应的Pastemask_Top复选框;然后在Package Gemetry选项中,选择 Pastemask_Top复选框。详见下图

步骤4:单击Apply按钮,显示选择3个 Subclass

步骤5:单击OK按钮,关闭 Color and Visibility窗口

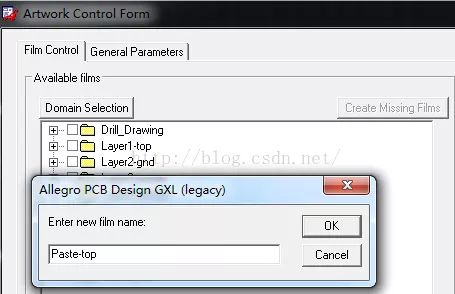

步骤6:在Artwork Control Form窗口,右击Available Films列表中TOP,选择快捷菜单的Add选项,弹出Allegro PCB Design GXL对话框。

步骤7:输入底片名称Paste-top,如下图

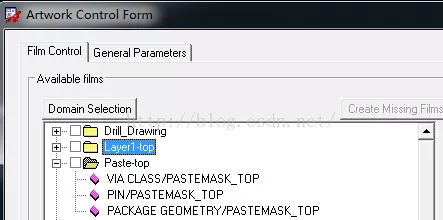

步骤7:单击OK按钮,添加底片Paste-top到Available Films列表中。通过点击+,查询Paste-top中内容。详见下图

注:其他底片内容参考paste-top设置方法 设置,全部设置好了进入下一步。

4) 输出光绘文件前,先按照下图 9.1.1和图9.1.2设置参数。全部设置完,选择“ Creat Artwork”命令,生成光绘文件。

图9.1.1 General Parameters 通用参数设置

图9.1.2 Film Control 底片设置

2.8.2 查看gerber是否正确

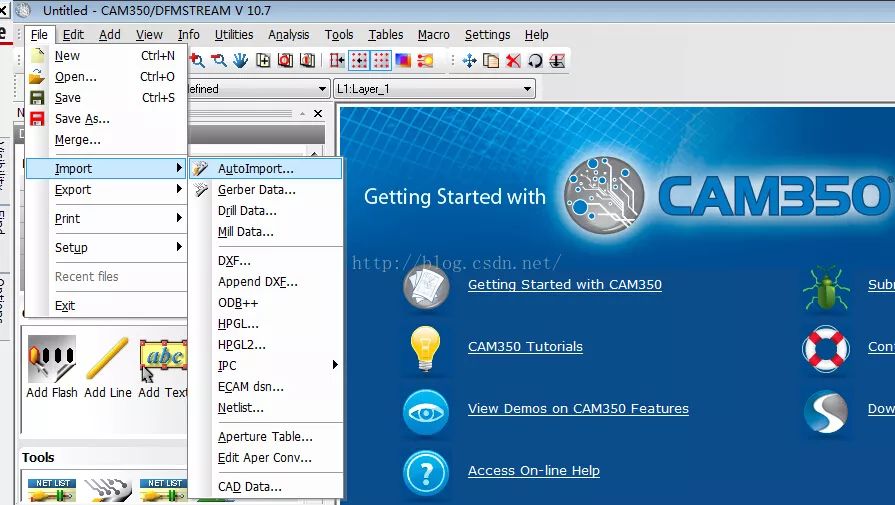

使用CAM350软件查看 光绘gerber文件是否正确。具体操作如下:

第一步:导入需要查看的gerber文件,按照如下操作,选择gerber文件路劲,自动导入。

注意:导入CAM350时单位需 生成gerber文件单位一致。例如:上面生成gerber的单位是公制,则导入CAM350也必须是公制,不然显示异常。

第二步:设置各层颜色。一般只显示 top bottom GND POWER silk丝印层 ,其他根据需要显示。通过查看gerber输出文件是否和 按设计输出PCB文件。

﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌﹌

免责声明:内容来自求知_swat的博客,版权归原作者所有,如涉及作品版权问题,请及时与我们联系,谢谢!

更多干货请点击文末阅读原文

电子发烧友热文推荐

7、55页PPT!很火的MOS管电路工作原理及详解,没有之一!

电子发烧友拆解及DIY推荐

1、大神教你DIY | 如何用一块FPGA开发板制作音乐盒?!

3、四旋翼 DIY高大上!用STM32单片机搞定四旋翼无人机飞控

5、史上最具创意鬼才10大DIY详细集锦,你赶紧看看吧!(收藏版)

电子发烧友学院精选

2、【学院推荐】LabVIEW与PLC如何进行Modbus通信?

4、【学院推荐】LabVIEW编程实例:手把手教你按键监视小软件的实现

5、【学院推荐】PCB工程师不得不看:超级实用AD常用快捷键总结

电子发烧友活动推荐

1、关于ESD原理及防护,这篇文章太专业了!点赞!(征文)

3、超强的四轴无人机飞控源代码,支持STM32所有系列(附项目资料)

4、11个电源设计小技巧,看完提高一半的工作效率!(附资料下载)

5、从菜鸟到高手,学习arm32位单片机的必经之路,给大家分享个人经验!

7、学好LLC开关电源设计,你必须要弄懂的原理知识(文末送资料大礼包)

电子发烧友电路精选

2、20个超经典模拟电路,工程师你知道几个?(收藏:附答案下载)

7、太牛了!电路图符号超强科普,不懂物理也能轻松看懂电路图!(推荐收藏)

电子发烧友资料精选

2、STM32大神笔记,超详细单片机学习汇总资料(干货分享)

3、工程师快速提升技能就看这份资料——固态继电器(SSR)使用指南

6、测量电子电路设计资料大全(电路图集+设计方案+制作流程)

最具有学习价值的电子发烧友社群邀请你加入

添加发烧友小助手

加入“发烧友微信群”交流,

THE END

1、加 Lwangzi312为好友,进入电子行业交流大群

嵌入式软件|可编程逻辑|C语言|linux|单片机|LabVIEW|微机原理|RF/无线|PCB设计|IC设计|电源设计|模拟技术|机器人|测试测量|Java|AR/VR|前端开发|大数据|python|STM32|FPGA|四轴算法|BLDC

2、加 Lwangzi312为好友,进入电子行业城市交流群

深圳39591|北京26276|上海24794|广州15554|西安11854|成都10678|杭州10600|苏州10141|南京9735|武汉9204|东莞7960|天津6610|重庆6319|合肥5096|长沙4832|青岛4427|郑州4425|佛山4176|宁波3774|无锡3617|厦门3569|惠州2893

-

tigershark00

2019-06-27

0 回复 举报收藏了! 收起回复

tigershark00

2019-06-27

0 回复 举报收藏了! 收起回复

- 相关推荐

- 热点推荐

- Cadence

-

cadence15.2PCB封装设计小结2010-04-05 916

-

cadence15.2PCB封装设计自我小结2011-07-05 4191

-

Cadence之OrCAD Capture CIS原理图工具使用小结2014-02-19 18141

-

北京科技大学——Allegro绘制PCB流程及规范2015-01-23 22403

-

Cadence Allegro平台先进的约束驱动PCB流程和布线能力2018-11-23 2366

-

使用Cadence Allegro绘制DragonFly四轴飞行器2021-11-25 2003

-

Cadence仿真流程2008-07-12 1579

-

Cadence PCB仿真流程2011-05-26 1593

-

Cadence 仿真流程2015-12-08 921

-

Cadence如何建立PCB?Cadence建立PCB步骤详解2018-02-07 28702

-

Cadence PCB封装制作流程2019-11-02 10933

-

Cadence电路设计流程2021-11-06 660

-

Cadence每日一学_10 | 使用OrCAD绘制STM32最小系统原理图完整流程2021-11-17 1816

-

基于AD绘制PCB的详细过程2021-12-07 3099

-

Cadence技巧个人总结2022-12-02 817

全部0条评论

快来发表一下你的评论吧 !