技术 | 复杂FPGA高效设计及优化方法

电子说

1.4w人已加入

描述

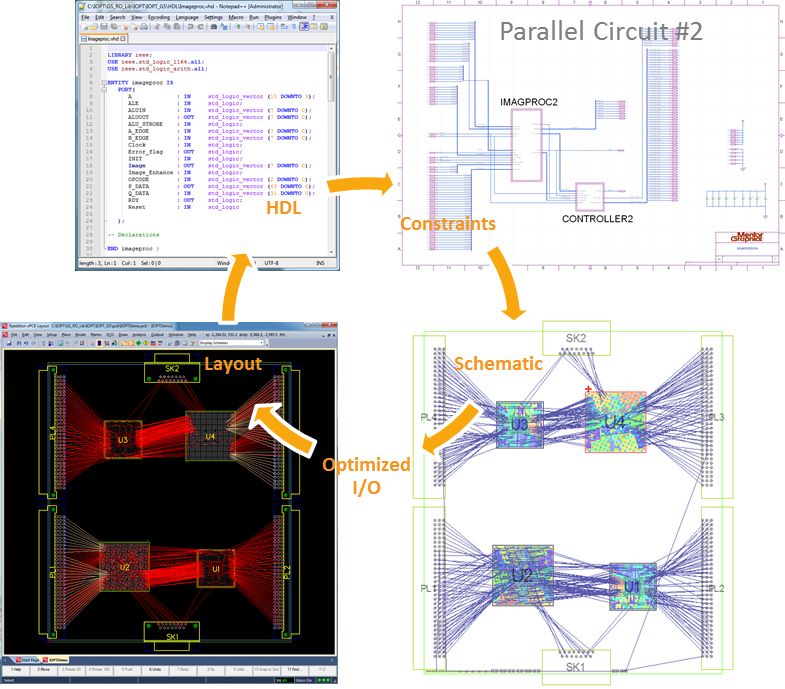

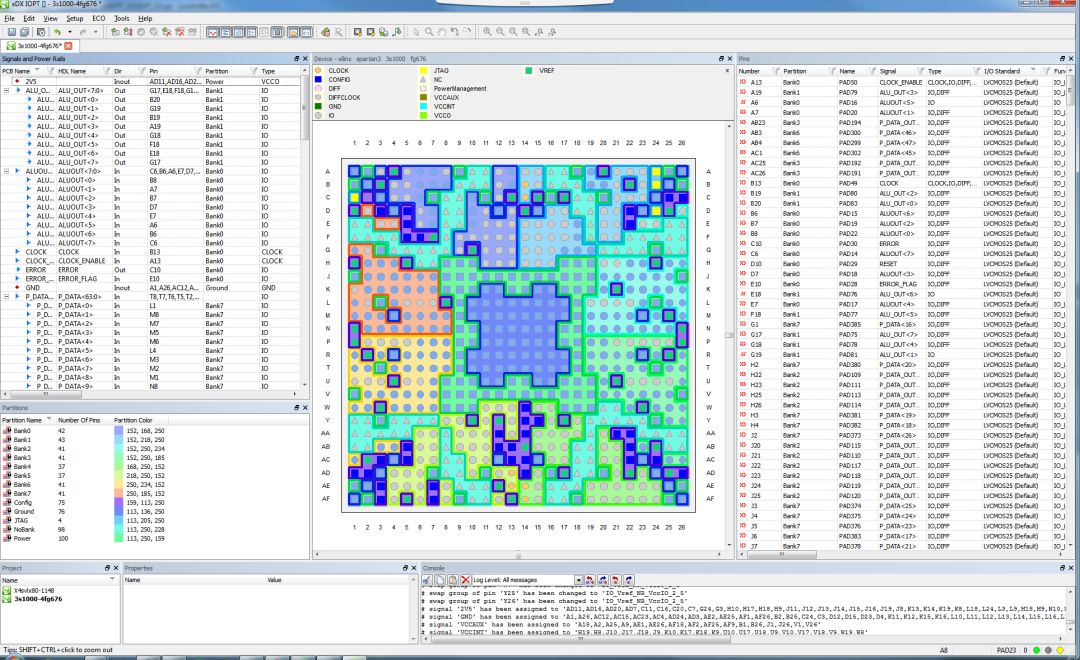

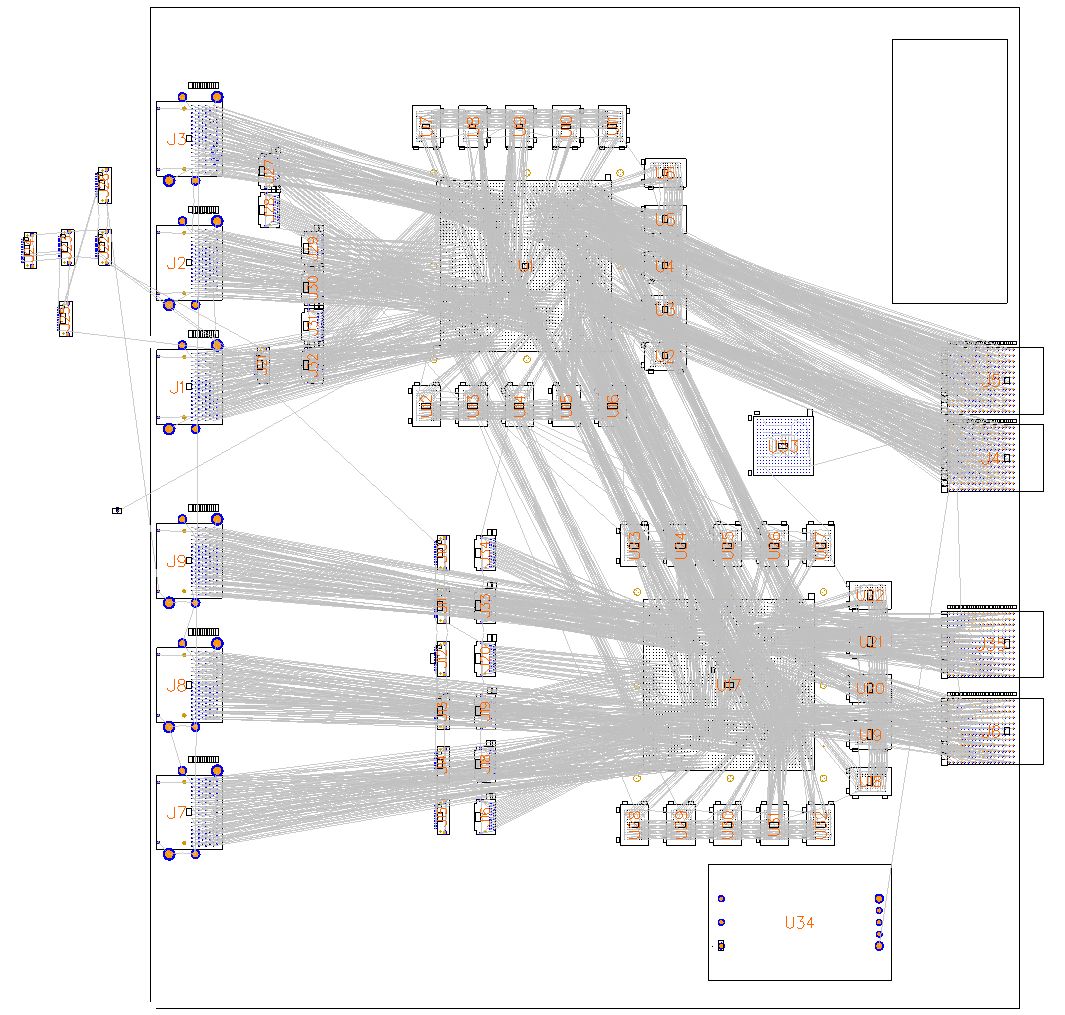

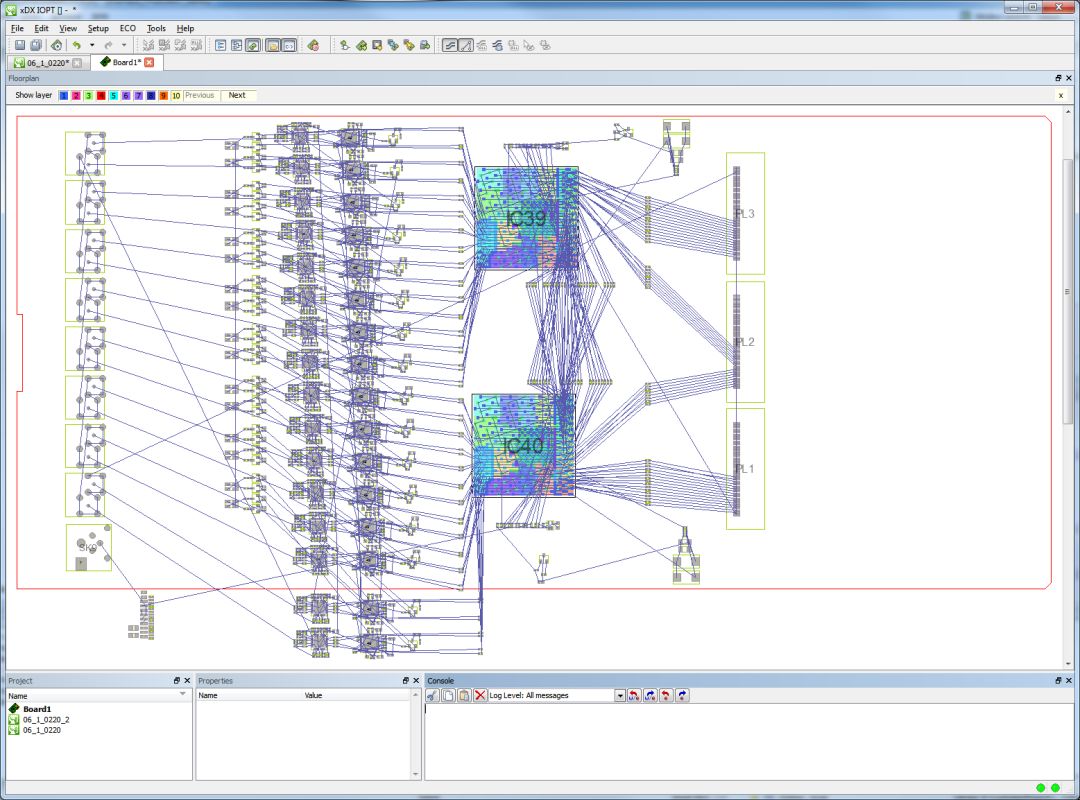

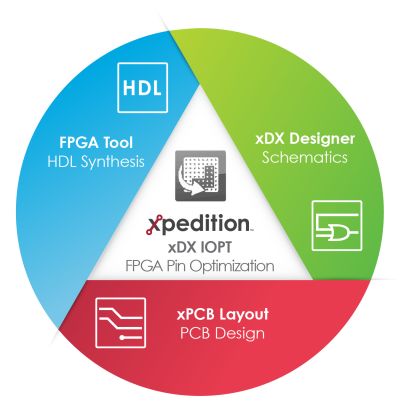

随着电子产品的集成性及复杂度呈指数型增长,加上越来越苛刻的研发周期要求,给各种设计公司提出了难题。这其中FPGA的设计挑战尤为突出。不断增加的管脚数量,同一PCB上的多颗FPGA之间互连等等,面对这些挑战如果还依照以往的手动式设计流程,势必会在激烈的市场竞争中失去优势!Mentor公司针对这种实际应用情况,提出了集成式管脚优化方案,根据信号连接关系及器件位置摆放信息,自动实现IO管脚优化,在保证产品质量的前提下,高效完成FPGA设计及优化工作,在最短的时间内使产品顺利上市!

4大技术优势:

| 1 |

缩减设计成本: 减少过孔数量 节省PCB叠层数量 减少生产制造迭代次数 |

| 2 |

缩短设计周期: 减少设计迭代次数 提升FPGA布线效率 快速优化IO管脚,自动生成器件symbol |

| 3 |

减少设计失误: 杜绝器件symbol设计失误 避免手动更换IO管脚而造成的失误 |

| 4 |

提高产品质量: 减少布线长度,提升信号质量 |

01

器件创建

02

网络互连

03

网络飞线优化

选定网络优化

选定FPGA网络优化

所有网络优化

04

优化后应用

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA工程师是如何实现复杂系统设计的2022-07-22 1087

-

数字IC/FPGA设计中的时序优化方法2025-12-09 3509

-

优化 FPGA HLS 设计2024-08-16 1114

-

高级FPGA设计 结构、实现和优化【书籍教材】2012-03-01 36238

-

FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化...2012-08-11 10193

-

FPGA的时序优化高级研修班2013-03-27 4981

-

FPGA技术的学习方法2017-01-11 89390

-

FPGA-PCB优化技术降低制造成本2018-09-20 1981

-

FPGA-PCB优化技术的意义2019-10-09 11958

-

FPGA设计应用及优化策略有哪些?2021-04-15 1841

-

海底复杂环境下机器人摆脱障碍物路径优化方法研究2017-01-03 801

-

利用FPGA工具设置优化FPGA HLS设计2018-12-16 1977

-

复杂FPGA高效设计及优化方法2019-06-24 3694

-

复杂深孔的高效加工方法!2023-12-10 2255

-

一种简单高效配置FPGA的方法2024-10-24 2758

全部0条评论

快来发表一下你的评论吧 !