关于基于多CPU 架构伺服驱动控制器的性能分析

描述

论述伺服驱动控制器的实现方法,通过对ARM+FPGA+DSP架构的多CPU控制器的具体分析将其原理和优势展现出来;这种架构控制器系统分工明确,提高了算法的实时性;提高了控制器对外接口EtherCAT的实时性;提高了系统的稳定性。这种架构方案在天津电气科学研究院有限公司的伺服驱动器产品中进行了实验,现场的应用取得了良好的效果,体现出这种技术的现实意义。

1.引言

伺服驱动器是用来控制伺服电机的一种控制器,一般是通过位置、速度和力矩三种方式对电机进行控制,实现高精度的系统定位。

目前,伺服控制器CPU的架构主要有:

1、单CPU架构ARM(AcornRISCMachine)控制器;

2、单CPU架构DSP(DigitalSignalProcess)控制器;

3、ARM+FPGA+DSP架构的多CPU控制器。

方法3是目前最先进的架构,前两种方法都有局限性。方法1和方法2这种单CPU架构的控制器,一个CPU集算法、采集控制、通讯、显示功能于一体,当算法复杂度和实时性要求高时往往会顾此失彼。而方法3的架构中各个CPU的分工明确,ARM负责通信和显示功能,DSP负责算法运算,FPGA负责采集和控制。方法3的技术瓶颈是满足伺服控制器的实时性要求需要几个CPU之间的高速数据通信,因此,如果能够找到一个高速的通信方式完全可以发挥各个CPU的特性,就像一个多核CPU在工作一样。

本研究基于ARM+FPGA+DSP架构,采用并口通信的方法用于几个CPU之间的内部高速通信;此外伺服驱动器作为伺服系统的一部分还需要和主控器和编码器进行高速通信,来满足整个伺服系统的实时性要求,本架构采用EtherCAT和高速485接口用于控制器和其他设备进行高速通信,描述了系统的原理架构和软件设计架构。

2.多CPU架构控制器原理分析

01

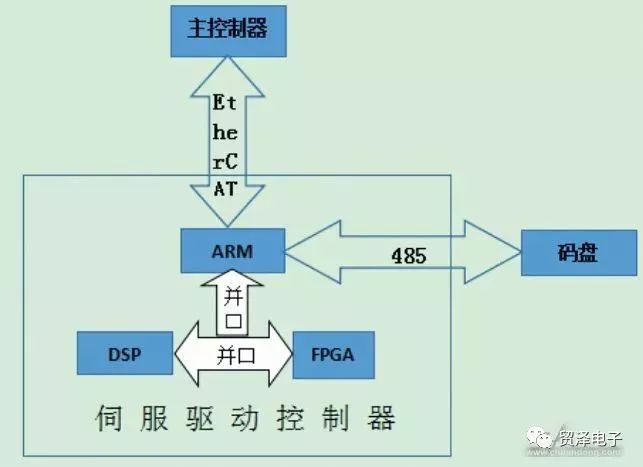

此架构的控制器中ARM负责通信和显示功能,DSP负责算法运算,FPGA负责采集和控制,如图1所示。FPGA采集相电压、相电流等物理量通过并口传给DSP;ARM通过EtherCAT接收主控制器命令,通过高速485采集码盘的速度和位置等信息,通过并口传给FPGA中转下再传到DSP;DSP中执行伺服控制的算法,利用FPGA和ARM中采集的数据进行计算,把计算结果再通过并口传给FPGA和ARM,由FPGA和ARM进行相关的控制操作。

图1 多 CPU 架构控制器结构图

2

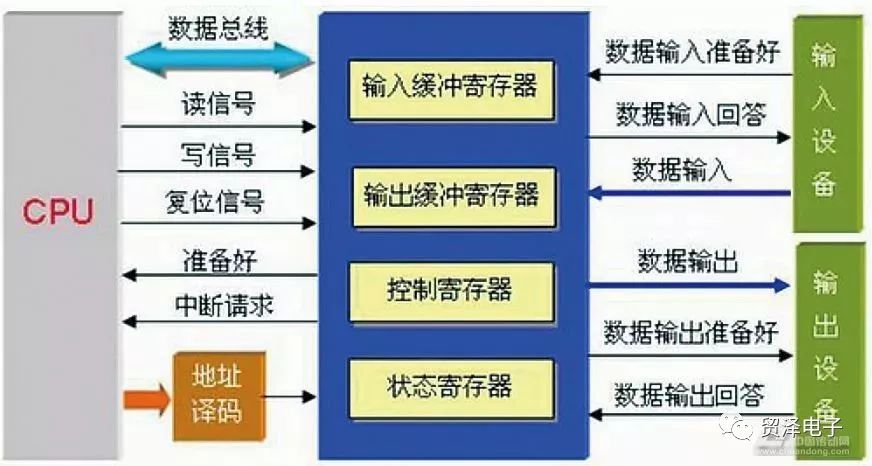

此架构控制器中几个CPU之间的双口RAM通信:用双口RAM中各位数据都是并行传送的,它通常是以字节(8位)的整数倍为单位进行数据传输,能完成数据的输入和输出。用双口RAM通信的原理如2所示。用双口RAM通信具有各数据位同时传输,传输速度快、效率高的特点,多用在实时、快速的场合。

图2 用双口RAM通信原理图

3

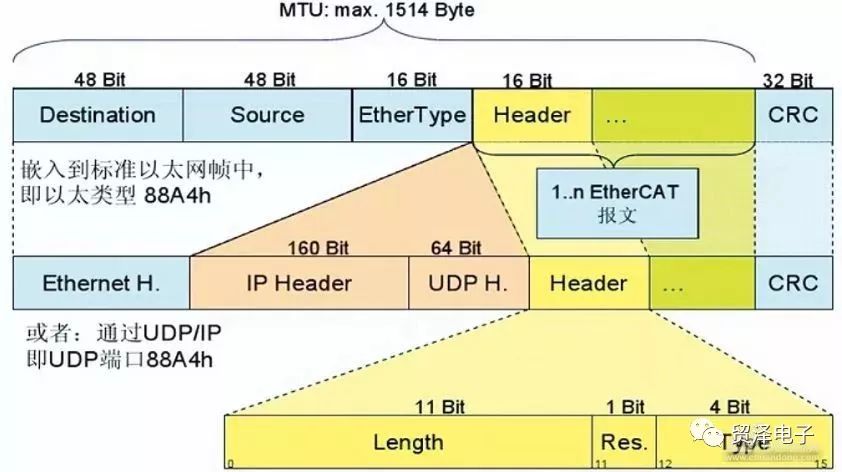

此架构控制器的对外接口有EtherCAT和高速485。码盘的接口一般采用485接口,所以本控制器也采用485的接口,用DMA来实现;伺服控制器与主控制之间的接口有EtherCAT和PROFINET等协议,本控制器采用应用比较广的EtherCAT接口。实时以太网EtherCAT是由倍福开发的一种工业以太网技术。它以高速率、高有效数据利用率、完全符合以太网标准、刷新周期短、同步性能好等优势,在伺服通讯领域中得到越来越多的应用。其原理如图3所示。

图3 EtherCAT报文

3.多CPU架构控制器硬件设计

3.1控制器ARM的设计

主控制器ARM通过STM32F407芯片完成上节介绍的与FPGA的并口通信、EtherCAT通信、485通信。STM32F407属于高端的32位ARM微控制器,该系列芯片是意法半导体(ST)公司出品,其内核是Cortex-M4。本次设计充分利用其资源,实现了并口通信、therCAT通信、485通信。

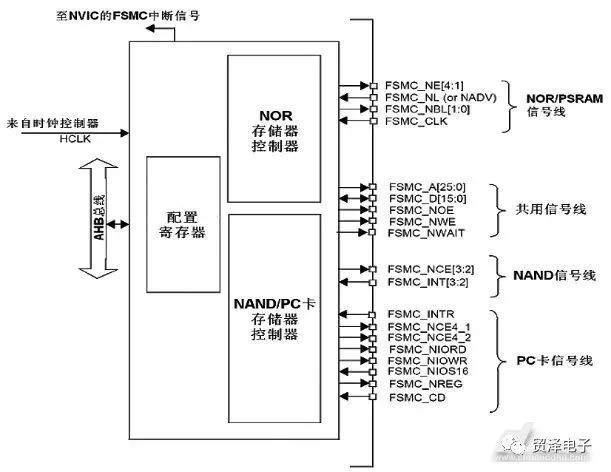

图4 FSMC框图

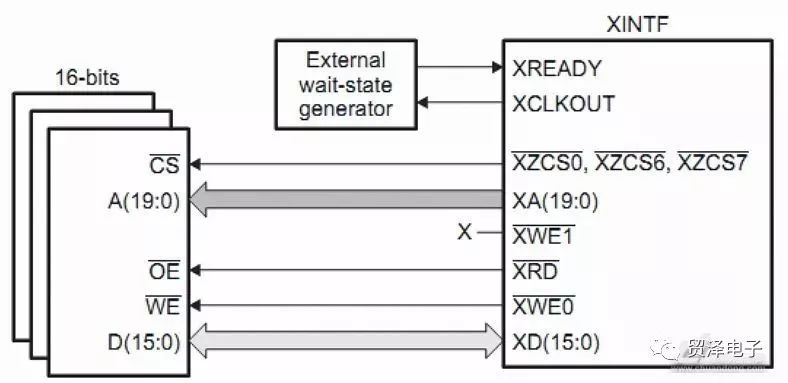

并口通信:STM32F407具有FSMC功能,灵活的静态存储器控制器(FSMC)是内置大容量的外部存储器控制器,使用这个控制器,STM32可以与FPGA或者存储器进行并口通信。FSMC产生所有驱动这些存储器(把FPGA当做存储器来操作)的信号时序:16个数据线和16个地址线,原理如图4所示。

图5 数据总线XINTF连接框图

EtherCAT通信和485通信:EtherCAT通信通过芯片ET1100来实现,ET1100是一款强大的EtherCAT从站控制器ESC专用芯片,ET1100与ARM的接口采用SPI的方式;485通信速度为2.5Mbps,采用DMA的方式来实现,DMA的具体实现方法在下章软件设计中详述。

图6读操作时序

3.2控制器FPGA和DSP的并口通信设计

FPGA采用Altera的CycloneIV系列FPGA,具有低成本、低功耗的特点,高达532个用户I/O,支持高达200MHz的DDR2SDRAM接口;DSP采用TMS320C28346,通过XINTF连接FPGA,实现双向并口通信。DSP的输入和输出采用中断控制,当FPGA准备好数据后,向DSP发送中断,DSP响应中断后读取相应地址的数据并向另外一段地址写入数据,FPGA等待60μs开始读数据。这样就能够完成两个芯片的并行通信。TMS320C28346型DSP芯片有16位XINTF数据总线,做为系统外部接口,它可以与各种外部存储器或者CPU实现无缝连接,如图5所示。在此系统中,将它与FPGA的16个用户可定义I/O管脚相连,用于实现16位并行数据的通信。TMS320C28346芯片可编程通用输入/输出引脚,任选一个和FPGA的用户I/O管脚相连,作为DSP的读写中断。

4.多CPU架构控制器软件设计

4.1控制器ARM的软件设计

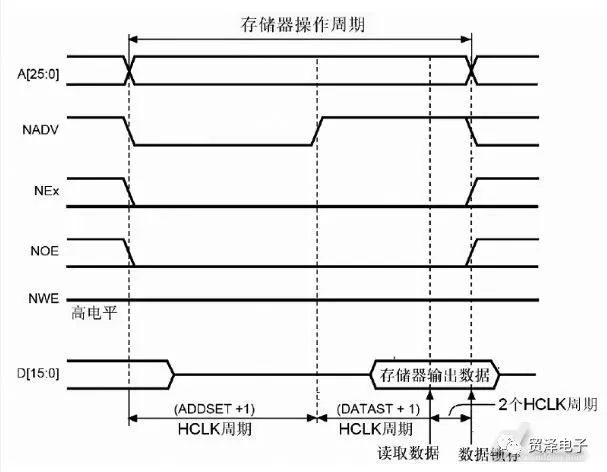

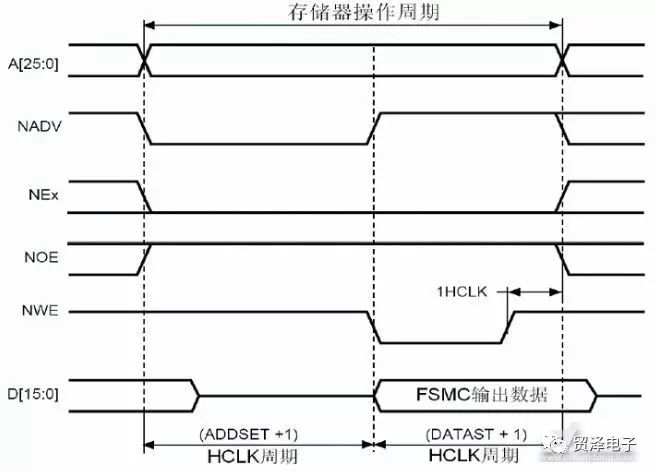

控制器中ARM与FPGA的并口通信用FSMC来实现,采用非总线复用的异步NOR闪存的方式来驱动,读时序如图6所示,写时序如图7所示。

图7 写操作时序

并口通信的地址选择使用了FSMC的BANK1的子板块2,具体程序代码如下:

p.FSMC_AccessMode=FSMC_AccessMode_A;

FSMC_NORSRAMInitStructure.FSMC_Bank=FSMC_Bank1_NORSRAM2;

FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM2,ENABLE);

ARM与FPGA通信触发由外部中断来触发,当FPGA准备好数据后给ARM一个中断,中断周期为120μs,其中前60μs用于ARM从并口地址读取数据并且把要传给FPGA的数据写入相应地址,后60μs用于FPGA从并口地址读取数据,程序代码如下:

pBuf=(s16*)EXT_SRAM_ADDR+31;

for(i=31;i<91;i++)//read

{FPGA_TO_ARM[i]=*pBuf++;}

pBuf=(s16*)EXT_SRAM_ADDR+41;

for(i=41;i<61;i++)//write

{*pBuf++=(FPGA_TO_ARM[i]+1);}

ARM与码盘通信通过485来实现,通信速度为2.5Mbps,由于速度快采用一般的中断方式很难满足需求,本系统采用DMA来实现,程序代码如下:

DMA_InitStructure.DMA_PeripheralBaseAddr=(uint32_t)(&(USART3->DR));//串口3接收DMA

DMA_InitStructure.DMA_Memory0BaseAddr=(uint32_t)UART3_DMA_RxBuffer;

DMA_InitStructure.DMA_PeripheralBaseAddr=(uint32_t)(&(USART3->DR));//串口3发送DMA

DMA_InitStructure.DMA_Memory0BaseAddr=(uint32_t)UART3_DMA_TxBuffer;

4.2控制器FPGA的软件设计

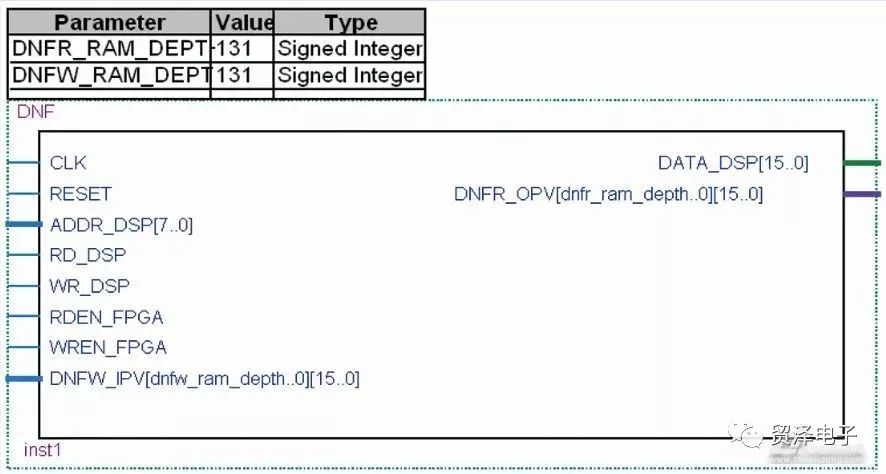

FPGA与DSP并行总线通讯模块用于FPGA与DSP之间的并行总线数据交换,其中包含两段独立的地址空间,一个空间用于DSP读FPGA内部数据通道,另一个空间用于DSP向FPGA写数据通道。程序使用ALTERA提供的双口RAM的IP核。程序模块图如图8所示。

图8 FPGA程序模块图

FPGA与DSP并行总线通讯模块主时钟CLK的频率应是DSP总线读写频率的4倍以上,一般选取120M,这个时钟由FPGA内部的PLL锁相环生成。由于DSP的地址总线一般为16位以上,ADDR_DSP连接DSP地址总线的低位。RD_DSP连接DSP读使能,WR_DSP连接DSP写使能,如果有片选信号,DSP读写使能信号需要与片选信号取或后再与WR_DSP和RD_DSP连接。

4.3控制器DSP的软件设计

DSP28346芯片通过外部接口(XINTF)来读写外扩存储单元,本系统中即为FPGA的双口RAM空间。DSP28346的XINTF是一个非复用的异步总线。在配置XINTF时,应该检测内部XTIMCLK所需要的与SYSCLKOUT有关的比例。通过写XINTFCNF2寄存器的XTIMCLK位,可以将TIMCLK配置成与SYSCLKOUT相等或者等于SYSCLKOUT/2。XINTF的所有访问从XCLKOUT的上升沿开始,而外部逻辑受到XCLKOUT时钟的控制。通过写XINTFCNF2寄存器的CLKMODE位,可将XCLKOUT配置成与内部XINTF时钟XTIMCLK成比例的频率。程序代码如下:

XintfRegs.XINTCNF2.bit.XTIMCLK=0;

XintfRegs.XINTCNF2.bit.WRBUFF=3;

XintfRegs.XINTCNF2.bit.CLKOFF=0;

XintfRegs.XINTCNF2.bit.CLKMODE=0;

XintfRegs.XINTCNF2.bit.BY4CLKMODE=1;

XintfRegs.XTIMING6.bit.XWRLEAD=3;

XintfRegs.XTIMING6.bit.XWRACTIVE=5;

XintfRegs.XTIMING6.bit.XWRTRAIL=2;

XintfRegs.XTIMING6.bit.XRDLEAD=3;

XintfRegs.XTIMING6.bit.XRDACTIVE=5;

XintfRegs.XTIMING6.bit.XRDTRAIL=2;

XintfRegs.XTIMING6.bit.X2TIMING=0;

XintfRegs.XTIMING6.bit.USEREADY=1;

XintfRegs.XTIMING6.bit.READYMODE=1;

5.结论

市面上的伺服驱动器CPU的架构主要有单ARM控制器和单DSP控制器。单ARM控制器方案在通信和控制方面存在优势,但是复杂算法在实现的时候往往会因为运算耗时而降低整个系统实时性;单DSP控制器方案中在算法中存下优势,但是在对外通信和控制方面往往会实现起来比较复杂。采用ARM+FPGA+DSP架构的多CPU控制器方案完全解决了上述两种方法的弊端,充分发挥了各个CPU的优势。本文论述的架构在本公司的伺服驱动器产品中进行试验和应用,证明了“ARM+FPGA+DSP架构的多CPU控制器架构”的可行性和技术优势。

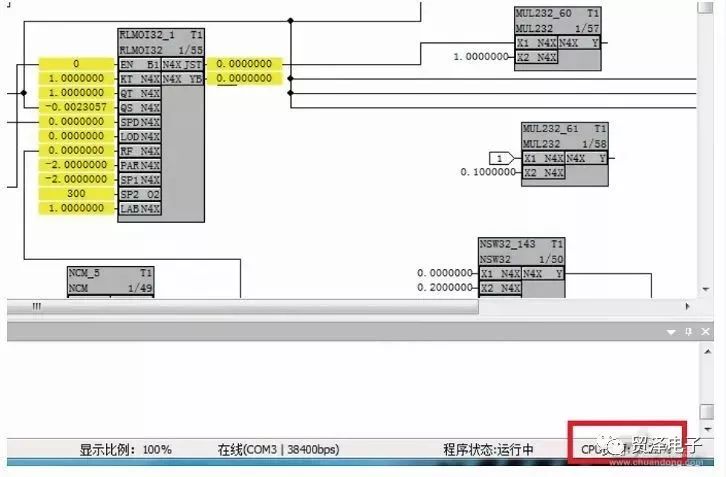

图9 CPU算法在线仿真图

如图9中的红色标记框图所示,整个伺服驱动器系统的CPU使用率在75.22%(A:空跑时优先级最低的计数器个数;B满算法运行时优先级最低计数器的个数;CPU使用率=(A-B)/A*100),此CPU架构达到了控制CPU使用率和提高系统效率的目标。

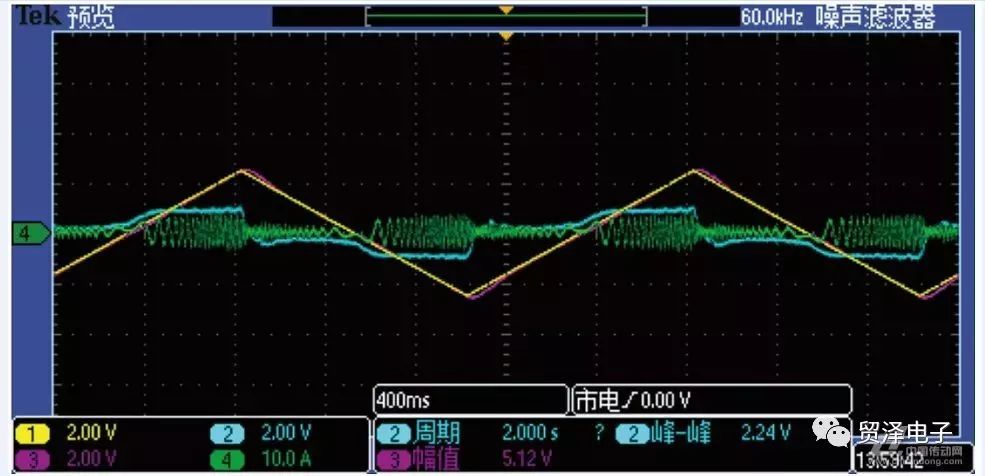

图10

如图10中的离线惯量辨识2s周期(0.5转速)PI不变时跟随情况,通道1是转速给定,通道2是电磁转矩,通道3是实际转速,通道4是实际A相电流。速度采集首先通过ARM的高速485采集码盘数据,并通过并口传给DSP和FPGA,经过算法处理再把数据下发给码盘,整个闭环过程通过并口传输,满足了伺服驱动器的算法实时性要求,此CPU架构达到了提高整个系统实时性的目标。

-

伺服驱动器的控制方式分析2024-11-04 2217

-

伺服驱动器对伺服电机的控制要求2024-06-14 2268

-

伺服控制器的工作原理和基本结构2024-06-13 4640

-

伺服控制器编码器反馈数值为负数怎么回事2024-06-05 6123

-

伺服控制器是什么_伺服控制器用途2023-03-12 7614

-

多CPU架构控制器软件设计2022-12-23 1314

-

论述伺服驱动控制器的实现方法2022-09-20 3278

-

高价回收 CPU模块 西门子伺服 驱动器 收购plc控制器2020-10-10 1170

-

关于伺服电机、驱动器、控制器的一些原理详解2018-07-04 44853

-

Machinekit的多轴控制器软件架构2018-03-12 2246

-

伺服定位控制在PLC中实现和在伺服控制器中实现解答2018-02-01 11993

-

基于多CPU架构伺服驱动控制器的研究2018-01-29 3416

全部0条评论

快来发表一下你的评论吧 !