关于可编程逻辑推动基于MCU的设计的分析和应用

描述

现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)都属于大型可编程逻辑器件,十年前它们发明伊始是为了充当胶合逻辑以及ASIC原型器件,但自出现后,它们的功能扩展非常迅速。嵌入式加速器和微处理器应用曾经一度仅使用DSP和ASSP,但FPGA以及CPLD后来也成为了强有力的候选。一旦设计师了解FPGA和CPLD架构的基础知识,就可以提升许多设计的性能、效率并缩短设计周期。

在演化到目前最新形态的FPGA和CPLD之前,可编程逻辑已经有很长的发展历史。这两种技术之间的体系结构差别可由名称识别出来。FPGA结构非常像ASIC门阵列,事实上,它最初用于ASIC原型。 CPLD则是一堆可编程逻辑元件的网络,这些元件连接起来可以创建一个更大的系统。

可编程逻辑基础

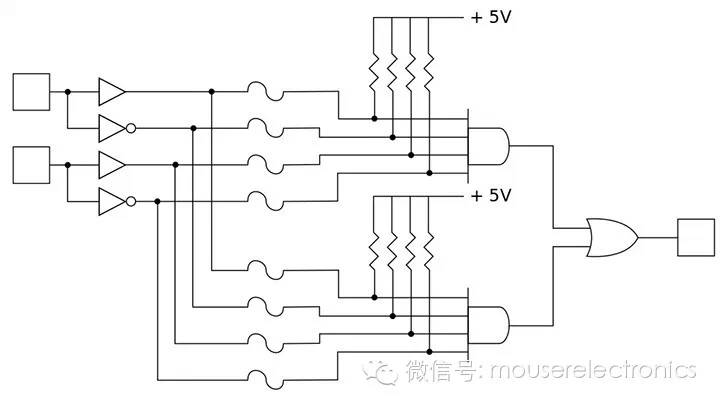

为理解FPGA和CPLD的基础配置思路,可以重新回顾一下可编程阵列逻辑(PAL)的特性。PAL最初具备一个宽泛的可编程与(AND)门平面,可以对输入进入与操作。或(OR)平面是固定的,限制了可以一起进行或操作的项数。也加入了一些基础逻辑单元,比如多路复用器、异或和锁存器,也包括一些时序单元,例如触发器。

这些电路元件的组合帮助设计者实现大量的逻辑功能,包括状态机需要的时钟时序逻辑。PAL速度非常快,可以取代很多上一代设计中的标准逻辑。图1显示了一个基础的PAL,其中的可编程元件(显示为熔丝)将输入信号的真值和互补值同时连接到图中所示的与门。与门,也被称为乘积项,通过或运算,形成乘积项之和的逻辑阵列。

图1:简化的可编程阵列逻辑(PAL)

CPLD和FPGA在PAL和ASIC门阵列之间创造了一种妥善并且非常具有扩展性的媒介。CPLD和PAL速度一样快,但更为复杂。FPGA方法复杂性与门阵列接近但是可编程。

CPLD架构

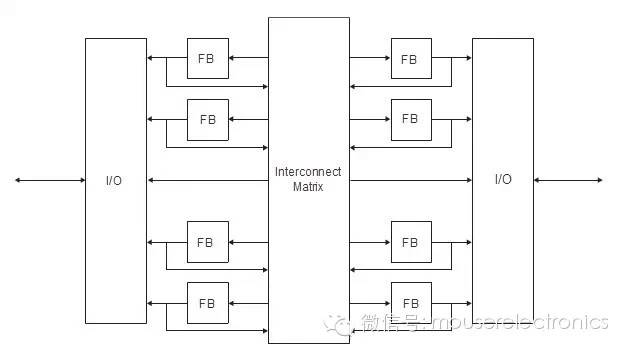

虽然每家CPLD厂商都有其独特实现,但所有CPLD具备一些共有特征,比如都拥有功能块(FB)、输入/输出模块(I / O)以及互连矩阵。 CPLD均通过使用特定制造商工艺对应的元件编程。存储器件可以是EPROM单元、EEPROM单元或Flash EPROM单元。图2显示了一个典型的CPLD架构。

图2:简化的CPLD架构

FPGA架构

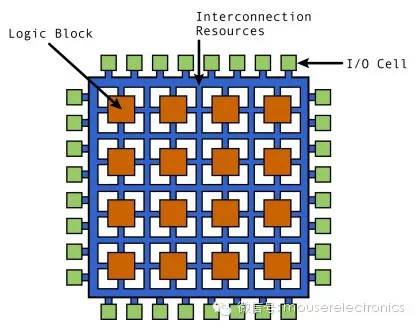

FPGA架构与ASIC类似,但与CPLD差异巨大。一个通用的FPGA架构包括配置逻辑块(CLB)阵列、I / O焊盘和可编程互连,如图3所示。加入了时钟电路以驱动时钟信号到每一个逻辑块。算术逻辑单元、存储单元和译码器也是典型的组件。

图3:基础FPGA架构

FPGA逻辑蕴藏在CLB中,CLB包含了RAM资源,可用于创建组合逻辑功能,这些功能也常称为查找表(LUT)。它还包含了触发器,可用于时序存储元件,还包含了多路复用器,以用于逻辑块内和外部资源之间的逻辑的布线。多路复用器还可用于极性选择以及复位和清零输入选择。

可配置I / O块包含带有三态以及开路输出控制集合功能的一对输入和输出缓冲对。输出的极性通常可编程为高有效或低有效输出,并且输出的压摆率经常也可以被编程为快或慢的上升和下降时间。输入端和输出端通常包含触发器。在输入端使用触发器,这样在到达触发器之前就不会有太多时延,但将增加器件保持时间的要求。在输出端,触发器允许时序信号直接输出到管脚,不会遇受显著延迟问题。

为避免信号延迟带来的不利后果,互联结构最终呈现出层次化结构,在这种结构中长连线(它们也可以被用作总线)连接芯片中物理上远离的多个关键CLB。短连线连接彼此接近的多个独立CLB。类似于CPLD中的开关矩阵,以特殊方式连接多条长连线和短连线。芯片内的可编程开关使能CLB与互连线的连接,以及互连线彼此间的连接,还有互连线与开关矩阵的连接。

利用三态缓冲器将多个CLB连接形成一个长连线,多条长连线就组成了总线。时钟通过长连线分布在整个FPGA中,这样的长连线称为全局时钟线,专门面向低阻抗和快速传播进行了优化。他们连接到时钟缓冲器,以及连接到每个CLB中的时序元件。

-

可编程逻辑(PLD)的市场及优点分析2011-12-05 1648

-

什么是可编程逻辑2009-05-29 3825

-

什么是可编程逻辑控制器?可编程逻辑控制器有哪些特点?2021-07-05 3313

-

可编程逻辑器件设计2006-03-25 1191

-

可编程逻辑基础电子书2010-03-23 729

-

可编程逻辑器件基础及应用实验指导书2010-03-24 798

-

什么是PLD(可编程逻辑器件)2009-06-20 30094

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1178

-

可编程逻辑器件(书皮)2022-07-10 809

-

关于可编程逻辑器件的分析和应用2019-08-28 4441

-

可编程阵列逻辑构造_可编程逻辑器材的运用2020-06-17 2402

-

基于可编程逻辑的SDRAM控制方法设计2021-06-30 1201

-

可编程逻辑控制继电器2022-11-01 1908

-

可编程逻辑器件测试2023-06-06 1330

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4615

全部0条评论

快来发表一下你的评论吧 !